ными входами второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера и первой и второй основными входными шинами, выход второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера подсоединен к третьим и четвертым дополнительным входам второго и третьего элементов И-ИЛИ-НЕ основного трехстабильиого триггера, выход третьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера соединен с пятыми и шестыми дополнительными входами второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера, первые выходы второго и третьего элементов И-ИЛИ-НЕ дополнительного трехстабильного триггера соединены с седьмыми дополнительными входами второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера и с четвертой дополнительной входной шиной, четвертый, пятый и шестой дополнительные входы первого элемента И-ИЛИ-НЕ основного трехстабийьного триггера соединены со вторыми, третьими и четвертыми входами второго и третьего элементов И-ИЛИ НЕ дополнительного трехстабильного триггера и третьей, четвертой и пятой основными входньани шинами, выход второго элемента И-ИЛИ-НЕ основного грехстабильного триггера соединен с четвертым входом второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера, пятый вход второго элемента И-ИЛИ-НЕ которого подключен к выходу первого элемента И-ИЛИ-НЕ эсновного трехстабильного триггера и к пятому входу третьего элемента il-ИЛИ-НЕ дополнительного трехстабильного триггера, выход третьего элемента И-ИЛИ-НЕ основного трехстабильног триггера соединен с шестым входом тргьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера.

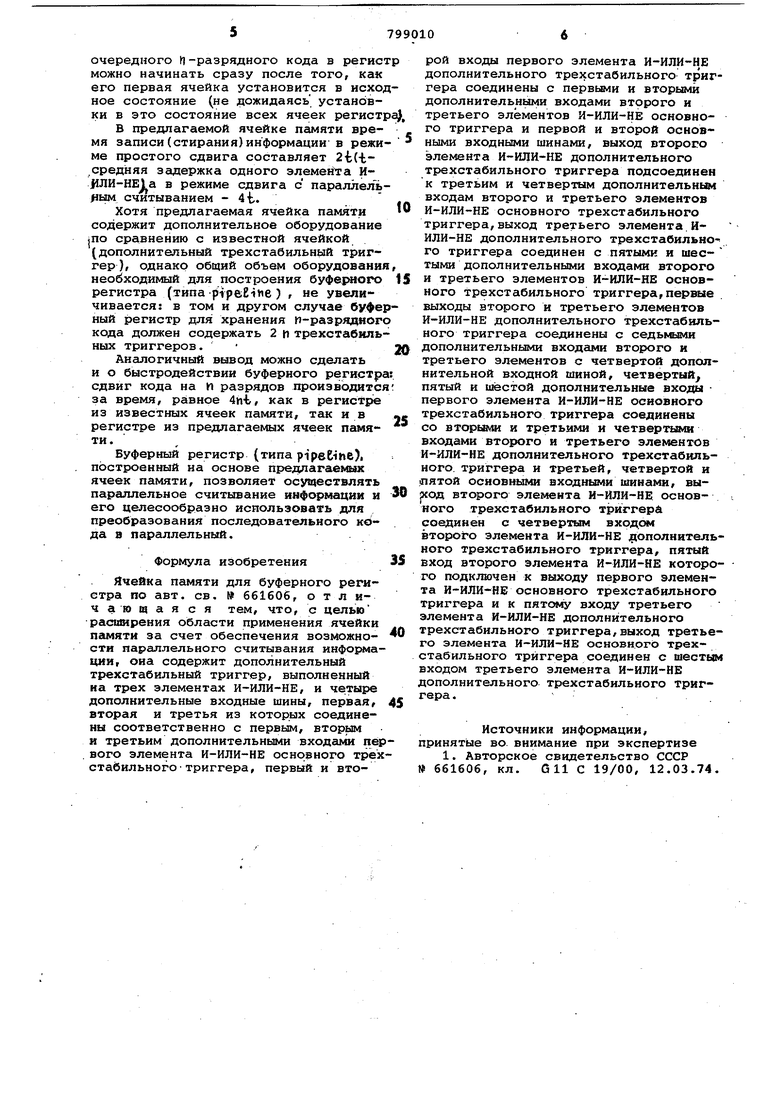

На чертеже представлена функциональная схема предлагаемой ячейки паияти для буферного регистра.

Устройство содержит элементы 1-ИЛИ-НЕ 1-3 основного трехстабильного триггера 4, элементы И-ИЛИ-НЕ -7 дополнительного трехстабильного триггера 8, основные входные шины J-14, дополнительные входные шины 15-18..

Ячейка работает слеДу1Сйдим образом Основной триггер предлагаемой ячеки-памяти имеет три устойчивых соегояния, которые определяются значениями на выходах элементов 1,2,3; 011 - информация в триггере 4 отсутствует, НО - в триггере- 4 записана

п н

I

101 - а триггере 4 записан О.

Аналогичные состояния имеет и дополнительный триггер 8.

Пока в дополнительном триггере 8 отсутствует информация; изменение состояний основного триггера происходит так же, как и в известном устройстве.

Условием записи (стирания) информации в 1-й ячейке, в этом режиме является отсутствие (наличие) информатции в (1+1)-и и наличие (отсутствие) информации в(1-1)-й ячейках соответртвенно. При этом запись (стирание) информации в 1-й ячейке происходит через элементы 2,3(1)Пусть теперь в( ячейке оказался (i+.1)-и разряд сдвигаемого кода, в результате чего в дополнительный триггер 8 (1+1).-й ячейки записалась информация, этот триггер оказался в состоянии 110 или 101. Эти состояния дополнительного триггера 8 (1+1)-й ячейки разрешают перепись информации из (1-1)-й ячейки в 1-ю ячейку через элементы 2 и 3. При этом, очевидно в 1-ю ячейку запишется 1-й разряд , сдвигаемого кодака в (1-1)-й ячейке информ 1ция будет стерта. Условием пе реписи информации из основного триггера 4 1 -и ячейки в ее дополнительный триггер 8 является наличие информации в основном 4 и дополнительном триггерах 8 (j+lj-й ячейки и отсутствие информации в (i-l)-и ячейке. Эти условия являются признаком того, что в 1-ю ячейку записан 1-й разряд сдвигаемого кода.

Таким образом, информация на выходах элементов 6 и 7 -f-й ячейки появляется только после того, как в этой ячейке окажется записанным 1-й разряд сдвигаемого кода, что позволяет осуществить параллельное считывание информации из буферного регистра.Возврат 1-й ячейки памяти буферног регистра в исходное состояние происходит в следующем порядке.

Сначала стирается информация в основном триггере 4 -f-й ячейки (условием этого является отсутствие информации в основном 4 и наличие ее в дополнительном триггере 8 (1-1)-й ячейки соответственно), а затем стирается информация в дополнительном триггере 8 -и ячейки (условием этого является отсутствие информации в основном триггере 4 (i+1 -и ячейки.

Процесс установки ячеек буферного регистра в исходное состояние распространяется последовательно от первой ячейки к п-й, причем как только i-я ячейка .оказывается в исходном состоянии (т.е. отсутствует информация в ее основном 4 и дополнительном триггерах 8), она снова может принимать информацию из (-г-1)-й ячейки. / При этом пока дополнительный триггер 8 1-й ячейки хранит информацию (находится в состоянии 110 или 101), запись информации в ее основной триггер 4 блокируется и поэтому запись очередного Ц-разрядного кода в регист можно начинать сразу после того, как его первая ячейка установится в исход ное состояние (не дожидаясь установки в это состояние всех ячеек регистр В предлагаемой ячейке памяти время записи(стирания)информации в режи ма простого сдвига составляет 2(-iсредняя задержка одного элементе а ИКЛИ-НЕ а в режиме сдвига с параллельtitoA считыванием - 4t. Хотя предлагаемая ячейка памяти содержит дополнительное оборудование шо сравнению с известной ячейкой (дополнительный трехстабильный триггер), однако общий объем оборудования необходимый для построения буфераого регистра (типа pipeEine) , не увеличивается: в том и другом случае буфер ный регистр для хранения п-разрядйого кода должен содержать 2 ц трехстабнльных триггеров. Аналогичный вывод можно сделать и о быстродействии буферного регистра сдвиг кода на ti разрядов производится за время, равное 4мЬ, как в регистре из известных ячеек памяти, так ив регистре из предлагаемых ячеек памя ти. Буферный регистр (типа pipetine). построенный на основе предлагаемых ячеек памяти, позволяет осуществлять параллельное считывание информации и его целесообразно использовать для преобразования последовательного кода в параллельный. Формула изобретения Ячейка памяти для буферного регистра по авт. св. 661606, отличающая ся тем, что, с целью раситрения области применения ячейки памяти за счет обеспечения возможности параллельного считывания информации, она содержит дополнительный трехстабильный триггер, выполненный на трех элементах И-ИЛИ-НЕ, и четыре дополнительные входные шины, первая, вторая и третья из которых соединены соответственно с первым, вторьм и третьим дополнительными входалш пер вого элемента И-ИЛИ-НЕ основного трех стабильного-триггера, первый и второй входы первого элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера соединены с первьв 1и и вторыми дополнительными входами второго и третьего элементов И-ИЛИ-НЕ основного триггера и первой и второй основными входными шинами, выход второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера подсоединен к третьим и четвертым дополнительным входам второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера,выход третьего элемента.ИИЛИ-НЕ дополнительного трехстабильно го триггера соединен с пятыми и шеетыми дополнительными входами второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера,первые выходы второго и третьего элементов И-ИЛИ-НЕ дополнительного трехстабильного триггера соединены с седьмыми дополнительными входами второго и третьего элементов с четвертой дополнительной входной шиной, четвертый пятый и шестой дополнительные входы первого элемента И-ИЛИ-НЕ основного трехстабильного триггера соединены со BTOpbBvm и третьими и четвертыми входами второго и третьего элементов И-ИЛИ-НЕ дополнительного трехстабильного. триггера и третьей, четвертой и 1ПЯТОЙ основными входными шинами, вырсод второго элемента И-ИЛИ-НЕ основного трехстабильного триггера соединен с четвертым входом второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера, пятый вход второго элемента И-ИЛИ-НЕ которого подключен к выходу первого элемента И-ИЛИ-НЕ основного трехстабильного триггера и к пятому входу третьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера,выход третьего элемента И-ИЛИ-НЕ основного трехстабильного триггера соединен с шестьо входом третьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера. Источники информации, принятые во. внимание при экспертизе 1. Авторское свидетельство СССР 661606, кл. G11 С 19/00, 12.03.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для буферного регистра | 1980 |

|

SU928417A2 |

| Ячейка памяти для буферного регистра | 1980 |

|

SU905860A1 |

| Реверсивный буферный регистрСдВигА | 1979 |

|

SU841050A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Устройство для сопряжения основной памяти цифровой вычислительной машины с каналами ввода-вывода | 1977 |

|

SU689438A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-12—Подача