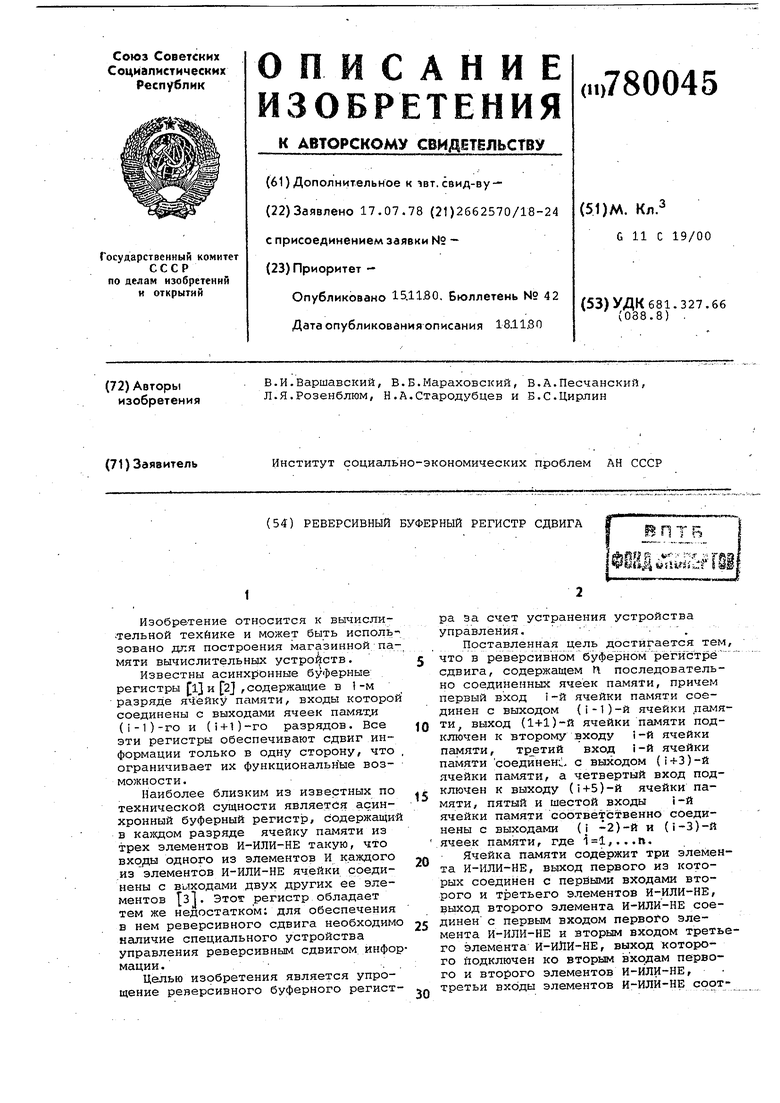

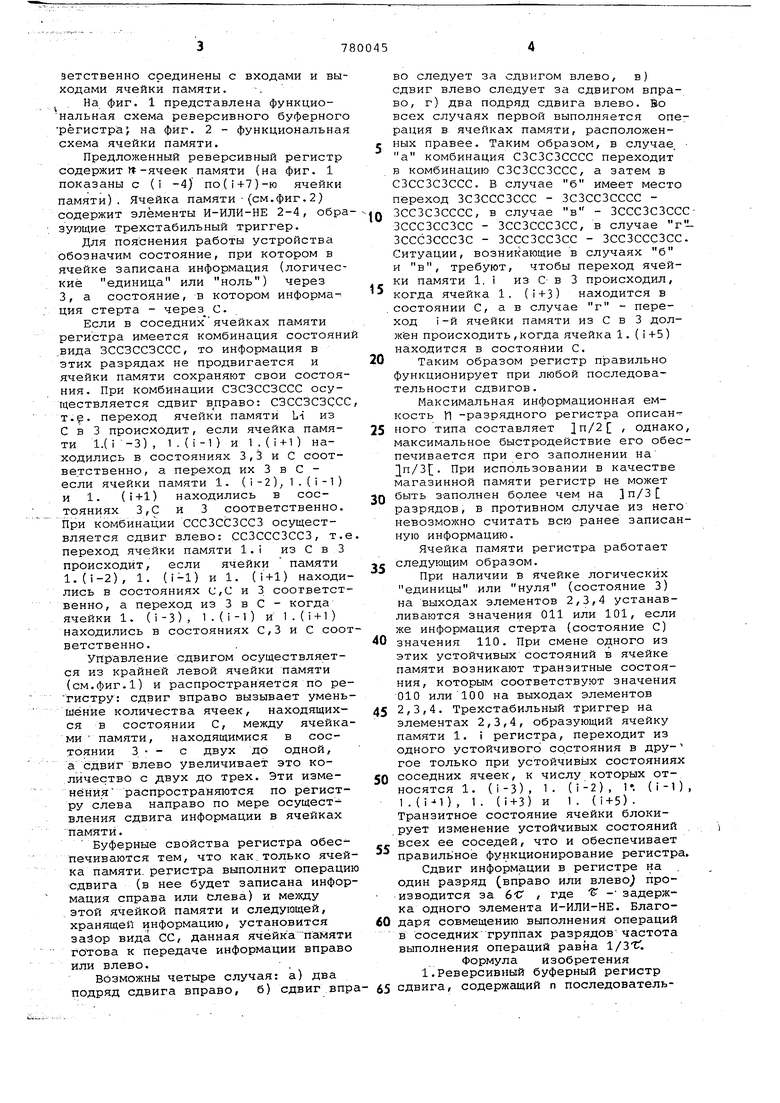

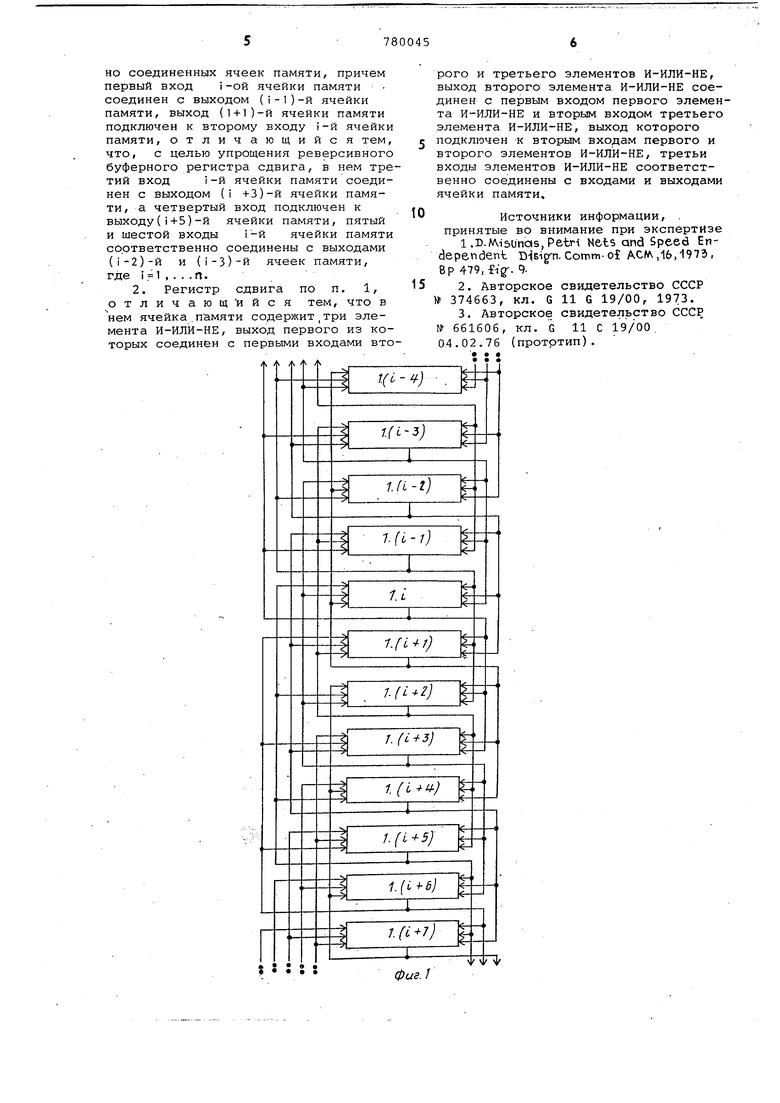

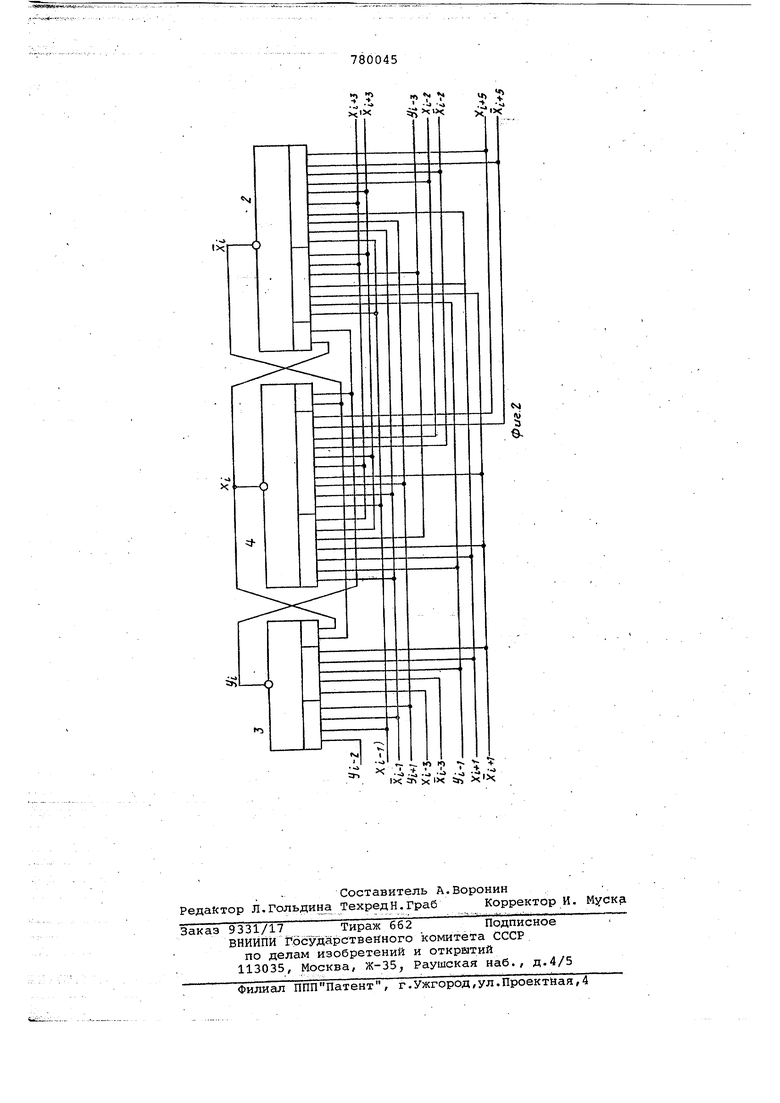

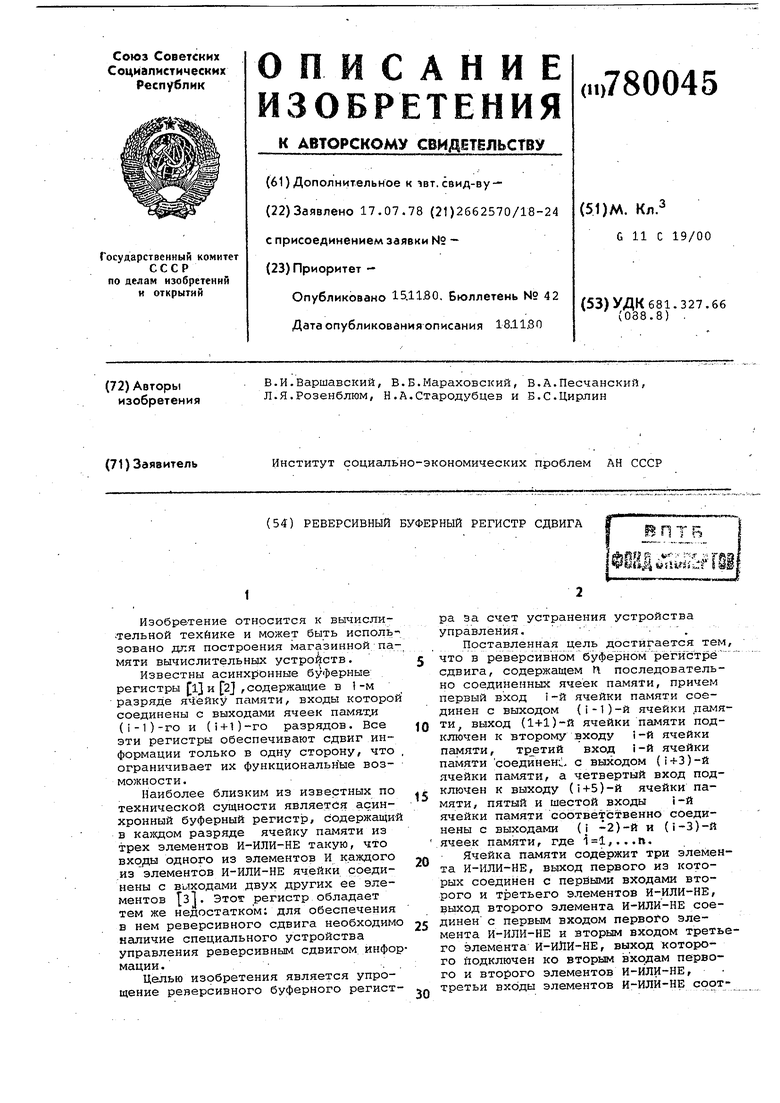

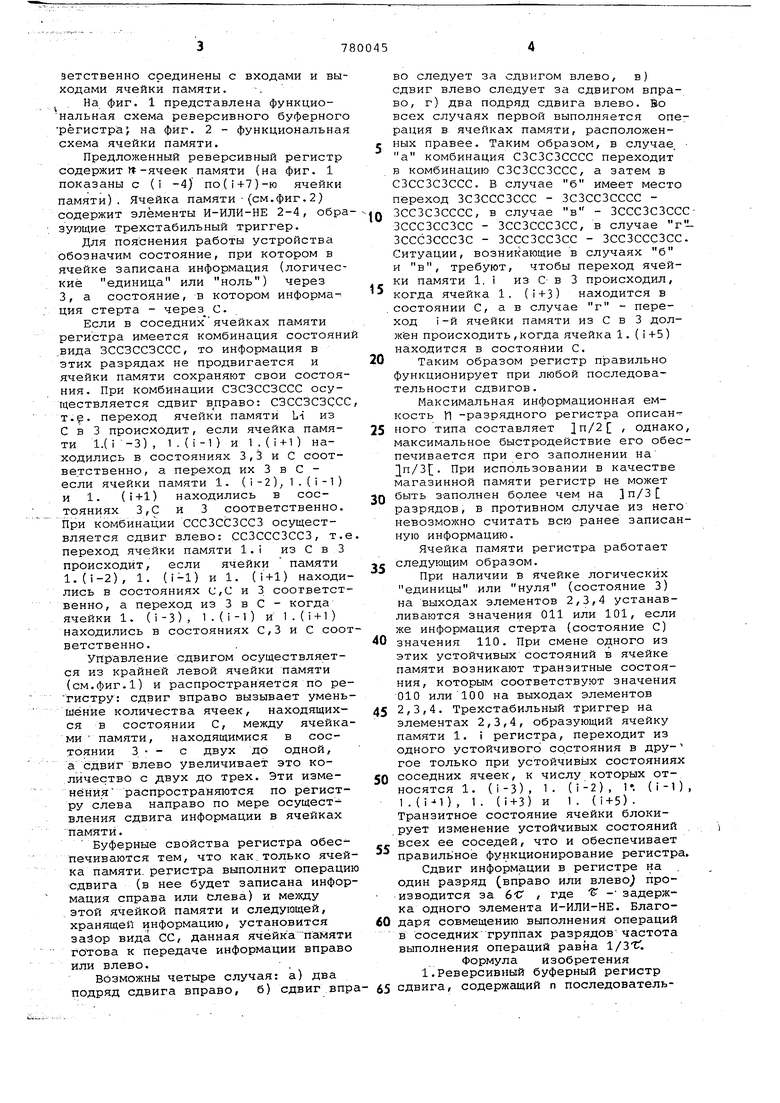

зетственно соединены с входами и выходами ячейки памяти. На фиг. 1 представлена функциональная схема реверсивного буферного регистра на фиг. 2 - функциональная схема ячейки памяти.

Предложенный реверсивный регистр содержит №-ячеек памяти (на фиг. 1 показаны с (1 -4) по(И-7)-ю ячейки памяти). Ячейка памяти (см.фиг.2) содержит элементы И-ИЛИ-НЕ 2-4, обра- эующие трехстабилъный триггер.

Для пояснения работы устройства обозначим состояние, при котором в ячейке записана информация (логические единица или ноль) через 3, а состояние, в котором информация стерта - через С.

Если в соседних ячейках памяти регистра имеется комбинация состояний вида ЗССЗССЗССС, то информация в этих разрядах не продвигается и ячейки памяти сохраняют свои состояния. При комбинации СЗСЗССЗССС осуествляется сдвиг в право: СЗССЗСЗССС, т.9. переход ячейки памяти L-i из С в 3 происходит, если ячейка памяти 1.(Г-3), l.(i-l) и l.(i+l) находились в состояниях 3,3 и С соответственно, а переход их 3 в С если ячейки памяти 1. (i-2),l.(i-1) и 1. (i+1) находились в состояниях 3,С и 3 соответственно. При комбинации СССЗССЗССЗ осуществляется сдвиг влево: ССЗСССЗССЗ, т.е. переход ячейки памяти 1.i из С в 3 происходит, если ячейки памяти l.(i-2), 1. (i-1) и 1. (i+1) находились в состояниях с,с и 3 соответственно, а переход из 3 в С - когда ячейки 1. (i-3), l.(i-l) и l.(i+l) находились в состояниях С,3 и С соответственно.

управление сдвигом осуществляется из крайней левой ячейки памяти (см.фиг.1) и распространяется по ре гистру: сдвиг вправо вызывает уменьшение количества ячеек, находящихся в состоянии С, между ячейками памяти, находящимися в состоянии 3 - с двух дб одной, а сдвиг влево увеличивает это количество с двух до трех. Эти изменения распространяются по регистру слева направо по мере осуществления сдвига информации в ячейках памяти.

Буферные свойства регистра обеспечиваются тем, что как.только ячейка памяти, регистра выполнит операцию сдвига (в нее будет записана информация справа или слева) и между этой ячейкой памяти и следующей, хранящей информацию, установится заЗор вида СС, данная ячейка памяти готова к передаче информации вправо или влево. ,

Возможны четыре случая: а) два подряд сдвига вправо, б) сдвиг вправо следует за сдвигом влево, в) сдвиг влево следует за сдвигом вправо, г) два подряд сдвига влево. Во всех случаях первой выполняется операция в ячейках памяти, расположенных правее. Таким образом, в случае а комбинация СЗСЗСЗСССС переходит в комбинацию СЗСЗССЗССС, а затем в СЗССЗСЗССС. В случае б имеет место переход ЗСЗСССЗССС - ЗСЗССЗСССС ЗССЗСЗСССС, в случае в - ЗСССЗСЗСССЗСССЗССЗСС - ЗССЗСССЗСС, в случае г ЗСССЗСССЗС - ЗСССЗССЗСС - ЗССЗСССЗСС. Ситуации, возникающие в случаях б и в, требуют, чтобы переход ячейки памяти 1. i из С в 3 происходил, когда ячейка 1. (i+3) находится в состоянии С, а в случае г - переход i-й ячейки памяти из С в 3 должен происходить , когда ячейка 1. (i +5) находится в состоянии С.

Таким образом регистр правильно функционирует при любой последовательности сдвигов.

Максимальная информационная емкость П -разрядного регистра описанного типа составляет 1п/2 , однако, максимальное быстродействие его обеспечивается при его заполнении на |п/31. При использовании в качестве агазинной памяти регистр не может быть заполнен более чем на п/3 разрядов, в противном случае из него невозможно считать всю ранее записанную информацию.

Ячейка памяти регистра работает следующим образом.

При наличии Б ячейке логических единицы или нуля (состояние 3) на выходах элементов 2,3,4 устанавливаются значения 011 или 101, если же информация стерта (состояние С) значения 110. При смене одного из этих устойчивых состояний в ячейке памяти возникают транзитные состояния, которым соответствуют значения 010 или 100 на выходах элементов 2,3,4. Трехстабильный триггер на элементах 2,3,4, образующий ячейку памяти 1. i регистра, переходит из одного устойчивого состояния в другое только при устойчивых состояниях соседних ячеек, к числу которых относятся 1. (i-3), 1. (i-2), 1. (i-1), 1 . (i-Ч) , 1 . (i+3) и 1 . (i+5) . Транзитное состояние ячейки блокирует изменение устойчивых состояний всех ее соседей, что и обеспечивает правильное функционирование регистра.

Сдвиг информации в регистре на . один разряд (вправо или влево) производится за бСГ , где Е - задержка одного элемента И-ИЛИ-НЕ. Благоаря совмещению выполнения операций в соседних группах разрядов частота выполнения операций равна 1/3С. Формула изобретения

1.Реверсивный буферный регистр двига, содержащий п последовательно соединенных ячеек памяти, причем первый вход i-ой ячейки памяти соединен с выходом (i- 1)-и ячейки памяти, выход (1+1)-и ячейки памяти подключен к второму входу i-й ячейки памяти, отличающийся тем, что, с целью упрощения реверсивного буферного регистра сдвига, в нем третий вход 1-и ячейки памяти соединен с выходом (i +3)-й ячейки памяти, а четвертый вход подключен к выходу(i+5)-и ячейки памяти, пятый и шестой входы i-й ячейки памяти соответственно соединены с выходами (1-2)-й и (1-3)й ячеек памяти, где i 1 ,...п.

2. Регистр сдвига по п. 1, отличающийся тем, что в нем ячейка .памяти содержит три элемента И-ИЛИ-НЕ, выход первого из которых соединен с первыми входами второго и третьего элементов И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ соединен с первым входом первого элемента И-ИЛИ-НЕ и вторым входом третьего элемента И-ИЛИ-НЕ, выход которого подключен к вторым входам первого и второго элементов И-ИЛИ-НЕ, третьи входы элементов И-ИЛИ-НЕ соответственно соединены с входами и выходами ячейки памяти.

o

Источники информации, . принятые во внимание при экспертизе l.D.wvi5Unas,Petri Nets and Speed Endependent D-jsig n. Comm-of ,1Ь.1975, Bp 479, ig-. q.

5

2.Авторское свидетельство СССР № 374663, кл. G 11 G 19/00, 1973.

3.Авторское свидетельство СССР № 661606, кл. G 11 С 19/00. 04.02.76 (протртип).

п-: х-х

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный буферный регистрСдВигА | 1979 |

|

SU841050A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| @ -Канальный формирователь последовательности импульсов | 1985 |

|

SU1305845A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Ячейка памяти для буферного регистра | 1980 |

|

SU928417A2 |

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1991 |

|

RU2022372C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1971 |

|

SU297040A1 |

«4

-О

X

s

о.

ю о

-а .д .J О .«S -,; IX ari X IX л ХХ

Авторы

Даты

1980-11-15—Публикация

1978-07-17—Подача