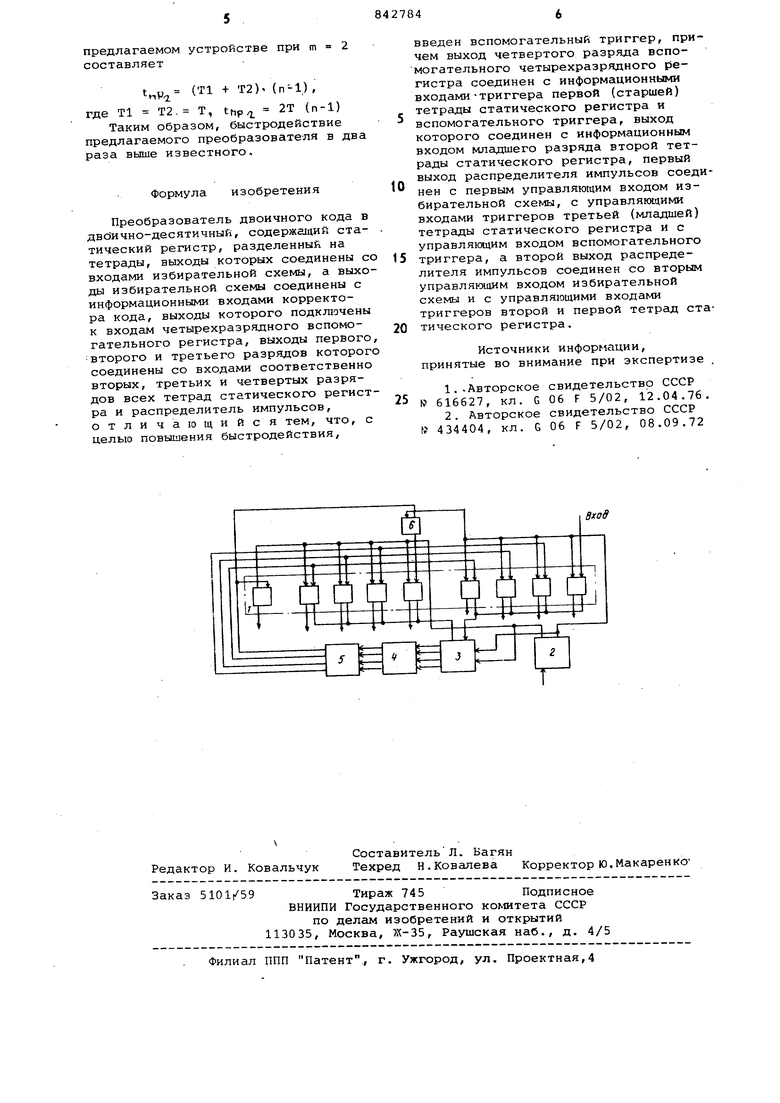

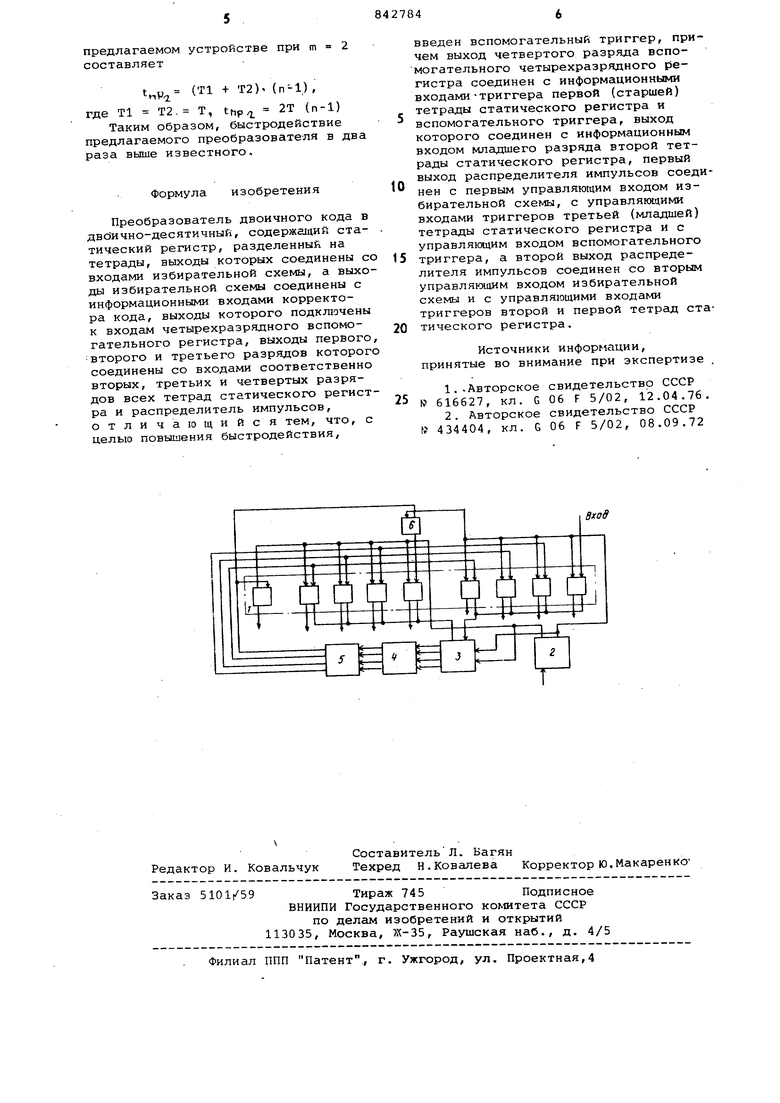

(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ. На чертеже показано предлагаемое устройство. Преобразователь содержит статичес кий регистр 1, распределитель 2 импульсов, избирательную схему 3, корректор 4 кода, вспомогательный ре гистр 5 и вспомогательный триггер 6 Статический регистр 1 предназначен для хранения промежуточных значений преобразования, а также для вы дачи окончательного результата преобразования в двоично-десятичном коде . Распределитель 2 импульсов формирует импульсы, необходимые для синхронизации работы всех узлов преобразователя. Так как в предлагаемом устройстве из-за ограничения преобразования двумя тетрадами кода (а для цикла преобразования каждой тетрады нужен только один такт) распределитель импульсов должен вырабатывать только прямую и инверсную последовательность тактов, то сам распределитель превращается в обычный инвертор При увеличении значения п преобразуе мого кода увеличивается и число тетрад двоично-десятичного эквивалента поэтому распределитель импульсов так же усложняется. Избирательная схема 3 служит для поочередного пропускания содержимого тетрад на общий корректор кода и представляет собой элемент совпадения для разрядов каждой тетрады. Корректор 4 кода предназначен дл анализа и коррекции содержимого тет рад и представляет комбинационную схему, зависимость между входом и вы ходом которой соледующая: ВходВыход 0000(0)0000(0) 0001(1)0001(1) 0010(2)0010(2) 0011(3)0011(3) 0100(4)0100(4) 0101(5)1000(8) 0110(6)1001(9) 0111(7)1010(10) 1000(8)1011(111 1001(9)1100(12) Отсюда следует, что входная ком бинация кода, имеющая значение 5-9, корректором увеличивается на три. Вспомогательный регистр 5 служит для хранения четырехразрядной скорр тированной информации после окончания такта коррекции тетрады. Следуе .заметить, что в предлагаемом устрой стве| одним и тем же тактовым импуль сом производится запись откорректированного кода тетрады и подача на коррекцию следующей тетрады. Поэтом техническая реализация регистра 5 должна быть таковой, чтобы обеспечи необновление содержимого регистра 5 до тех пор, пока не произошла запис откорректированной предыдущей тетра ды. Если регистр 5 реализовать как отенциальный (т.е. информация на го выходе изменяется только тогда, огда она изменилась на входе) и, роме того, так же реализовать коминационные схемы корректора и избиательного блока, то возникновение ышеуказанной ситуации исключено. Вспомогательный триггер б предазначен для промежуточного хранения таршего разряда откорректированной етрады. Если зна:чение преобразуемого кода п и ей соответствует m тетад двоично-десятичного эквивалента, то для предлагаемого устройства необходимо будет (т-2) вспомогательных триггеров. Устройство работает следующим образ.ом. Перед началом преобразования обнуляются все триггеры и регистры, начальное состояние которых влияет на результат преобразования. Обнуляется вспомогательный регистр 5, статический регистр 1 и вспомогательный триггер б. По первому такту (Ti) в младший разряд младшей тетрады статического регистра записывается старший разряд преобразуемого двоичного кода, в статический регистр записывается откорректированная младшая тетрада со сдвигом на один разряд влево (старший разряд тетрады записывается в вспомогательный, триггер б и передается вторая тетрада кода на коррекцию). Во время этого такта (Т1) происходит коррекция кода второй тетрады согласно вышеописанному алгоритму и запись откорректированного результата в регистр 5. По второму такту (Т2) записывается откорректированная вторая тетрада в статический регистр со сдвигом на один разряд влево, а на свободное место образовавшееся в результате этого сдвига (в младший разряд второй тетрады) - содержимое вспомогательного триггера б, а также подается на коррекцию младшая тетрада. Во время такта Т2 происходит коррекция младшей тетрады и запись откорректированного результата в регистр 5. Последующему такту (Т1) записывается следующий разряд преобразуемого двоичного кода, и циклы преобразования (коррекции и записи со сдвигом) тетрад продолжаются до тех пор, пока в статический регистр по дальнейшему такту (Т2) не запишется последний (младший) разряд преобразуемого двоичного кода. После этого в статическом регистре 1 находится двоично-десятичный эквивалент преобразуемого числа. , Очевидно, что общее время преобразования двоичного числа (tr,Po) в

предлагаемом устройстве при m « 2 составляет

(Т1 + Т2), (п-1),

где Т1 Т2. Т, thp 2Т (п-1) Таким образом, быстродействие предлагаемого преобразователя в два раза выше известного.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий статический регистр, разделенный на тетрады, выходы которых соединены со входами избирательной схемы, а выходы избирательной схемы соединены с информационными входами корректора кода, выходы которого подключены к входам четырехразрядного вспомогательного регистра, выходы первого, второго и третьего разрядов которого соединены со входами соответственно вторых, третьих и четвертых разрядов всех тетрад статического регистра и распределитель импульсов, от ли ч а ю щ и и с я тем, что, с целью повышения быстродействия.

введен вспомогательный триггер, причем выход ч;етвертого разряда вспомогательного четырехразр5здного регистра соединен с информационными входами-триггера первой (старшей) тетрады статического регистра и вспомогательного триггера, выход которого соединен с информационным входом младшего разряда второй тетрады статического регистра, первый выход распределителя импульсов соеди0нен с первым управляющим входом избирательной схемы, с управляющими входами триггеров третьей (младшей) тетрады статического регистра и с управляющим входом вспомогательного

5 триггера, а второй выход распределителя импульсов соединен со вторым управляющим входом избирательной схемы и с управляющими входами триггеров второй и первой тетрад ста0тического регистра.

Источники информации, принятые во внимание при экспертизе

1.-Авторское свидетельство СССР 25 № 616627, кл. G 06 F 5/02, 12.04.76,

2. Авторское свидетельство СССР 434404, кл. G 06 F 5/02, 08.09.72

Авторы

Даты

1981-06-30—Публикация

1979-10-12—Подача