1

Преобразователь последовательного двоичного кода в двоично-десятичный предназначен для использования в специализированных логических устройствах, оперирующих в двоичной системе счисления и выдаюп;их результаты обработки информации для восприятия в десятичной системе.

Известны преобразователи двоичного кода в двоично-десятичный, содержащие статический регистр, разделенный на тетрады, выходы которых соединены со входами избирательной схемы, корректор кода, четырехразрядный вспомогательный регистр, распределитель импульсов.

Предлагаемое устройство отличается от известных тем, что с целью упрощения устройства выходы избирательной схемы соединены через корректор кода со входами четырехразрядного вспомогательного регистра, выходы первого, второго и третьего разрядов этого регистра соединены со входами соответственно вторых, третьих и четвертых разрядов всех тетрад статического регистра, выход четвертого разряда четырехразрядного вспомогательного регистра соединен со входами первых разрядов всех тетрад статического регистра, кроме первой тетрады, выходы распределителя соединены с управляющими входами избирательной схемы и статического регистра.

Эти отличия позволяют использовать один

и тот же корректор кода и четырехразрядный

вспомогательный регистр для анализа всех

тетрад, что упрощает устройство и сокращает

количество оборудования.

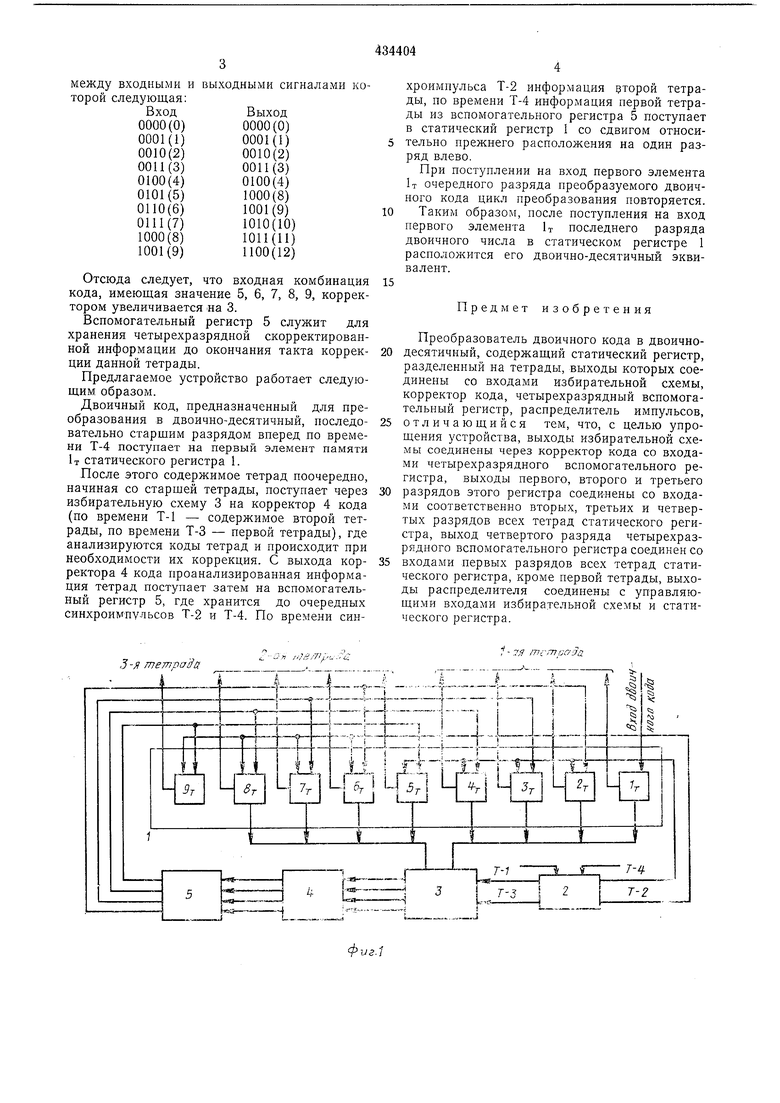

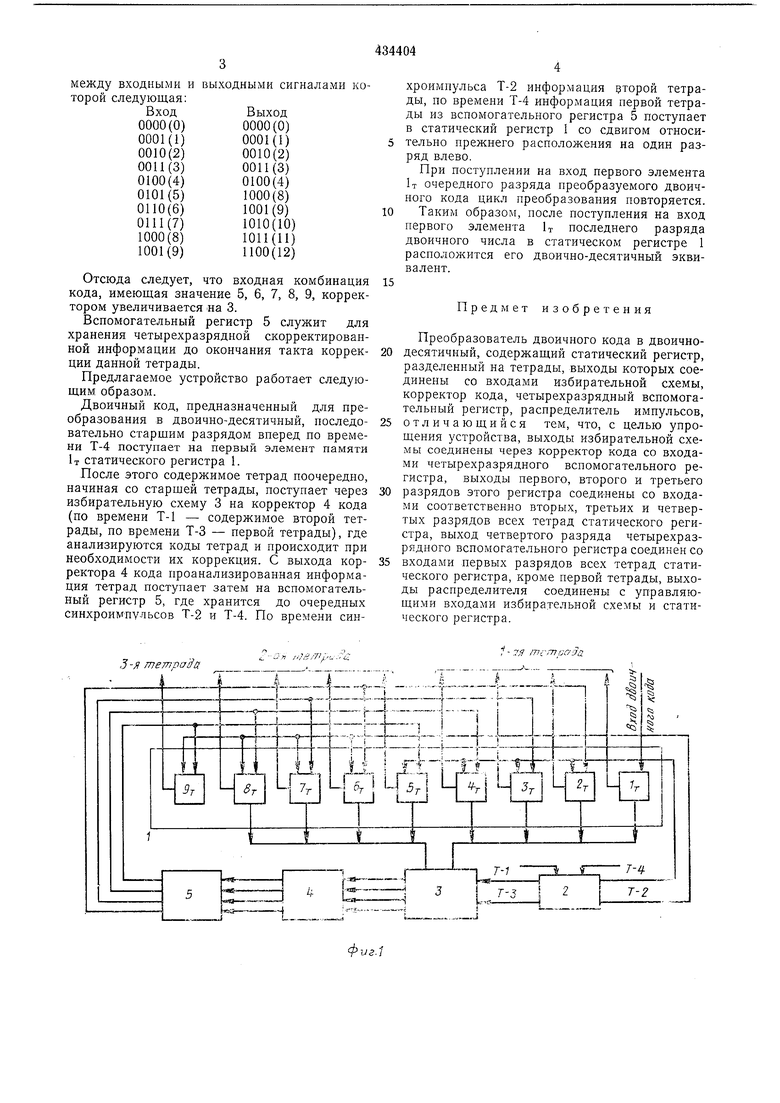

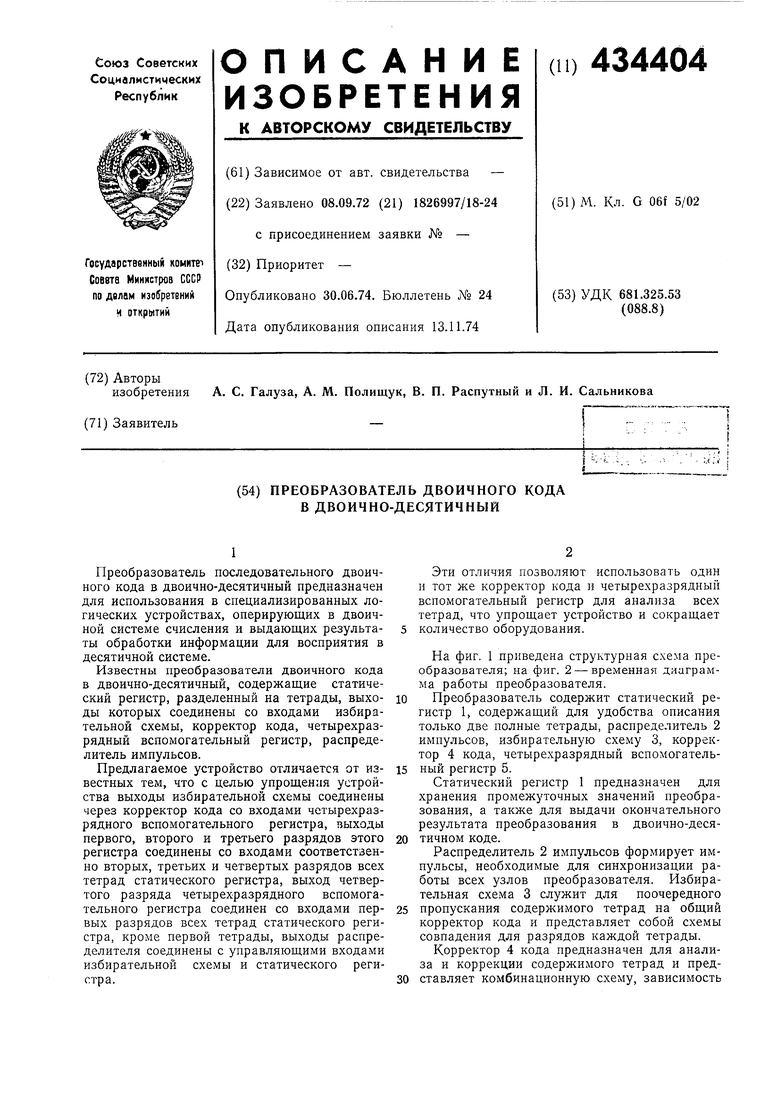

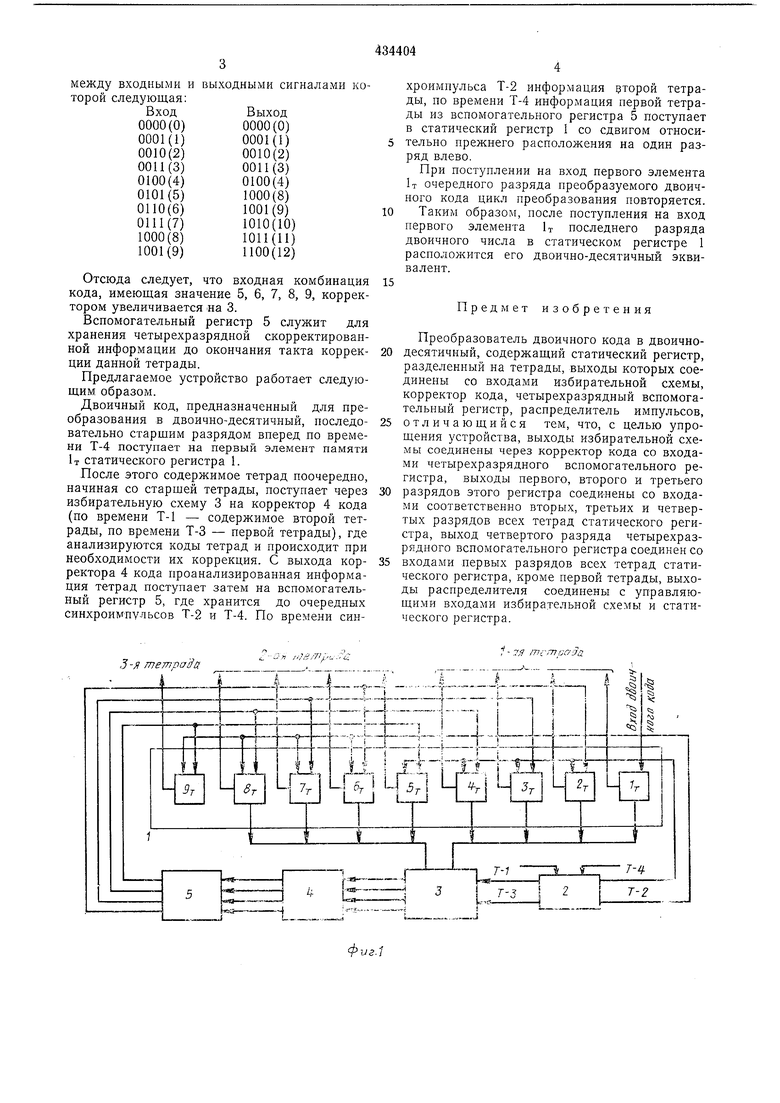

На фиг. 1 приведена структурная схема преобразователя; на фиг. 2 - временная диаграмма работы преобразователя.

Преобразователь содержит статический регистр 1, содержащий для удобства описания только две полные тетрады, распределитель 2 импульсов, избирательную схему 3, корректор 4 кода, четырехразрядный вспомогательный регистр 5.

Статический регистр 1 предназначен для хранения промежуточных значений преобразования, а также для выдачи окончательного результата преобразования в двоично-десятичном коде.

Распределитель 2 импульсов формирует импульсы, необходимые для синхронизации работы всех узлов преобразователя. Избирательная схема 3 служит для поочередного

пропускания содержимого тетрад на общий корректор кода и представляет собой схемы совпадения для разрядов каждой тетрады.

Корректор 4 кода предназначен для анализа и коррекции содержимого тетрад и представляет комбинационную схему, зависимость между входными и выходными сигналами ко торой следующая: ВходВыход 0000(0)0000(0) 0001(1)0001(1) 0010(2)0010(2) 0011(3)0011(3) 0100(4)0100(4) 0101(5)1000(8) 0110(6)1001(9) 0111(7)1010(10) 1000(8)1011(11) 1001(9)1100(12) Отсюда следует, что входная комбинация кода, имеющая значение 5, 6, 7, 8, 9, корректором увеличивается на 3. Всиомогательный регистр 5 служит для хранения четырехразрядной скорректированной информации до окончания такта коррекции данной тетрады. Предлагаемое устройство работает следующим образом. Двоичный код, предназначенный для преобразования в двоично-десятичный, последовательно старщим разрядом вперед по времени Т-4 поступает на первый элемент памяти IT статического регистра 1. После этого содержимое тетрад поочередно, начиная со старшей тетрады, поступает через избирательную схему 3 на корректор 4 кода (по времени Т-1 - содержимое второй тетрады, по времени Т-3 - первой тетрады), где анализируются коды тетрад и происходит при необходимости их коррекция. С выхода корректора 4 кода проанализированная информация тетрад поступает затем на вспомогательный регистр 5, где хранится до очередных синхроимпульсов Т-2 и Т-4. По времени синJ- т em patis

- zf тстаауа хроимпульса Т-2 информация дторой тетрады, по времени Т-4 информация первой тетрады из вспомогательного регистра 5 поступает в статический регистр 1 со сдвигом относительно прежнего расположения на один разряд влево. При поступлении на вход первого элемента IT очередного разряда преобразуемого двоичного кода цикл преобразования повторяется. Таким образом, после поступления на вход первого элемента 1т последнего разряда двоичного числа в статическом регистре 1 расположится его двоично-десятичный эквивалент. Предмет изобретения Преобразователь двоичного кода в двоичнодесятичный, содержащий статический регистр, разделенный на тетрады, выходы которых соединены со входами избирательной схемы, корректор кода, четырехразрядный вспомогательный регистр, распределитель импульсов, отличающийся тем, что, с целью упрощения устройства, выходы избирательной схемы соединены через корректор кода со входами четырехразрядного вспомогательного регистра, выходы первого, второго и третьего разрядов этого регистра соединены со входами соответственно вторых, третьих и четвертых разрядов всех тетрад статического регистра, выход четвертого разряда четырехразрядного вспомогательного регистра соединен со входами первых разрядов всех тетрад статического регистра, кроме первой тетрады, выходы распределителя соединены с управляющими входами избирательной схемы и статического регистра.

ТИ-1 rh-2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU842784A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1974 |

|

SU603985A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1974 |

|

SU549801A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНО- ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ | 1970 |

|

SU260962A1 |

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1983 |

|

SU1142826A1 |

Даты

1974-06-30—Публикация

1972-09-08—Подача