(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КВАЗИКАНОНИЧЕСКОГО МОДИФИЦИРОВАННОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КАНОНИЧЕСКИЙ КОД

третьей группы, выходы одноименных элементов И первой и третьей групп соединены через соответствующие элементы ИЛИ группы со счетными входами разрядов регистра числа, первый информационный вход преобразователя соединен с первыми входами первого и второго элементов И и со вторыми входами элементов И второй группы, второй информационный вход преобразователя соединен со вторым входом первого элемента И, выход которого соединен со вторыми входами элементов И третьей группы, второй тактирущий вход преобразователя подключен к третьему входу первого и второго входу второго элементов И, выход последнего из которых подключен ко вторым входам элементов И первой группы, а третий тактирующий вход преобразователя соединен с входами записи информации вспомогательного регист- ра.

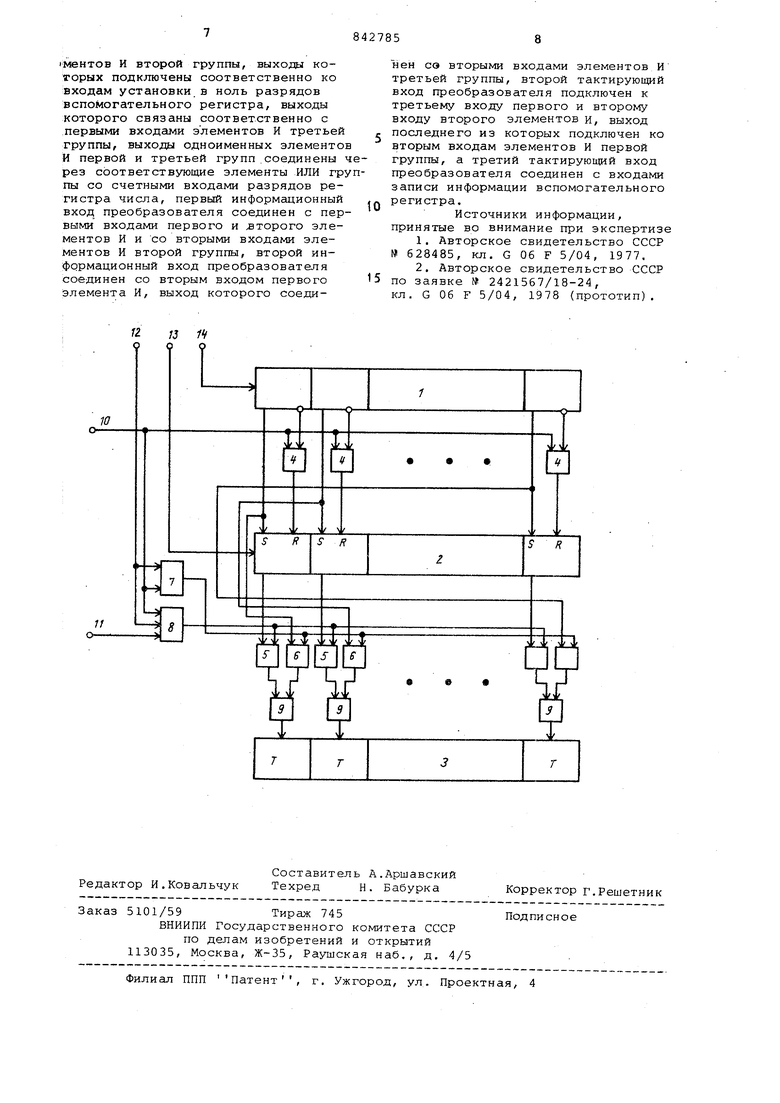

На чертеже изображена структурная схема преобразователя последовательного двоичного квазиканонического модифицированного кода в параллельный канонический код.

Преобразователь содержит распределитель 1 сигналов, который может быт выполнен, например, как кольцевой празрядный сдвиговой регистр или счетчик с дешифратором на п входов, вспомогательный регистр 2, содержащий п тактируемых RS-триггеров, регистр 3 числа, содержайшй п Т-триггеров, группы элементов И 4 - 6, элементы И 7 и 8, группу элементов ИЛИ 9, информационные входы 10 и 11 и тактирующие входы 12 - 14,

Прямые выходы распределителя 1 сигналов соединены с входами регистра 2 и с первыми входами элементов И 6 первой группы, а инверсные выходы распределителя 1 подключены к первым входам элементов И 4 второй группы, подключенных выходами к входам регистра 2, выходы которого связаны с первыми входами элементов И 5 третьей группы. Выходы элементов И 5 и б второй и третьей групп соединены со входами группы элементов ИЛИ 9 выход которой подключен к счетным входам регистра 3 числа. Информационный вход 10 преобразователя подведен к первым входам элементов И 8 и 7 и вторым входам элементов И 4второй группы, а информационный вход 11 связан со вторым входом элемента И 8 выхол которого соединен со вторыми входйми элементов И 5 третьей группы. Тактирующий вход 12 подключен к третьему входу элемента И 8 и второму входу элемента И7, выходом подключенного ко вторым входам элементов И б первой группы, тактирующий вход 13 соединен с цепями приема

кода вспомогательного регистра 2, а тактирующий вход 14 подключен к управляющему входу расспределителя 1 сигналов.

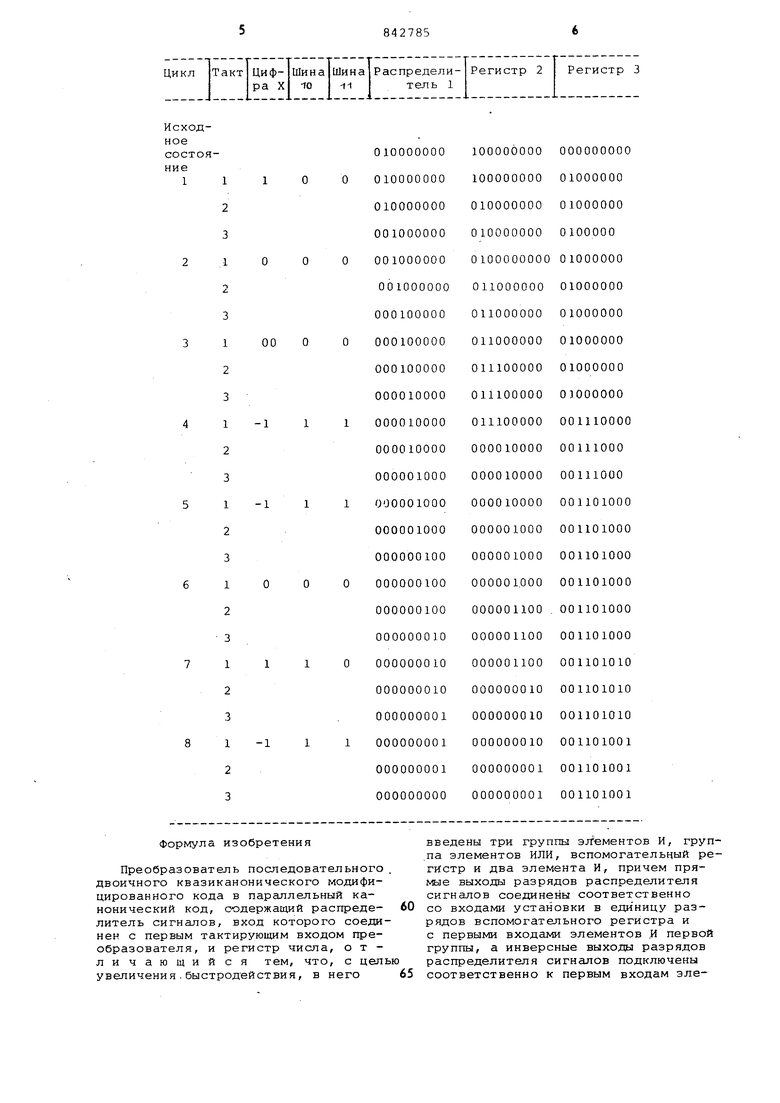

Преобразователь работает следующим образом,

В исходном состоянии в распределителе 1 сигнешов единица: находится во втором, а во вспомогательном регистре 2 - в первом разряде слева, в, остальных разрядах записаны нули,

В каждом i-M цикле (i I,n-l) на информационные входы 10 и 11 поступает цифра а,- операнда А, имеющая вес 2 и принимающая значение из множества , О, ij , Цифры кодируютс следующим образом:

ЗначениеШинаШина

цифры1Q11

110

0ОО

1;11

На выходе распределителя 1 единица нходится в -И-м разряде,

В первом такте каждого i-ro цикла по сигналу с входа 12 происходит инвертирование 1-го разряда регистра 3, если принимаемая цифра равна 1 или 1, Если принимаемая цифра равна 1, то в регистре 3, кроме тог.о, происходит инвертирование тех разрядов, на которые поступают единицы с вспомогательного регистра 2, Если принимаемая цифра равна О, то содержимое регистра 3 не меняется,

Во втором такте по сигналу с входа 13 в i-й разряд вспомогательного регистра 2 записывается единица. Если же поступившая цифра равна 1 или Т, то при этом происходит еще -и обнуление остальных разрядов регистра 2

В третьем такте по сигналу с выхода 14 единица в распределителе 1 сигналов сдвигается на один разряд вправо.

Если распределитель 1 и регистр 2 выполнены на триггерах .:: внутренней задержкой, то тактирующие сигналы с входов 12 - 14 могут подаваться одновременно,

В результате выполнения 1-го цикла в регистре 3 числа формируется результат A, причем крайний .слева разряд является знаковым.

При выполнении регистра 2 и распределителя 1 сигналов на триггерах внутренней задержкой время преобразования п-1 разрядного кода с помощью предлагаемого устройства приблизително равно ntr.

Таким образом, предлагаемое устройртво превосходит по быстродействи известное примерно в п раз,

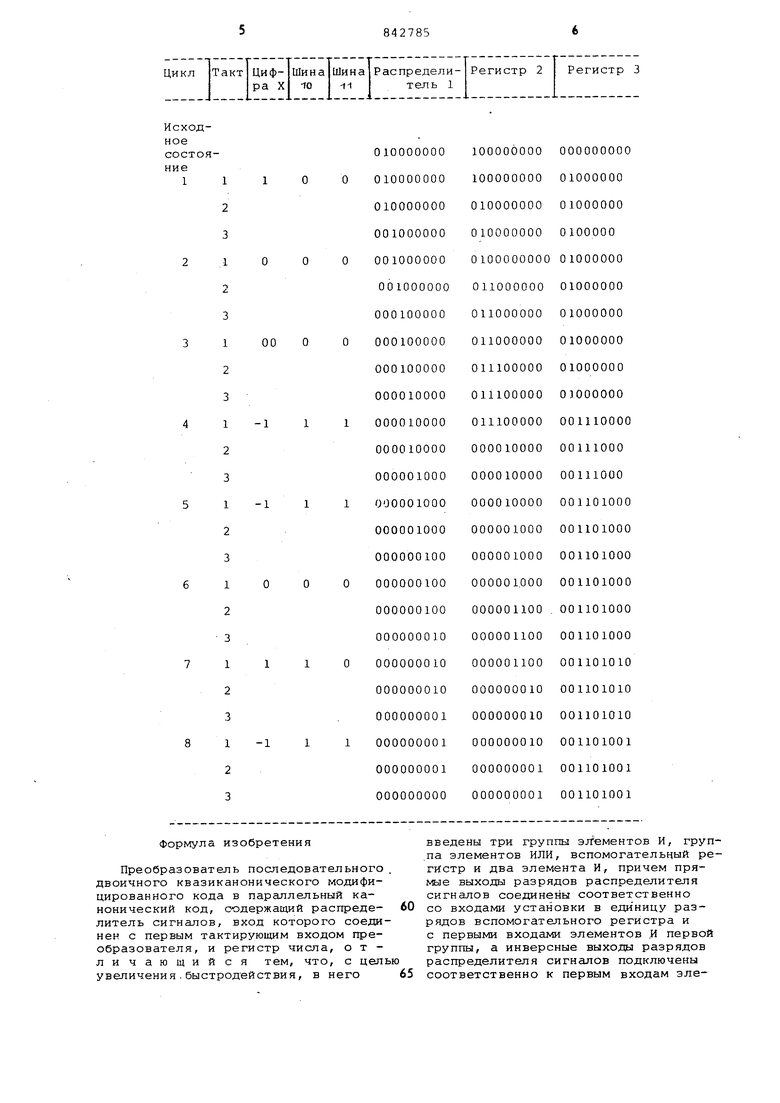

В таблице приведен пример формирования устройством результата А при поступлении на него операнда А 10011011.

Формула изобретения

Преобразователь последовательного . двоичного квазиканонического модифицированного кода в параллельный канонический код, содержащий распределитель сигналов, вход которого соединен с первым тактирующим входом преобразователя, и регистр числа, отличающий ся тем, что, с цель увеличения.быстродействия, в него

введены три группы эх %ментов И, груп,па элементов ИЛИ, вспомогательный регистр и два элемента И, причем прямые выходы разрядов распределителя сигналов соединены соответственно со входами устайовки в единицу разрядов вспомогательного регистра и с первыми входами элементов И первой группы, а инверсные выходы разрядов распределителя сигналов подключены соответственно к первым входам элементов И второй группы, выходы которых подключены соответственно ко входам установки.в ноль разрядов вспомогательного регистра, выходы которого связаны соответственно с первыми входами элементов И третьей группы, выходы одноименных элементо И первой и третьей групп .соединены рез соответствующие элементы .ИЛИ гр пы со счетными входами разрядов регистра числа, первый информационный вход преобразователя соединен с пер выми входами первого и второго элементов И и со вторыми входами элементов И второй группы, второй инфррмационный вход преобразователя соединен со вторым входом первого элемента И, выход которого соеди йен се вторыми входами элементов. И третьей группы, второй тактирующий вход преобразователя подключен к третьему входу первого и второму входу второго элементов и, выход последнего из которых подключен ко вторым входам элементов И первой группы, а третий тактирующий вход преобразователя соединен с входами записи информации вспомогательного регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 628485, кл. G Об F 5/04, 1977. 2.Авторское свидетельство СССР по заявке 2421567/18-24, кл. G 06 F 5/04, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 1990 |

|

RU2022337C1 |

| Устройство для сдвига последовательных чисел в избыточном коде | 1986 |

|

SU1348823A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1976 |

|

SU662936A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

Авторы

Даты

1981-06-30—Публикация

1979-07-10—Подача