1

Изобретение относится к лычисли- тельной технике и может быть использовано при разработке быстродействук щих устройств для умножения двоичных и десятичных чисел.

Цель изобретения - сокращение количества оборудования устройства.

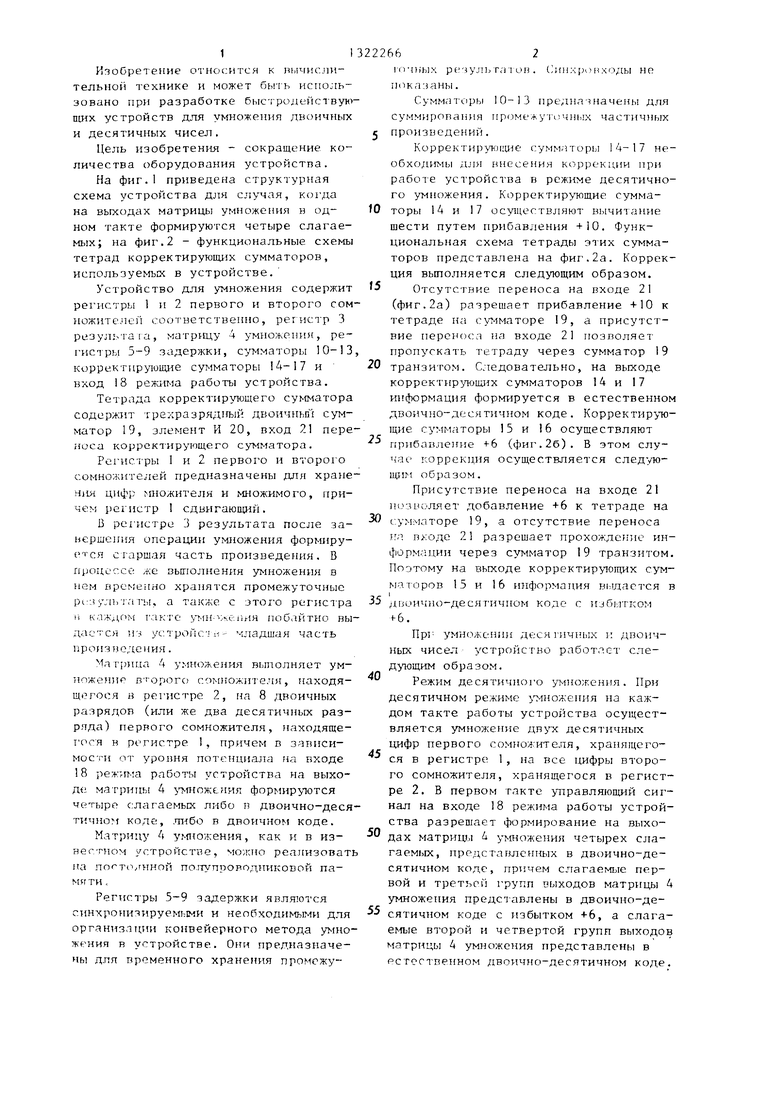

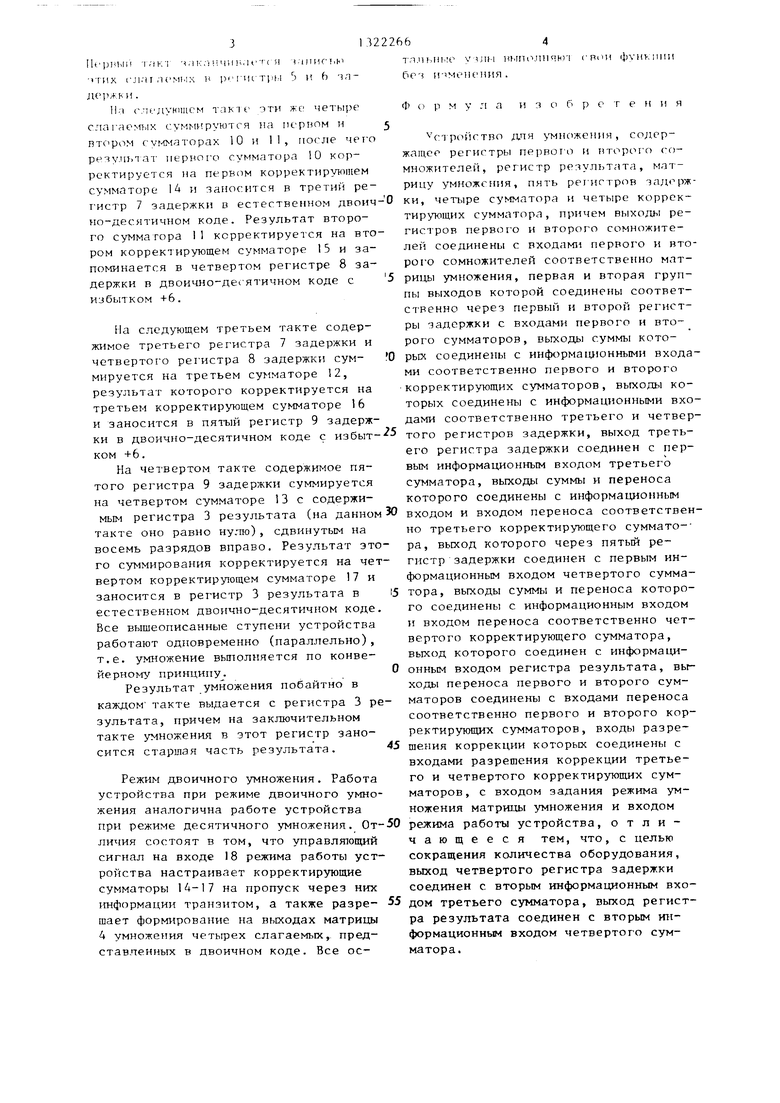

На фиг.1 приведена структурная схема устройства для случая, когда на выходах матрицы умножения в одном такте формируются четыре слагаемых; на фиг.2 - функциональные схемы тетрад корректирующих сумматоров, используемьк в устройстве.

Устройство для умножения содержит регистры 1 и 2 первого и второго сом ножителеГт соответственно, регистр 3 результата, матрицу 4 умножепия, регистры 5-9 задержки, с:,т4маторы 10-13 корректирующие сумматоры I4-I7 и вход 18 режима работы устройства.

Тетрада корректирующего сум 1атора содержит трехразряд1Шй двоичньй сумматор 19, элемент И 20, вход 21 переноса корректирующего сумматора.

Регистры I и 2 первого и второго сомножителей предназначены для хранения цифр множителя и множимого, причем регистр 1 сдвигающий.

В регистре 3 результата после за- нершения операции умножения формируется сгаршая часть произведения. В процессе же выполнения умножения в нем хранятся промежуточные pi:Li yjib i аты, а так л;е с зтого регистра ti каждом 1 акте умН Х, побайтно выдается из устройс 11- младшая часть ироизнедеиия.

MaTinn a 4 умножения выполняет умножение в гор : го сомножителя, находящегося в регистре 2, на 8 двоичных разрядов (или же два десятичньк раз- рядгО первого сомножителя, находяще- 1 ося в регистре 1 , причем в зависимости от уровня потенциала на входе 18 режима работы устройства на выходе матрицы А хт тножения формируются четыре слагаемых либо в двоично-десятичном коде, либо в двоичном коде.

Матрицу 4 умножения, как и в известном устройстве, молаю реализоват па погтолнной по.ггупрородниковой па- мя ти.

Регистры 5-9 задержки являются синхронизируемыми и необходимььми для организации конвейерного метода умножения в устройстве. Они предназначены для временного хранения промсжу

10

5

20

222662

точных результатов, (.xponxo ы не показаны.

Сумматоры 10-13 предпа начеиы для суммирования гфомелутичных частич) 5 произведений.

Корректируки Ц1е сумматоры 14-17 необходимы для внесения коррекции при работе устройства в режиме десятичного умножения. Корректирующие сумматоры 14 и 17 осуществляют вычи1ание шести путем прибавления +10. Функциональная схема тетрады этих сумматоров представлена на фиг.2а. Коррекция вьшолняется следующим образом.

Отсутствие переноса на входе 21 (фиг.2а) разрешает прибавление +10 к тетраде на сут-1маторе 19, а присутствие переноса на входе 21 позволяет пропускать тетраду через сумматор 19 транзитом. Следовательно, на выходе корректир; тощих сумматоров 14 и 17 информация формируется в естественном двоично-десятичном коде. Корректирующие сумматоры 15 и 16 осуществляют прибавление +6 (фиг.2б). В этом случае Оррекция осуществляется следующим образом.

Присутствие переноса на входе 21 позволяет добавление +6 к тетраде на (.сумматоре 19, а отсутствие переноса и; , входе 21 разрешает прохождение информации через сумматор 19 транзитом. Поэтому на выходе корректирующих с , маторов 15 и 16 информация выдастся в

I

двоично-десяг ичном коде с избытком

+ 6.

Прг умн(1жени1 десятичных т: двоичных чисел устройство работает сле- д 1ощим образом.

Режим десятичного умножения. При десятичном режиме 1ножения на каждом такте работы устро11ства осуществляется умножение цвук десятичных цифр первого сомножителя, хранящегося в регистре 1, на все цифры второго сомножителя, хранящегося в регистре 2. В первом такте управляющий сигнал на входе 18 режима работы устройства разрешает формирование на выходах матрицы 4 уьдаожения четырех слагаемых, предетавленгшх в двоично-десятичном коде, причем слагаемые первой и третьей групп тзыхояов матрицы 4 умножения представлены в двоично-десятичном коде с избытком +6, а слага- erftie второй и четвертой групп выходов матрицы 4 умножения представлены в естестпенном двоично-десятичном коде.

30

35

40

45

50

55

Ilcplibll l l. lK r Ч,-П :Г1 i;4Hli,U T( я f.-iHHC I.Kl

гллг лсмых и PC гиг Tpt. S и Ь ьч- дс ржн и .

Па с. тгдуниисм тактг эти жс четыре с.чагаемых суммируются на перном и j втсфом суг 1маторах 10 и 11, после чег о резултлат мерного сумматора 10 корректируется на первом корректнрукнием сумматоре 1А и заносится в третий ре- 1 истр 7 задержки в естественном двоич- О но-десятичном коде. Результат второго сумматора 1 корректируется на втором корректирующем сумматоре 15 и запоминается в четвертом регистре 8 задержки в двоично-десятичном коде с 5 избытком +6.

На следующем третьем такте содержимое третьего регистра 7 задержки и четвертого регистра 8 задержки сум- О мируется на третьем сумматоре 12, результат которого корректируется на третьем корректирующем сумматоре 16 и заносится в пятый регистр 9 задержки в двоично-десятичном коде с избыт- ком +6.

На четвертом такте содержимое пятого регистра 9 задержки суммируется на четвертом сумматоре 13 с содержитлльт1г:е vчлм иыполняьп сяои i)vnv,iiiiM беч И ме1и ния .

Ф о р м у л а и 3 о б р с т е и и я

cipoiicTBo дпя т нс жеиия, содержащее регистры первог о и нторог о го- множителеГ, регистр результата, матрицу умножения, пять регистров тадорж- ки, четыре сумматора и четыре корректирующих сумматора, причем выходы регистров первого и второго сомножителей соединены с входами первого и второго сомножителей соответственно матрицы умножения, первая и вторая группы выходов которой соединены соответственно через первый и второй регистры задержки с входами первого и второго сумматоров, выходы суммы которых соединены с информащюнными входами соответственно первого и второго корректирующих сумматоров, выходы которых соединены с информационными входами соответственно третьего и четвертого регистров задержки, выход третьего регистра задержки соединен с первым информационным входом третьего сумматора, выходы суммы и переноса которого соединены с информационным

мым регистра 3 результата (на данном 50 входом и входом переноса соответствен- такте оно равно нулю), сдвинутым на но третьего корректирующего суммато- восемь разрядов вправо. Результат это- ра, выход которого через пятый ре- го суммирования корректируется на четвертом корректирующем сумматоре 17 и заносится в регистр 3 результата в естественном двоично-десятичном коде. Все вышеописанные ступени устройства работают одновременно (параллельно), т.е. умножение выполняется по конвейерному принципу.

Результат умножения побайтно в

гистр задержки соединен с первым информационным входом четвертого сумма15 тора, выходы суммы и переноса которого соединены с информационным входом и входом переноса соответственно четвертого корректирующего сумматора, выход которого соединен с информаци0 онным входом регистра результата, выходы переноса первого и второго сумматоров соединены с входами переноса соответственно первого и второго корректирующих сумматоров, входы разре- 45 щения коррекции которых соединены с входами разрешения коррекции третьего и четвертого корректирующих сумматоров, с входом задания режима умножения матршды умножения и входом

каждом такте выдается с регистра 3 результата, причем на заключительном такте умножения в этот регистр заносится старшая часть результата.

0 онным входом регистра результата, в ходы переноса первого и второго сум маторов соединены с входами перенос соответственно первого и второго ко ректирующих сумматоров, входы разре 45 щения коррекции которых соединены с входами разрешения коррекции третье го и четвертого корректирующих сумматоров, с входом задания режима ум ножения матршды умножения и входом

Режим двоичного умножения. Работа устройства при режиме двоичного умножения аналогична работе устройства при режиме десятичного умножения. От-50 режима работы устройства, о т л и - личия состоят в том, что управляющий чающееся тем, что, с целью сигнал на входе 18 режима работы уст- сокращения количества оборудования, ройства настраивает корректирующие сумматоры 14-17 на пропуск через них 1шформации транзитом, а также разре- щает формирование на вькодах матрицы

выход четвертого регистра задержки соединен с вторым информационным вхо 55 дом третьего сумматора, выход регис ра результата соединен с вторым mt- формационным входом четвертого сумматора.

4 умножения четырех слагаемых,, представленных в двоичном коде. Все ос3222664

тлльт1г:е vчлм иыполняьп сяои i)vnv,iiiiM беч И ме1и ния .

Ф о р м у л а и 3 о б р с т е и и я

cipoiicTBo дпя т нс жеиия, содержащее регистры первог о и нторог о го- множителеГ, регистр результата, матрицу умножения, пять регистров тадорж- ки, четыре сумматора и четыре корректирующих сумматора, причем выходы регистров первого и второго сомножителей соединены с входами первого и второго сомножителей соответственно матрицы умножения, первая и вторая группы выходов которой соединены соответственно через первый и второй регистры задержки с входами первого и второго сумматоров, выходы суммы которых соединены с информащюнными входами соответственно первого и второго корректирующих сумматоров, выходы которых соединены с информационными входами соответственно третьего и четвертого регистров задержки, выход третьего регистра задержки соединен с первым информационным входом третьего сумматора, выходы суммы и переноса которого соединены с информационным

0 входом и входом переноса соответствен- но третьего корректирующего суммато- ра, выход которого через пятый ре-

гистр задержки соединен с первым информационным входом четвертого сумма15 тора, выходы суммы и переноса которого соединены с информационным входом и входом переноса соответственно четвертого корректирующего сумматора, выход которого соединен с информаци0 онным входом регистра результата, выходы переноса первого и второго сумматоров соединены с входами переноса соответственно первого и второго корректирующих сумматоров, входы разре- 5 щения коррекции которых соединены с входами разрешения коррекции третьего и четвертого корректирующих сумматоров, с входом задания режима умножения матршды умножения и входом

0 режима работы устройства, о т л и - чающееся тем, что, с целью сокращения количества оборудования,

50 режима работы устройства, о т л и - чающееся тем, что, с целью сокращения количества оборудования,

выход четвертого регистра задержки соединен с вторым информационным вхо- 55 дом третьего сумматора, выход регистра результата соединен с вторым mt- формационным входом четвертого сумматора.

21

о

W

Редактор П.Гереюи

Составитель Н.Маркелова

Техред Л.Олийнык Корректор И. Муска

Заказ 2865/45 Тираж 672Подписиое

ВНИИПИ Государствениого комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

f i9 г

I

1

11 if

05 6 Ьг ь fe.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения | 1988 |

|

SU1501046A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения двоичных и десятичных чисел. Целью изобретения является сокращение количества оборудования устройства. Цель достигнута за счет изменения функций второго и третьего корректирующих сумматоров 15 и 16 и связей между узлами устройства, что позволило исключить из устройства два корректирующих сумматора и один регистр задержки. В устройстве применен конвейерный принцип обработки ииформации с анализом в каждом такте двух десятичных цифр или же восьми двоичных цифр множителя. Устройство содержит регистры 1-3 сомножителей и результата, матрицу 4 умножения, регистры 5-9 задерж- с ки, сумматоры 10-13 и корректирующие сумматоры 14-17. 2 ил.

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-10-24—Подача