(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЛ КВАДРАТНОГО КОРНЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1979 |

|

SU922735A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU957209A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления функции х= @ + @ | 1981 |

|

SU964634A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1007103A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах.

По основному авт.св. № 611208 известно устройство для извлечения квадратного корня,содержащее входной и выходной регистры, блок управления, блок подбора цифр результата, постоянное запоминающее устройство, схему сравнения, входы которой соединены с выходом постоянного запоминающего устройства и первого входного регистра, вход которого подключен к первому входу устройства, выход останова схемы сравнения соединен со входом блока управления, а два других - с информационными входами блока подбора цифр результата, управляющий вход которого соединен с выходом блока управления, а выход блока подбора цифр результата через выходной регистр соединен с ijepBHM входом постоянного запоминающего устройства и с первым .выходом устройства 1 .

Недостаток известного .устройстваограниченные функциональные возможности (его можно использовать только для извлечения квадратного корня)

Цель изобретения - расширение функциональных возможностей за счет дополнительного вычисления взаимообратных монотонно изменяющихся функций и выполнения операции деления.

Поставленная цель достигается тем, что в устройство дополнительно введены входной регистр и коммутатор, причем второй вход устройства соединен со вторым входом постоянного запоминающего блока, третий вход которого подключен к выходу коммутатора, первый, второй и третий входы которого соединены соответственно с выходом выходного регистра, третьим входом устройства и выходом второго входного регистра, выход которого является четвертым входом устройства, выход постоянного запоминающего устройства является вторым . выходом устройства.

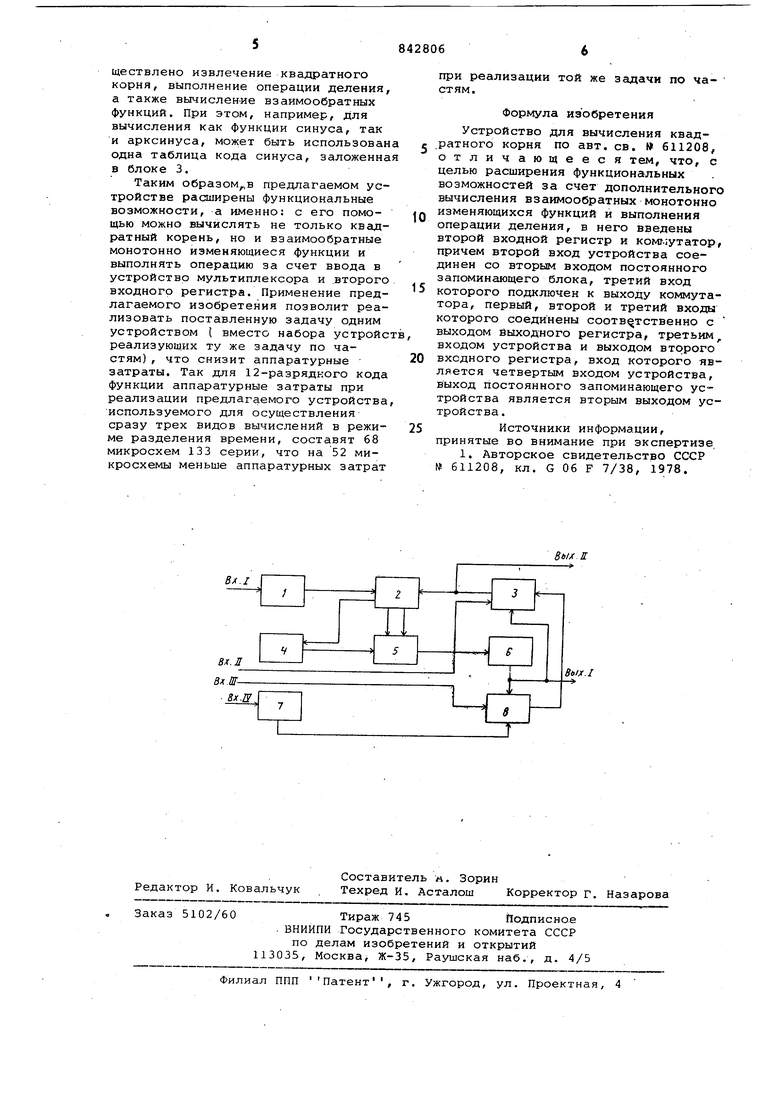

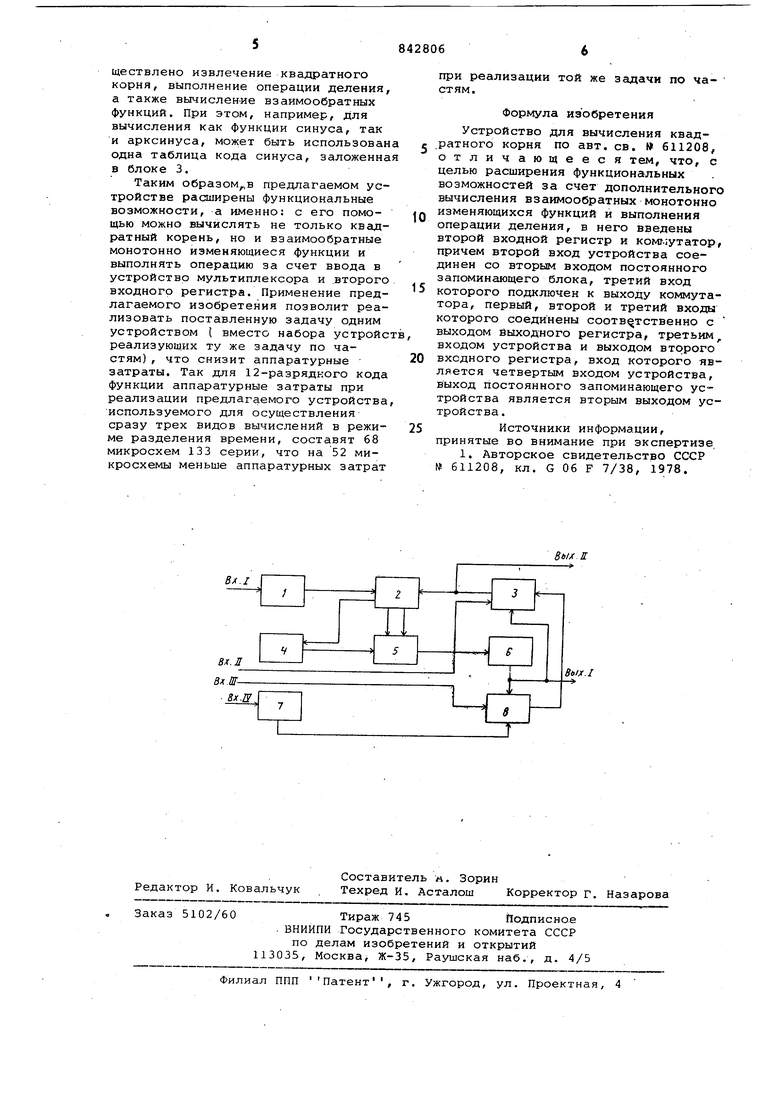

Блок-схема устройства представлена на чертеже.

Устройство содержит первый входной регистр 1, схему 2 сравнения, постоянное запоминающее устройство 3, блок 4 управления, блок 5 подбора цифр результата, выходной регистр 6, второй входной регистр 7, коммутатор 8.

Устройство работает следующим образом.

При наличии команды Вычисление каадратного корня в первый входной регистр 1 заносится параллельный код аргумента X. Все разряды выходного регистра 6 устанавливаются в нуле,вые состояния, а блок 3 по команде, поступающей нэ второй вход устройства, переводится в режим умножения двоичных чисел. В этом случае первый и третий входы блока 3 соответствуют входам умножителя кодов, а выход блока 3 -.выходу умножителя. С помощью коммутатора 8 по команде, поступающей на третий вход устройства осуществляется подключение на оба входа блока 3 выхода выходного регистра 6. Таким образом, при выполнении операции извлечения квадратного корня блок 3 и коммутатор 8 осуществляют возведение в квадрат значения кода, снимаемого с выхода выходного регистра 6. В первом такте вычислений включается генератор тактовых импульсов в блоке 4 управления и с en выходов (число которых равно нислу разрядов входного регистра 1) в каждом такте появляются управляющие импульсы. Первый управляющий импульс (в первом такте) устанавливает логическую единицу в самом старшем разряде выходного регистра 6. Содержание которого возводится в квадрат в блоке 3 и сравнивается схемой сравнения 2 с содержанием входного регистра 1. Если значение квадрата в выходном регистре 6 больше значения аргумента X во входном регистре 1, то со второго выхода схемы сравнения 4 на соответствующий информационный вход блока подбора цифр результата 5 выдается сигнал, который открывает в блоке 5 соответствующие элементы И (на входах сброса старшего разряда и установки следующего разряда выходного регистра 6). В следующем такте управляющий импульс со следующего выхода блока 4 управления проходит через откритые элементы И и устанавливает логический нуль в старшем разряде и логическую единицу в следукнаем разряде. Если квадрат значения в выходном регистре 6 меньше аргумента X, то с третьего выхода схемы 2 сравнения на другой информационный вход блока 5 подбора цифр результата выдается сигнал, который открывает в блоке 5 соответствующий элемент И (на выходе установки соответствующего разряда выходного регистра 6). В следующем такте управляющий импуль со следующего выхода блока управления 4 проходит через этот элемент И и устанавливает логическую единицу в следующем разряде.Предыдущий старщий разряд при этом остается значащим. Полученное число в выходном регистре 6 возводится блоком 3 в квадрат и сравнивается в схеме 2 сравнения со значением аргумента X и т.д. Если квадрат значения в выходном регистре 6 равен значению аргумента X, то с первого выхода схемы 2 сравнения на вход блока 4 управления-выдается сигнал, который останавливает работу устройства, так как процесс вычисления квадратного корня закончен. Максимальное число тактов равно п - 4HCJiy разрядов входного регистра 1.

При наличии команды Вычисление кода угла в первый входной ре-, гистр 1 заносится значение величины sinp.Bce разряды выходного регистра устанавливаются в нулевые состояния а блок 3 по команде, поступающей на второй вход,устройства, переводится в режим вычисления функции синуса. В этом случае первый вход блока 3 соответствует входу цифрового синусного преобразователя, а выход блока 3 соответствует выходу преобразователя. Вычисление кода угла |J , как и вычисление квадратного корня, производится в соответствии с выыерассмотренным методом поразрядног уравновешивания с определением на каждом т-акте вычислений одной значащей цифры кода углар) , который снимается с выхода выходного регистра 6. При наличии команды Выполнение операции деления в первый входной регистр 1 заносится делимое d, а во второй входной регистр 7 делитель f. По команде, поступающей на третий вход устройства, выход второго входного регистра 7 подключается на третий вход блока-3 через коммутатор 8. По команде со второго входа устройства блок 3 переводится в режим умножения кодов. В первом такте вычислений с выхода выходного регистра б задается первое значение частного 2. в виде 011... 11. С выход блока 3 снимается произведение и сравнивается в схеме 2 сравнения со значением кода делимого d. На основании результата сравнения формируется первая значащая цифра частного. Например, при в первом разряде записывается логическая единица. Значение частного снимаетс с выхода выходного регистра б.

При наличии команды Вычисление функций sinlJ значение кода угла 0 заносится во второй входной регистр и по команде, поступившей с третьег входа устройства, через коммутатор передается на третий вход блока 3, которое по команде, поступившей со второго входа устройства переводитс в режим вычисления функции sin (Ь . Код функции считывается со второго выхода устройства.

Таким образом, с помощью предлагаемого устройства может быть осуществлено извлечение квадратного корня, выполнение операции деления, а также вычислен-ие взаимообратных функций. При этом, например, для вычисления как функции синуса, так и арксинуса, может быть использован одна таблица кода синуса, заложенна в блоке 3. Таким образом в предлагаемом устройстве расширены функциональные возможности, а именно; с его помощью можно вычислять не только квадратный корень, но и взаимообратные монотонно изменяющиеся функции и выполнять операцию за счет ввода в устройство мультиплексора и .второго входного регистра. Применение предлагаемого изобретения позволит реализовать поставленную задачу одним устройством t вместо набора устройс реализующих ту же задачу по частям) , что снизит аппаратурные затраты. Так для 12-разрядного кода функции аппаратурные затраты при реализации предлагаемого устройства используемого для осуществления сразу трех видов вычислений в режиме разделения времени, составят 68 микросхем 133 серии, что на 52 микросхемы меньше аппаратурных затрат при реализации той же задачи по частям. Формула изобретения Устройство для вычисления квадратного корня по авт. св. 611208, отличающееся тем, что, с целью расширения функциональных возможностей за счет дополнительного вычисления взаимообратных монотонно изменяющихся функций и выполнения операции деления, в него введены второй входной регистр и кoм.;yтaтop, причем второй вход устройства соединен со вторым входом постоянного запоминающего блока, третий вход которого подключен к выходу коммутатора, первый, второй и третий входы которого соединены соответственно с выходом выходного регистра, третьим, входом устройства и выходом второго входного регистра, вход которого является четвертым входом устройства, выход постоянного запоминающего устройства является вторым выходом устройства. Источники информации, принятые во внимание при экспертизе, 1. Авторское свидетельство СССР № 611208, кл. G 06 F 7/38, 1978.

Авторы

Даты

1981-06-30—Публикация

1979-11-12—Подача