(54) УСТРОЙСТВО ДД.Я ВЫЧИСЛЕНИЯ ФУНКЦИИ

y--VA VBi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ = @ + @ | 1983 |

|

SU1136153A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Устройство для вычисления полиномов | 1985 |

|

SU1277098A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

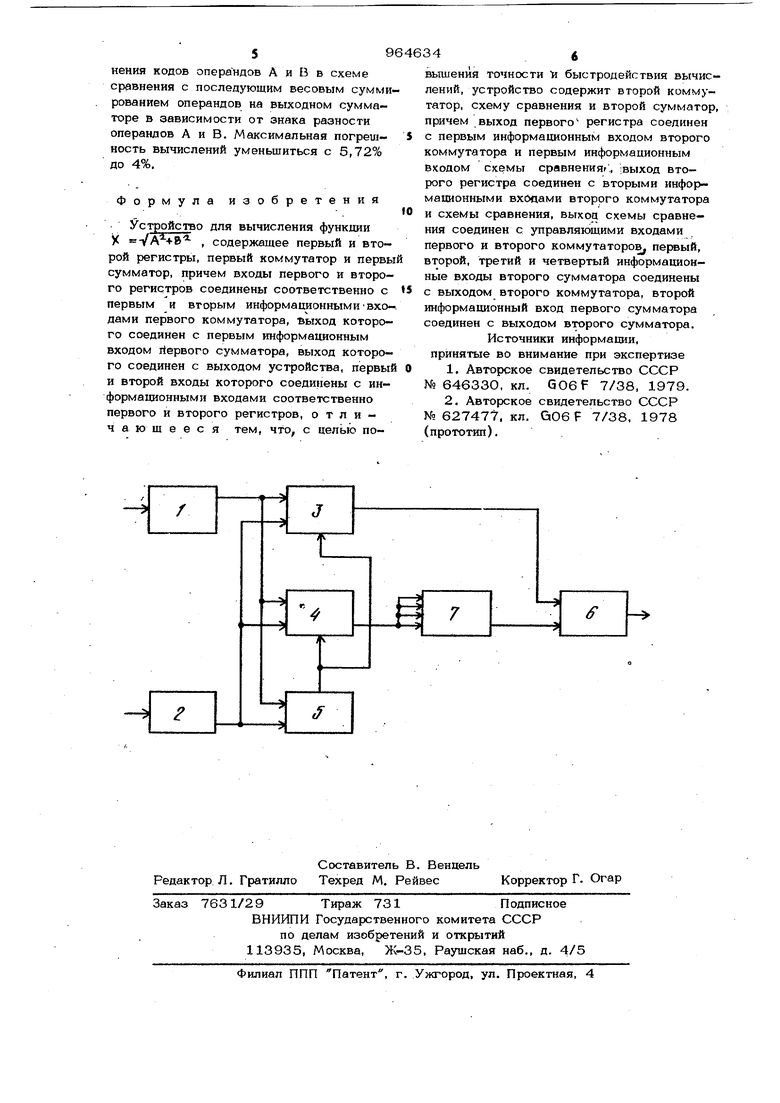

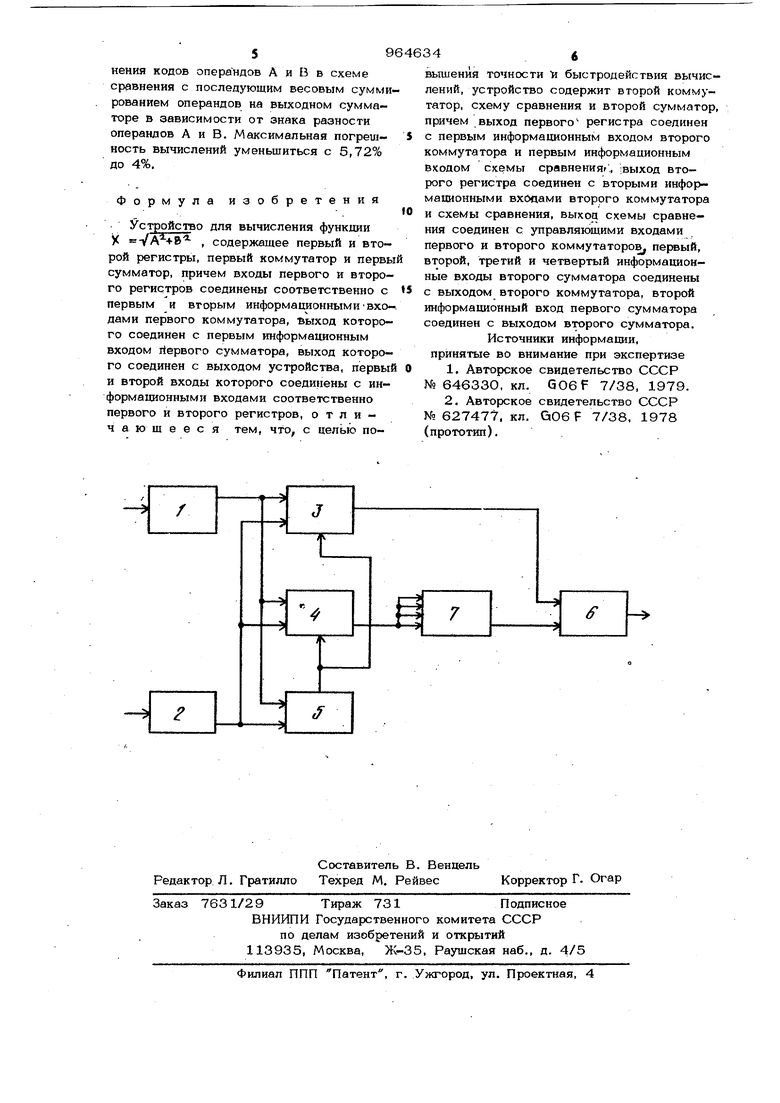

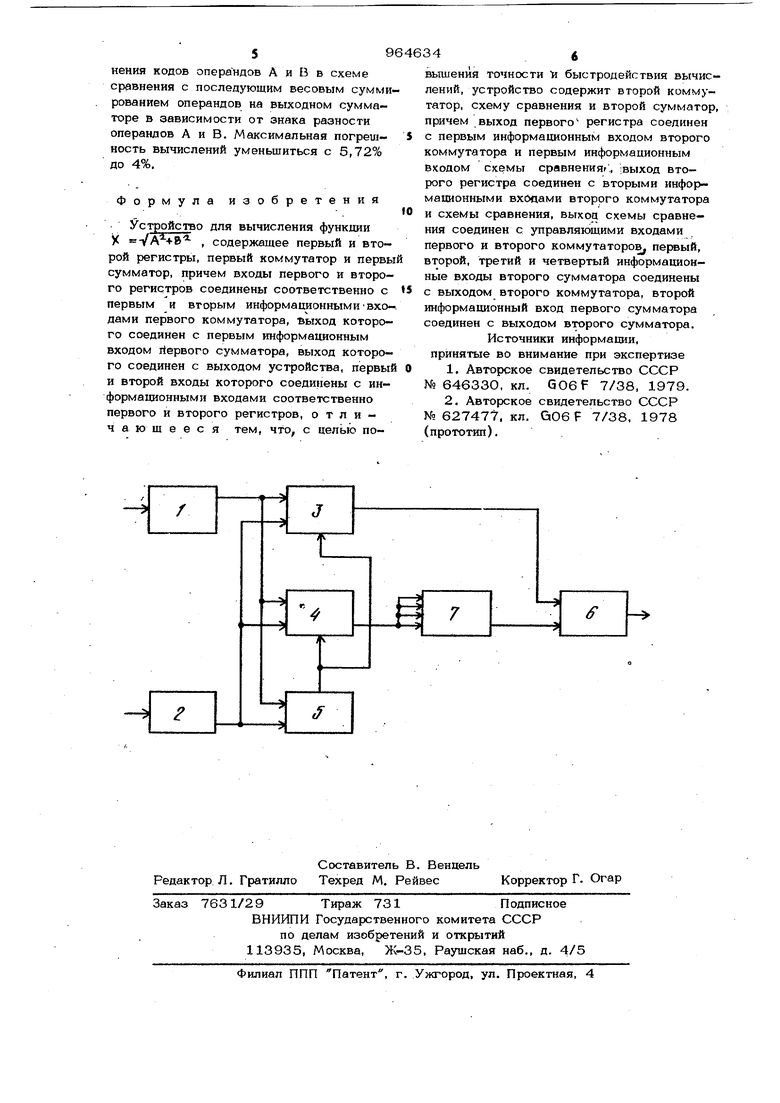

Изобретение относится к Bbt4HcnHf SR fc ной технике и может быть нспсйГьзовано в специализированных устройствах обработки информации. Известно устройство для вычисления функции У , в котором вычисление функщш производится за шжлов с вычислением за каждый цикл одной значащей результата путем выполнени в каждом цикле трех операций с разрядны ми цифрами очередных разрядов О и сшерандов А и В и содержащее блок суммирования, регистр левого сдвига на два разряда, три регистра левого сдвига на один разряд, три коммутатора, элементы ИЛИ, И и счетчик l j. Недостатком такого устройства являет ся низкое быстродействие, так как для. получения К разрядов результата необходимо выполнить И циклов вычислений, Известно также устройство для вычислешис квадратного корня из суммы квадратов двух чисел, в котором вычисление функции осуществляется путем реализации приближенной зависимости 1,5 -з; +|В| +0,5 //А/ + /В/. Г: Недостатком устройства 5авляется его низкое быстродействие. Наиболее близким к изобретению по технической сущности является устройство, содержащее распределитель импульсов, коммутатор, состоящий из группы элементов И и ИЛИ, накапливающий сумматор, элемент И и регистры операндов сдвига 23Недостатком известного устройства является низкое быстродействие, так как вычисление осуществляется за девять тактов путем последовательного вычисления разности (А) - (В) сдвига разности на один разряд вправо с последующей перезаписью значения 0,5 //А/-/В// в накапливающий сумматор и суммированием его с кодами операндов А и В, а также низкая точность вычислений, обусловленная реализацией приближенного алгоритма, .максимальная погрещность вычислений составляет 5,72%. 396 Щелью изобретения является повышение быстродействия в устройстве за счет сокращения числа тактов вычислений и повышение точности вычислений. Поставленная цель достигается тем, что в устройство для вычисления функции , , содержащее первый и второй , регистры, первый коммутатор и первый сумматор, причем выходы первого и второго регистров соединены соответственно с.первым и вторым информационными входами первого коммутатора, выход которого соединен с первым шформационным. входом первого сумматора, выход которого соединен с выходом устройства, первы и второй входы которого соединены информашюнными входами соответственно первого и второго регистров, введены второй коммутатор, схема сравнения и второй i сумматор, причем выход первого регистра соединен с первым информационным входом второго коммутатора и с первым информапионным входом схемы сравнения, -выход второго регистра соединен с вторы и информационными входами второго ком- мутатора и схемы сравнения, выход схемы сравнения соединен с управляющими входа ми лервого и второго коммутаторов, перзвый, второй, третий и четвертый информационные входы второго сумматора соединены с выходом второго коммутатора, вто рой информационный вход первого сумматора соединен с выходом второго сумматора. Устройство реализует приближённый алгоритм в соответствии с выражением . 1.04УА -1-В (А+0,4143В) при 1,04-/А В (В + 0,4143 А) при В А. Ка чертеже представлена функциональная схема устройства. Устройство содержит регистры 1 и 2, первый и второй коммутаторы 3 и 4, схе му 5 сравнения, первый и второй сумматоры 6 и 7, Выход регистра 1 соединен с первым входом коммутаторов 3 и 4 и схемы 5 сравнения. Выход регистра 2 соединен с вторым входом коммутаторов 3 и 4 и схемы 5 сравнения. Выход схемы 5 сравнения соединен с третьим входом коммутатора 3, соединен с первым входом сумматора 6, второй вход которого соединен с выходом сумматора 7, входы которого соедггаены с выходом коммутатора 4. Устройство работает следующим образом. В регистры 1 и 2 засылаются коды операндов А и В. С выходов регистров 1 и 2 коды операндов А. и В подаются на 4 соответствующие коды коммутаторов 3 и 4 и схемы 5 сравнения. В зависимости от знака равноети А -В осуществляется подключение на входы сумматора 7 или операнда А, или операнда В. При на входы сумматора 7 подается код опе ранда В,- а на выходе сумматора 7 формируется значение кода 0,4143В. Значение кода 0,4143В получается путем одновременного суммирования значений . ti.2 Ви2 Вс последующим формированием окончательного результата 0,4143 В В ( + + 2). Сдвиг операнда В вправо на требуемое число разрядов (два, три, пять и семь) осуществляется соответствующим подключением выхода коммутатора 4 на входы сумматора 7. Значение 0,4143В подается на второй вход выходного сумматора 6. На первый вход сумматора 6 в этом случае подается значение операнда А. Таким образом, на выходе сумматора 6 получаем Значение (А + 0,4143В). Получаемое на сумматоре 6 число равняется знвчанию искомой функции, помноженному на коэффициент 1,О4.. Коэффициент можно рассматривать как Масштабный и учитывать iB дальнейших вычислениях. Эффект1шность изобретения заключает- ся в повьпиении быстродействия за счет вычисления функШ1и за один такт на проходе. Это позволяет применить устройство в быстродействующих и вычислительных устройствах. Так, например, при использовании в известном устройстве тактирующих импульсов Ю мГц время вычисления функции К составит 0,9 мкс. В предложенном устройстве время вычислений вы функции составляет tTgyq СУ,сре1ВМ. сумм1 коАлм-- судлма. . . - время вычисления функции; Т ., .пч время выполнения операции с А t ср ВИ i сравнения; суллм-: Р®м выполнения операции; CVHANM суммирования в первом и втором сумматорах; .омД задержки сигнала в коммутаторе. При применении в сумматорах стандартных микросхем четырехразрядных полных сумматоров 155 ИМЗ для восьмиразрядных операндов время вычисления Сауц .0,3 МКС. Таким образом, быстродействие предложенного устройства повьппается в 3 раза. Повышена точность вычислений за счет осуществления предварительного сравнения кодов операндов А и В в схеме сравнения с последующим весовым суммированием операндов на выходном сумматоре в зависимости от знака разности операндов А и В. Максимальная погрешность вычислений уменьшиться с 5,72% до 4%.

Формула изобретения

Устройство для вычисления функции У VAHB , содержащее первый и второй регистры, первый коммутатор и первы сумматор, причем входы первого и второго регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, выход которого соединен с первым информационным входом rtepBoro сумматора, выход которого соединен с выходом устройства, первый и второй входы которого соединены с информационными входами соответственно первого и второго регистров, отличающееся тем, что, с целью повышения точности к быстродействия вычислений, устройство содержит второй коммутатор, схему сравнения и второй сумматор причем выход первого регистра соединен с первым информационным входом второго коммутатора и первым информационным Входом схемы сравненияг ;выход второго регистра соединен с вторыми инф01 мационными входами второго коммутатора и схемы сравнения, выход схемы сравнения соединен с управляющими входами первого и второго коммутаторов первый, второй, третий и четвертый информационные входы второго сумматора соединены с выходом второго коммутатора, второй информационный вход первого сумматора соединен с выходом второго сумматора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-10-07—Публикация

1981-03-02—Подача