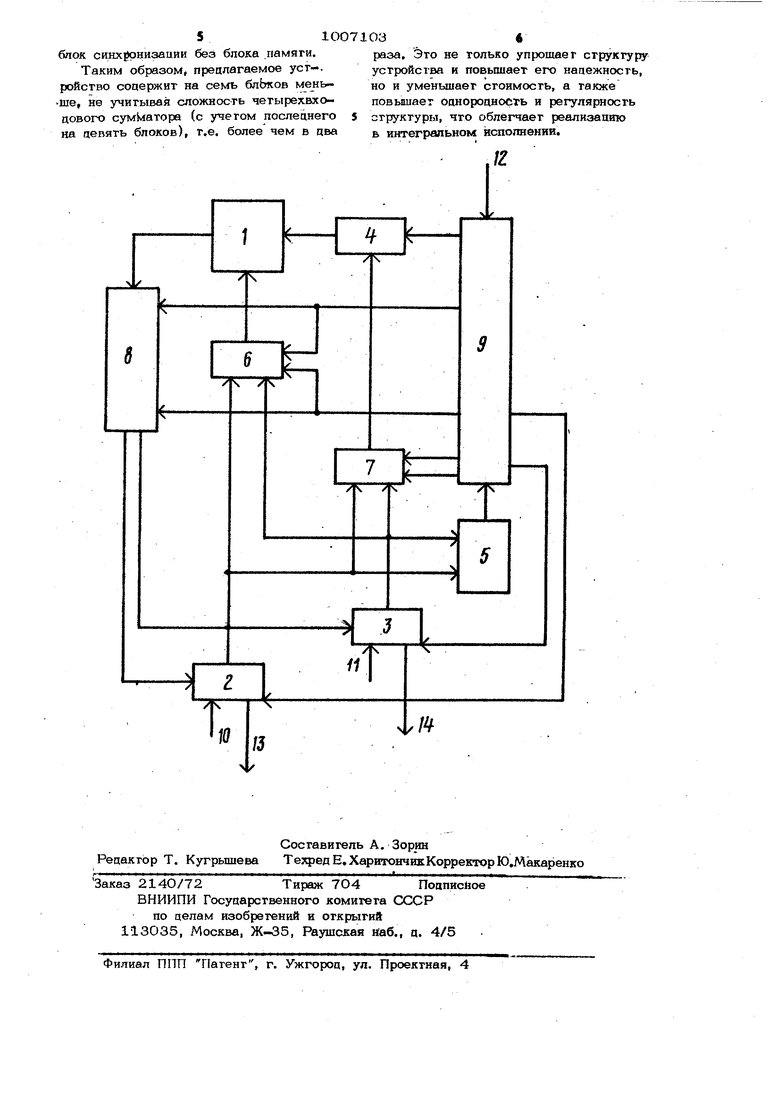

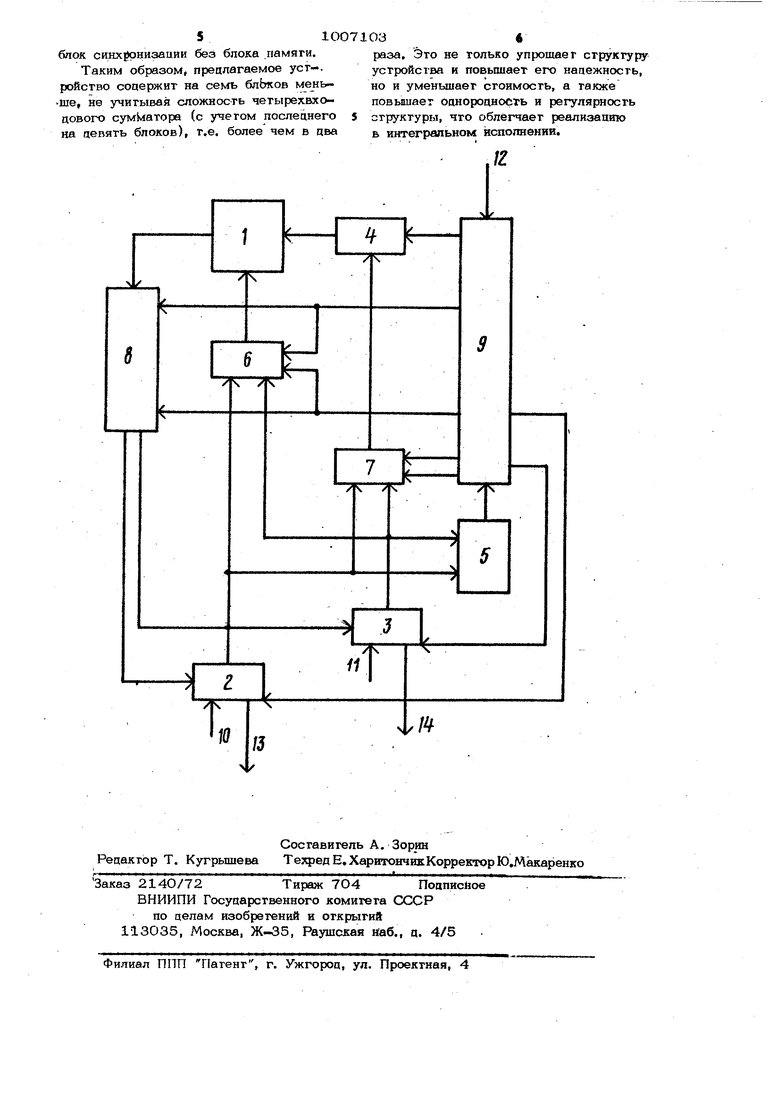

Изобретение относится к вычислител ной технике и может быть использовано аля аппаратной реализации операции вычисления квапратного корня в двоичной системе в форме с фиксированной запятой в вычислительных и управляющи системах и устройствах автоматики, телемеханики и вычислительной техники Известен вычислитель квадратного корня, содержащий однозарядные двоичн сумматоры на два и на три входа, три регистра, устройства формирования приращений на однсютороннем запоминающе устройстве, блок анализа знака и блок управления Г 1 Недостатком вычислителя является его сложность. Наиболее близким по технической сущности к предлагаемому является уст ройство для извлечения квадратного кор ня, содержащее два сумматора, регистр блок сдвига, два коммутатора, схему сравнения, блок задания знака и блок управления, причем выход блока анализа разности соединен с блоком управления, выход первого регистра через первый коммутатор соединен с первым входом первого сумматора, выход второго регистрасоединен через второй коммутатор и блок сдвига с вторым входом пер вого сумматора, первый выход блока управления соединен с блоком сдвига, агорой и третий выходы - с вторыми входами первого и второго коммутаторов соответственно 2 3 , Недостатком этого устройства являе ся его сложность, так.как аппаратурные затраты на его реализацию составляют два сумматора (причем один из них по слсишости эквивалентен трем сумматорам с двумя входами каждый), шесть регистров, два коммутатора, два логических блока и блок управления, прггчем в последний входит блок памяти. Следует отметить, что повьпяение быстродейс вия известного устройства путем пропус ка итераций с большим весом для аргументов с малыми числовыми значениями возможно только для значений, составля ющих ао 30% всех-чисел. Быстродейств для остальных 70% чисел равно в такта цля последовательных сумматоров П4 Г . а для параллельных сумматоров равно Ттах в тактах Целью настоящего изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство, .содержащее два регистра, схему сравнения, блок сдвига, блок синхронизации и сумматор, первый вход которого соединен с выходом блока сдвига, выход схемы сравнения соединен с первым входом блока синхронизации, второй вход сумматора соединен с выходом первого коммутатора, первый информационный вход которого соединен с выходом первого регистра| выход второго регистра соединен с первым информационным входом второго коммута тора, выход которого соединен с информационным входом блока сдвига, управляющий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым упра&ляюшим входом первого коммутатора, третий выход блока с ихронизаикк соединен с первым управляющим входом второго коммутатора, содержит третий коммутатор, информационный вход которого соединен с выходом сумматора, . первый и второй выходы третьего коммутатора соединены с информационными входами соответственно первого и второго регистров, входы записи которых соединены с входами соответственно тргументаи константы устройства, выходы первого и второго регистров соединены соответственно с первым и вто-f, рым входами схемы сравнения, вторые информационные входы первого и второго коммутаторов соединены соответственно с выходами второго и первого регистров, первый управляющий вход третьего коммутатора соединей с вторым выходом блока синхронизации, четве{ тый выход которого соединен с вторыми управляющими входами первого и третьего коммутаторов, управляющие входы первого и второго регистров соединенысоответственно с пятым и щестым выходами блока синхронизации, седьмой выход которого соединен с вторым упправляюшим входом второго коммутатора, вход запуска блока сшгхронизации соединен с входом стартового импульса устройства. На чертеже приведена структурная схема устройства для вычисления квадратного корня. Устройство для вычисления квадратного корня содержит сумматор 1, регистры 2 и 3, блок 4 сдвига, схему 5 сравнения, коммутаторы 6-8, блок 9 синхронизации, входы 10 и 11 регистров. вход 12 запуска блока синхронизации, выхрцы 13 и 14 устройства. Ввшисление квацрагного корня в данном устройстве осуществляется по следующему алгоритму из системы разностных рекуррентных соотношений в интерационном процессе , .Y4jj n v- vW)при Zj , где э 0,п - порядковый номер итерации М - число разрядов кода аргумента X С и (ц,- - прямой и обратный код: сигнала сравнения значений Zj и Xj, V -h ) 2 коэффициент V /коррекции ре зультата. Вычисление квадратного корня в устройстве осуществляется следующим образом. Первоначально в регистр 2 заносится значение константы l/K равное, например, 0,4195248, в регистр 3 заносится значение аргумента X. На вход 12 подается стартовый импульс, по котором производится сравнение значений в регистрах 2 и 3 соответственно и запускается генератор тактовых импуль- сов в блоке 9 синхронизации. По результатам сравнения значений ZQ и XQ (по значению цифры ) в блоке 9 синхронизации производится формирование управ ляющих сигналов с второго, третьего, че вертого и седьмого выходов. Например, при значение Z о через коммутатор 7 переписывается в блок 4 сдвига и сдвигается на один разряд тактовым импульсом сдвига с первого входа блока, затем сдвинутое значение ZQ с выхода блока 4 сдвига и значение 2 с выхода регистра 2 при помощи импульсов продвижения с первого и пятого выходов блока синхронизации заносятся в однозарядный сумматор 1. Результаты суммирования с выхода сумматора 1 через коммутатор 6 заносятся младшими разрядами вперед в освобождающиеся i. при продвижении старшие разряды регистра 2 и сдвигаются к его началу. В конце первой итерации в регистре 2 записано значение Z . В регистре 3 остается значение XQ- В конце итерации определяется значение цифры с для следующей итерации. Если , то вышеописанный процесс повторяется. Если , то значен.ю 2 остается в регистре 2, значение залисывается через коммутатор 7 в блок 4 двига, где производится его сцви1г на . два разряда. Затем значения из блока 4 двига и регистра 3 продвигаются в сумматор 1, результаты итерации с выхода последнего записываются через коммутатор 8 младшими разрядами вперед в освобождающиеся при продвижении старшие разряды регистра 3 и сдвигаются к его началу. В конце второй итерации в регистре 3 записано значение Хл, а в .ч..-ч- регистре 2 записано значение2п 2. Цикл вычисления состоит изп игераций, каж. дая из которых выполняется за п тактов, поскольку в итерации выполняется только одно сложение и один сдвиг. В последней h -и итерации в регистрах 2 и 3 содержится значение квадрат ного корня из заданного аргумента X. В общем случае погрешность вычис- ления определяется длиной разрядной сетки и лри введении m дополнительных защитных разрядов всегда меньше единицы последнего младшего разряда п , где т дополнительных защитных разрядов регистров, блока сдвига и сумматора для компенсации погрешности усечения чисел при их сдвиге за пределы разрядной сетки. Время вычисления квадратного корня в данном устройстве для последовательнего принципа вычисления (с последовательным однозарядным сумматором) равно в тактах j(n+) ги-пп + Время вычисления квадратного корня в данном устройстве для параллельного принципа вычисления (с параллельным сумматором и матричным сдвигателсм) равно в тактах . По сравнению с известным предлагаемое устройство значительно проще, поскольку для реализации известного устройства требуется два сумматора (один из которых является четырехвходовым, что эквивалентно трем двухвходовым сумматорам), шесть регистров, два коммутатора, два логических блока и блок управления, в который входит блок памяти. Для реализации данногЪ устройства .требуется один двухвходовый сумматор, два регистра, два коммутатора, один логическийблок и простой

(шок синх1 онизаиии без блока памяги.

Таким образом, преплагаемое уст-.

ройство соцержит на семь блЬков меньше, не учитывая сложность четырехвхоцового сумматора (с учетом послецнего

на девять блоков), т.е. более чем в два

раза. Это не только упрощает структуру устройства и повьпиает его надежность, но и уменьшает стоимость, а также повышает оцнородность и регулярность структуры, что облегчает реализацию в интегральном исполнении.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1024914A1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее два регистра, два коммутатора, схему сравнения, блок сдвига, блок синхронизации и сумматор, первый вход которого соединен с выходом блока сдвиге, выход схемы сравнения соединен с первым Ьходомбпока скнхронизации, второй вход сумматора - с выходом пер;вого коммутатора, пе1юый йнформацион- :ный вход которого соединен с выходом первого регистра, выход второго регистра соединен с первым информационным входом второго KOMMyTaTopia, выход которого соединен с информационным входом блока сдвига, управляющий вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым управляющим ;Входом первого коммутатора, третий выход блока синхронизации соединен с первым управляющим входом второго коммутатора, отличающееся тем, что, с целью гпрощения, оно содержит третий коммутатор, информационный .вход которого соединен с выходом сумматора, первый и второй выходы третьего коммутатора соединены с инфор 1а1исш- ными входами соответственно первого и второго регистров, входы записи которых соединены с входами соответственно аргумента и константы устройства, выхо ды первого и второго .регистров соединены соответственно с первым и вторым входами схемы сравнения, вторые, информ мационные входы первого и второго комi мутаторов соединены соответственно с выходами второго и первого регистр, первый управляющий вход третьего коммутатора соединен с вторым выходом блока синхронизации, четвертый выход которого соединён с вторыми управляю- щими входами первого и третьего комму-i та торов, управляющие входы первого и. второго регистров соединены соотэетст- веяно с пятым и щестым выходами ка синхронизации, седьмой выход кото рого соединен с вторым управляющим о входом второго коммутатора, вход заОР :пуска блока синхронизации соединен с входом стартового импульса , ройства.

/ч / V

т

W

/J

/

У. /V

4

IJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Теория и примеяение математических машин, Минск,иад-во БГУ, 1972, с | |||

| Деревянное стыковое устройство | 1920 |

|

SU163A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU732863A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-03-23—Публикация

1981-04-21—Подача