(54) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1979 |

|

SU847279A1 |

| Цифровой интегратор | 1976 |

|

SU720427A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОБУЧЕНИЕМ И ОЦЕНИВАНИЕМ ЗНАНИЙ ОБУЧАЮЩИХСЯ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2011 |

|

RU2467388C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

1

Изобретение относится к цифровой вычислительной технике и может найти применение в устройствах программного управления.

Известно устройство, содержащее блок подынтегральной функции, выходной блок, блок итераций, програмный блок, состоящий нз регистра сдвига, сумматора, элемента задержки 1.

Недостаток устройства - больпше затраты на оборудование.

Наиболее близок предлагаемому по технической сущности цифровой интегратор, содежащий блок подьштегральной функции, блок итераций, сдвиговый регистр, сумматор, элемент задержки, элементы И 21.

Недостатком интегратора является низкое быстродействие.

Цель изобретения - повьпиение быстродейгтвия.

Указанная цель достигается тем, что в цифровой интегратор, содержащий блок памяти, первый разрядный выход которого соединен с первым прямым входом трехвходового элемента И, второй прямой вход коiTOporo соединен с первым выходом сумматора и вторым разрядным выходом блока памяти, инверсный вход трехвходового элемента И подключен к первому входу сумматора, второй, выход которого через первый элемент задержки соединен с прямым входом двухвходового элемента И, инверсный вход которого соединен с первым выходом генератора и вторым входом сумматора, выход двухвходового элемента И подключен к третьему входу сумматора, введены счетчик, второй элемент задержки и элемент НЕ, причем вход элемента НЕ соединен .с первым выходом сумматора, а выход через второй элемент задержки - с установочным входом счетчика, управляющий вход которого соединен со вторым выходом генератора, выход счетчика подключен к адресному входу блока памяти, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами генератора.

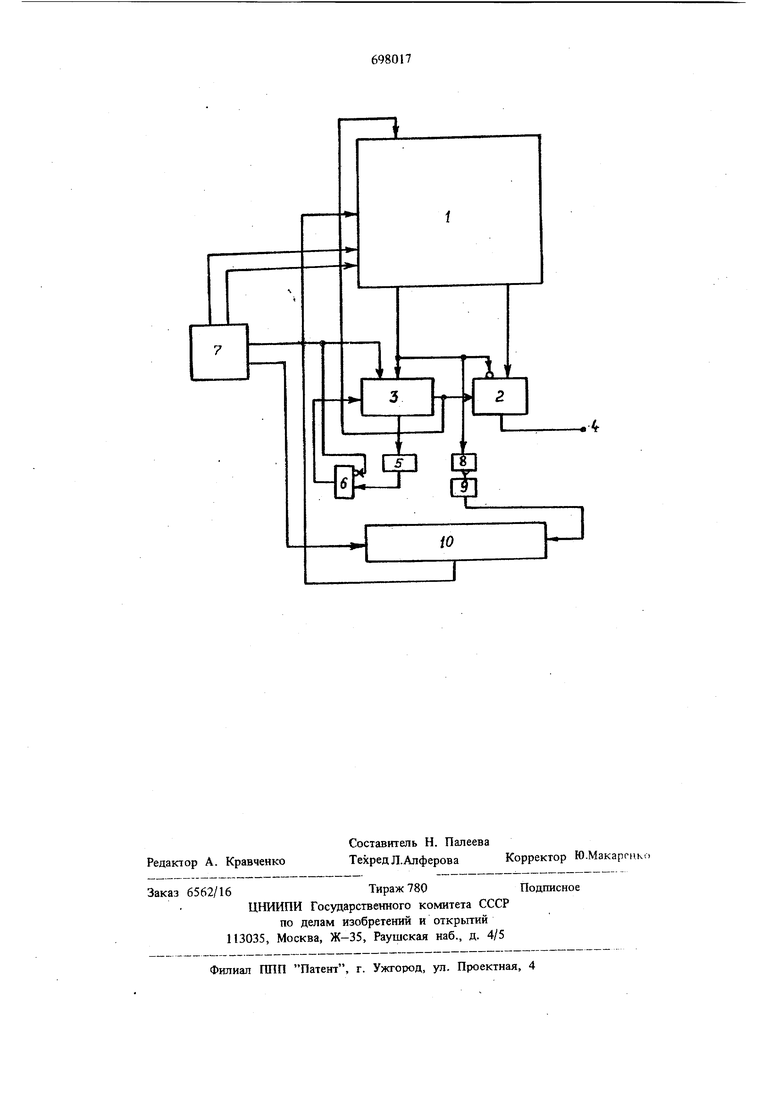

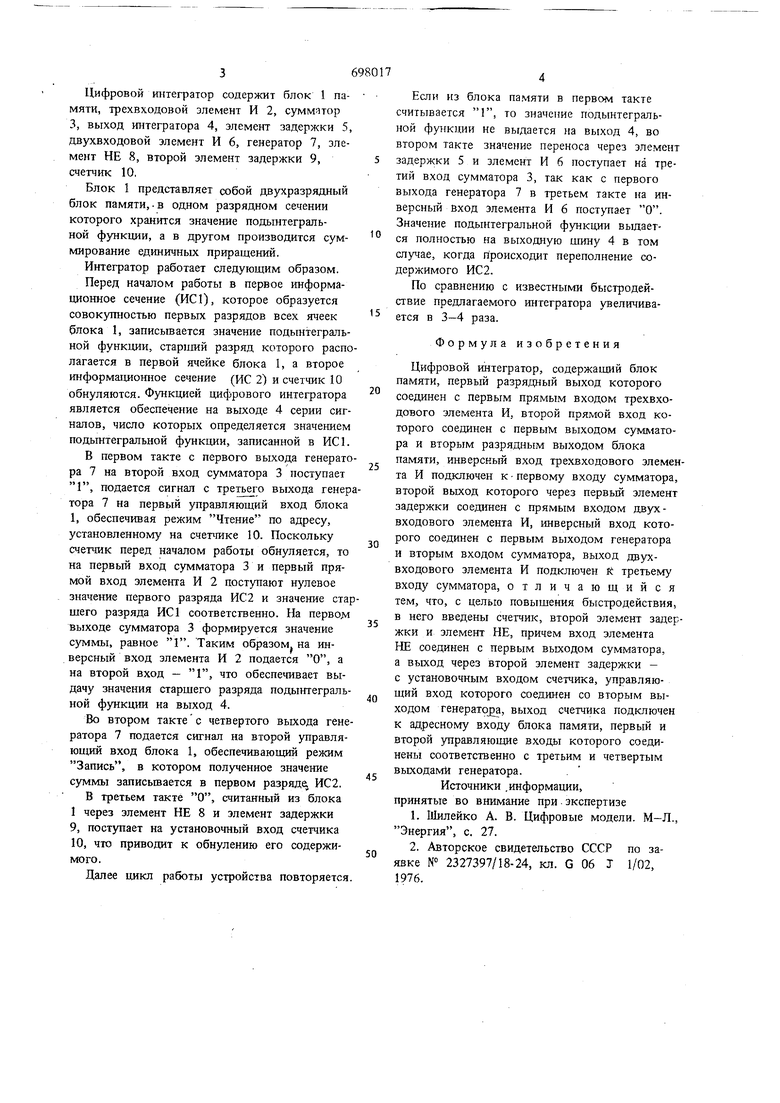

На чертеже изображена блок-схема предлагаемого интегратора. Цифровой интегратор содержит блок 1 памяти, трехвходовой элемент И 2, сумматор 3, выход mirerparopa 4, элемент задержки 5, двухвходовой элемент И 6, генератор 7, элемент НЕ 8, второй элемент задержки 9, счетчик 10. Блок 1 представляет собой двухразрядный блок памяти, в одном разрядном сечении которого хранится значение подынтегральной функции, а в другом производится суммирование единичных приращений. Интегратор работает следующим образом. Перед началом работы в первое информационное сечение (ИС1), которое образуется совокупностью первых разрядов всех ячеек блока 1, записьгеается значение подынтегральной функции, старишй разряд которого распо лагается в первой ячейке блока 1, а второе информационное сечение (ИС 2) и счетчик 10 обнуляются. Функцией цифрового интегратора является обеспечение на выходе 4 серии сигналов, число которых определяется значеьшем подынтегральной функции, записанной в ИС1. В первом такте с первого выхода генерато ра 7 на второй вход сумматора 3 поступает 1, подается сигнал с третьего выхода генер тора 7 на первый управляющий вход блока 1, обеспечивая режим Чтение по адресу, установленному на счетгшке 10. Поскольку счетчик перед началом работь обнуляется, то на первый вход сумматора 3 и первый прямой вход элемента И 2 поступают нулевое значение первого разряда ИС2 и значение ста щего разряда ИС1 соответственно. На первод выходе сумматора 3 формируется значение суммы, равное 1. Таким образом, на инверсный вход элемента И 2 подается О, а на второй вход - 1, что обеспечивает выдачу значения старшего разряда подынтеграль ной функции на выход 4. Во втором тактес четвертого выхода гене ратора 7 подается сигнал на второй управляющий вход блока 1, обеспечивающий режим Запись, в котором полученное значение суммы записьшается в первом разряде; ИС2. В третьем такте О, считанный из блока 1 через элемент НЕ 8 и элемент задержки 9,поступает на установочный вход счетчика 10,что приводит к обнулению его содержимого. Далее цикл работы устройства повторяется Если из блока памяти в первом такте считывается 1, то значение подьштегральной функции не выдается на выход 4, во втором такте значение переноса через элемент задержки 5 и элемент И 6 поступает на третий вход сумматора 3, так как с первого выхода генератора 7 в третьем такте на инверсный Вход элемента И 6 поступает О. Значение подынтегральной функции вьщается полностью на выходную шину 4 в том случае, когда происходит переполнение содержимого ИС2. По сравнению с известными быстродействие предлагаемого интегратора увеличивается в 3-4 раза. Формула изобретения Цифровой интегратор, содержащий блок памяти, первый разрядный выход которого соединен с первым прямым входом трехвходового элемента И, второй прямой вход которого соединен с первым выходом сумматора и вторым разрядным выходом блока памяти, инверсный вход трехвходового элемента И подключен к-первому входу сумматора, второй выход которого через первый элемент задержки соеддгаен с прямым входом двухвходового элемента И, инверсный вход которого соединен с первым выходом генератора и вторым входом сумматора, выход двухвходового элемента И подключен К третьему входу сумматора, отличающийся тем, что, с целью повышения быстродействия, в него введены счетчик, второй элемент задержки и элемент НЕ, причем вход элемента НЕ соединен с первым выходом сумматора, а выход через второй элемент задержки - с установочным входом счетчика, управляющий вход которого соединен со вторым выходом reHepaToj a, выход счетчика подключен к адресному входу блока памяти, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами генератора. Источники .информации, принятые во внимание при экспертизе 1.Шилейко А. В. Цифровые модели. М-Л., Энергия, с. 27. 2.Авторское свидетельство СССР по заявке № 2327397/18-24, кл. G 06 Т 1/02, 1976.

Авторы

Даты

1979-11-15—Публикация

1978-03-13—Подача