1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения наладочных запоминающих устройств с вычислительными машинами.

Известны устройства для сопряжения абонентов с ЦВМ, содержащие память команд, регистр команд, блоки коммутации, блок памяти, регистр управления выдачей, дешифратор адреса, адресные регистры, блоки сравнения, блоки приема и выдачи Ш. ,

Недостаток этих устройств состоит в больших аппаратурных затратах.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения вычислительных машин, содержащее блок динамической памяти, первые и вторые входы и выходы которого являются соответственно первыми и вторыми входами и выход 1ми устройства, третьи вход и выход - подключены к соответствующим входу и выходу регистра команд, четвертые вход и .выход - соответственно к первому входу и выходу блока сравнения адресов, вторым входом соединенного через блок приема адреса к третьему входу устройства, а третьим входс к выходу регистра адреса и первому входу блока передачи данных, вторым и третьим входами подключенный соответственно к пятому выходу блока динамической памяти и выходу буферного регистра, выходом - с соответствующим выходом устройства и входом блока приема, соединенным выходом и входом к соответствующим входам 10 и выходам блока динамической памяти 21.

Недостаток такого устройства состоит в сложности и больших затратах оборудования. Кроме того, обработка временных диаграмм работы

на стыках производится в независимых циклах последовательно по специальным сигнсШсШ запросов и ответов, что делает невозможным сопряжение 20 вычислительной машины с наладочным запоминающим устройством,подменяющим отлаживаемое долговременное запоминающее устройство вычислительной машины.

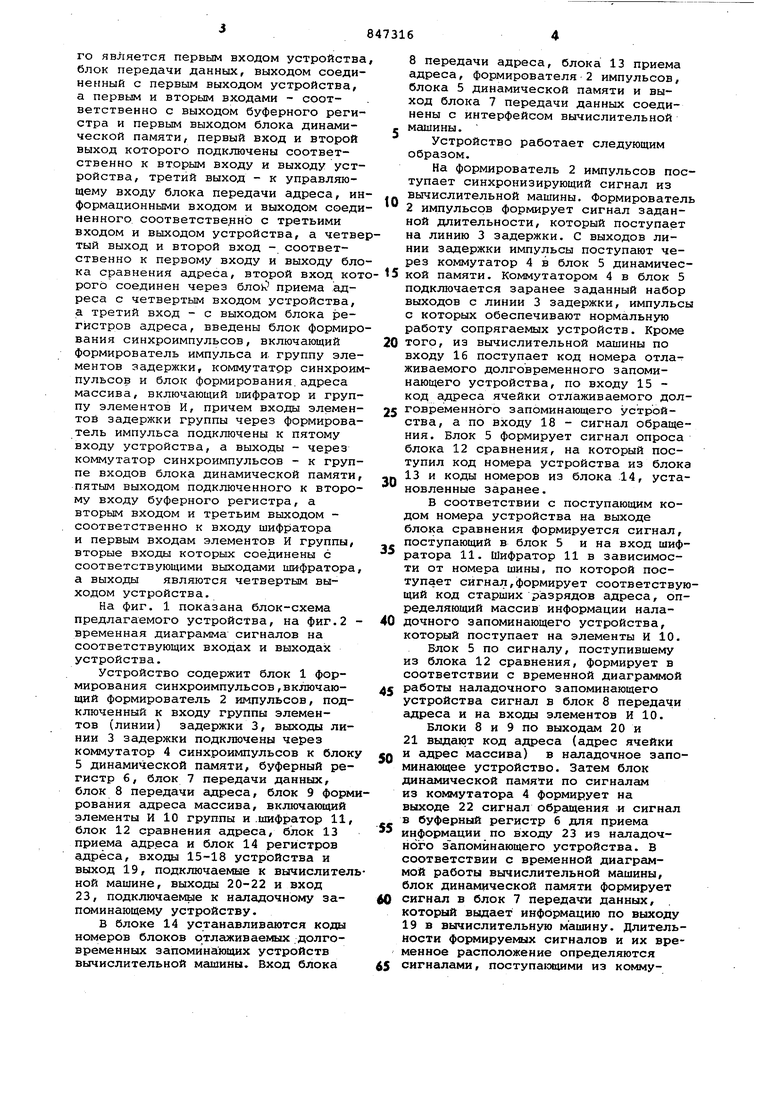

25 Цель изобретения - сокращение объема оборудования .и упрощение устройства.

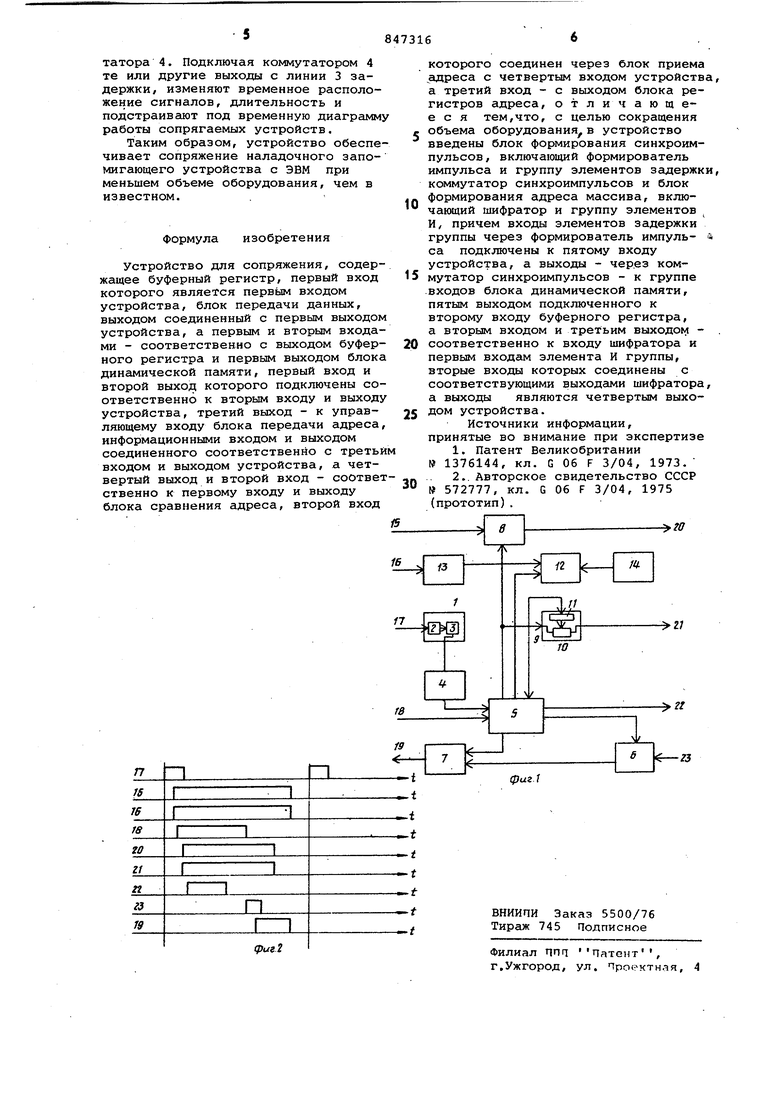

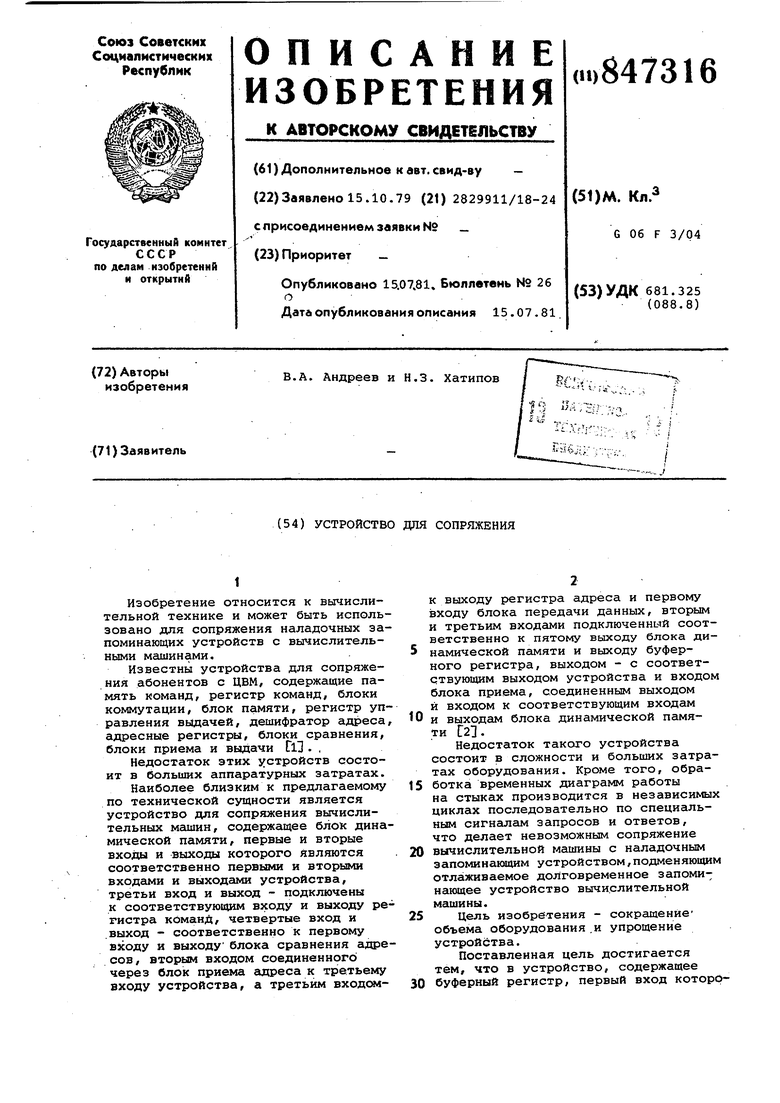

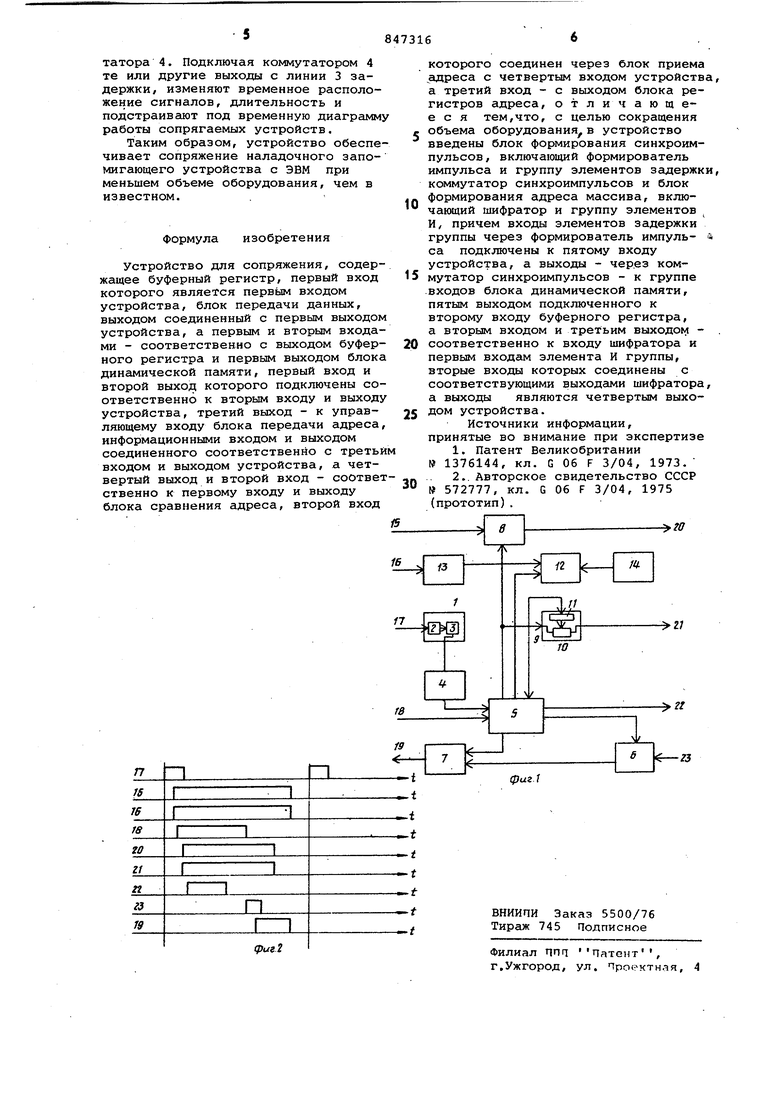

Поставленная цель достигается тем, что в устройство, содержащее 30 буферный регистр, первый вход которрго является первым входом устройства блок передачи данных, выходом соединенный с первым выходом устройства, а первым и вторым входами - соответственно с выходом буферного регистра и первым выходом блока динамической памяти, первый вход и второй выход которого подключены соответственно к вторым входу и выходу устройства, третий выход - к управляющему входу блока передачи адреса, ин формационными входом и выходом соеди ненного соответственно с третьими входом и выходом устройства, а четве тый выход и второй вход - соответственно к первому входу и выходу бло ка сравнения адреса, второй вход кот рого соединен через бло приема адреса с четвертым входом устройства, а третий вход - с выходом блока регистров адреса, введены блок формиро вания синхроимпульсов, включающий формирователь импульса и группу элементов задержки, коммутатор синхроим пульсов и блок формирования.адреса массива, включающий ишфратор и группу элементов И, причем входы элементов задержки группы через формирователь импульса подключены к пятому входу устройства, а выходы - через коммутатор синхроимпульсов - к группе входов блока динамической памяти пятым выходом подключенного к второму входу буферного регистра, а вторым входом и третьим выходом соответственно к входу шифратора и первым входам элементов И группы/ вторые входы которых соединены с соответствующими выходами шифратора а выходы являются четвертым выходом устройства. На фиг. 1 показана блок-схема предлагаемого устройства, на фиг.2 временная диаграмма сигналов на соответствующих входах и выходах устройства. Устройство содержит блок 1 формирования синхроимпульсов,включающий формирователь 2 импульсов, подключенный к входу группы элементов (линии) задержки 3, выходы линии 3 задержки подкдпочены через коммутатор 4 синхроимпульсов к блок 5 динамической памяти, буферный регистр б, блок 7 передачи данных, блок 8 передачи адреса, блок 9 форм рования адреса массива, включающий элементы И 10 группы и .шифратор 11, блок 12 сравнения адреса, блок 13 приема адреса и блок 14 регистров адреса, входы 15-18 устройства и выход 19, подключаемые к вычислител ной машине, выходы 20-22 и вход 23, подключаемые к наладочному заП(1инающему устройству. В блоке 14 устанавливаются коды номеров блоков отлс1живаемых долговременных запоминающих устройств вычислительной машины Вход блока 8 передачи адреса, блока 13 приема адреса, формирователя 2 импульсов, блока 5 динамической памяти и выход блока 7 передачи данных соединены с интерфейсом вычислительной машины. Устройство работает следующим образом. На формирователь 2 импульсов поступает синхронизирующий сигнал из вычислительной машины. Формирователь 2 импульсов формирует сигнал заданной длительности, который поступает на линию 3 задержки. С выходов линии задержки импульсы поступают через коммутатор 4 в блок 5 динамической памяти. Коммутатором 4 в блок 5 подключается заранее заданный набор выходов с линии 3 задержки, импульсы с которых обеспечивают нормальную работу сопрягаемых устройств. Кроме того, из вычислительной машины по входу 16 поступает код номера отла живаемого долговременного запоминающего устройства, по входу 15 код адреса ячейки отлаживаемого долговременного запоминающего устройства, а по входу 18 - сигнал обращения. Блок 5 формирует сигнал опроса блока 12 сравнения, на который поступил код номера устройства из блока 13 и коды номеров из блока 14, установленные заранее. В соответствии с поступающим кодом номера устройства на выходе блока сравнения формируется сигнал, поступающий в блок 5 и на вход шифратора 11. Шифратор 11 в зависимости от номера шины, по которой поступает сигнал,формирует соответствующий код старших разрядов адреса, определяющий массив информации наладочного запоминающего устройства, который поступает на элементы И 10. Блок 5 по сигналу, поступившему из блока 12 сравнения, формирует в соответствии с временной диаграммой работы наладочного запоминающего устройства сигнал в блок 8 передачи адреса и на входы элементов И 10. Блоки 8 и 9 по выходам 20 и 21 выдают код адреса (адрес ячейки и адрес массива) в наладочное запоминающее устройство. Затем блок динамической памяти по сигналам из коммутатора 4 формирует на выходе 22 сигнал обращения и сигнал в буферный регистр 6 для приема информации по входу 23 из наладочного запомйнающего устройства. В соответствии с временной диаграммой работы вычислительной машины, блок динамической памяти формирует сигнал в блок 7 передачи данных, . который выдает информацию по выходу 19 в вычислительную машину. Длительности формируемых сигналов и их временное расположение определяются сигналами, поступающими из коммутатора 4. Подключая коммутатором 4 те или другие выходы с линии 3 задержки, изменяют временное расположение сигналов, длительность и подстраивают под временную диаграмму работы сопрягаемых устройств.

Таким образом, устройство обеспечивает сопряжение наладочного запомигающего устройства с ЭВМ при меньшем объеме оборудования, чем в известном.

Формула изобретения

Устройство для сопряжения, содержащее буферный регистр, первый вход которого является первым входом устройства, блок передачи данных, выходом соединенный с первым выходом устройства, а первым и вторым входами - соответственно с выходом буферного регистра и первым выходом блока динамической памяти, первый вход и второй выход которого подключены соответственно к вторым входу и выходу устройства, третий выход - к управляющему входу блока передачи адреса, информационными входом и выходом соединенного соответственно с третьи входом и выходом устройства, а четвертый выход и второй вход - соответственно к первому входу и выходу блока сравнения адреса, второй вход

которого соединен через блок приема адреса с четвертым входом устройства, а третий вход - с выходом блока регистров адреса, отличающееся тем,что, с целью сокращения объема оборудования в устройство введены блок формирования синхроимпульсов , включающий формирователь импульса и группу элементов задержки, коммутатор синхроимпульсов и блок формирования адреса массива, вклю0чающий шифратор и группу элементов И, причем входы элементов задержки группы через формирователь импульса подключены к пятому входу устройства, а выходы - через ком5мутатор синхроимпульсов - к группе входов блока динамической памяти, пятым выходом подключенного к второму входу буферного регистра, а вторым входом и третьим выходом 0соответственно к входу шифратора и первым вхояэм элемента И группы, вторые входы которых соединены с соответствующими выходами шифратора, а выходы являются четвертым выходом устройства.

5

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании № 1376144, кл. G 06 F 3/04, 1973.

2.. Авторское свидетельство СССР

0 572777, кл. G 06 F 3/04, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения | 1981 |

|

SU1121667A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Система для сопряжения терминалов с вычислительной машиной | 1987 |

|

SU1529232A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Авторы

Даты

1981-07-15—Публикация

1979-10-15—Подача