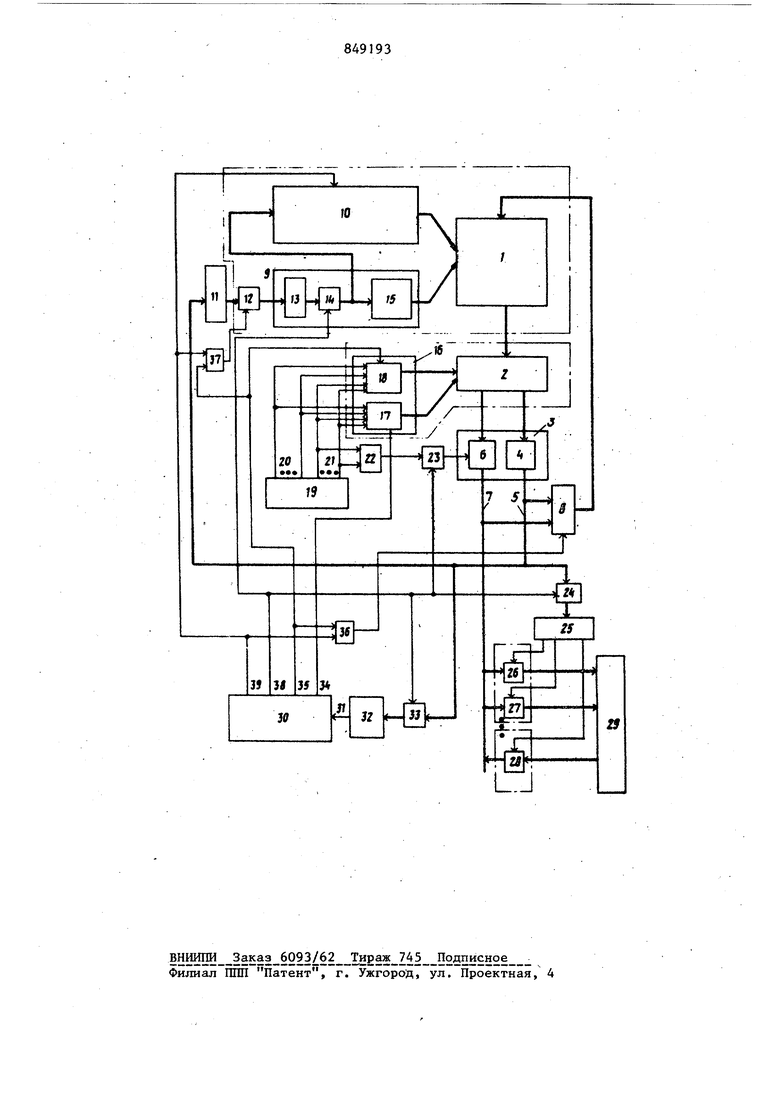

Изобретение относится к вычислительной технике и может быть использовано при построении специапизирова ных мини-ЦВМ для управления технолог ческим оборудованием, например станками с программным управлением. Известны устройства обмена информ цией между ЦВМ и объектом управления в которых функции регистров связи выполняют ячейки накопителя.. Обращение к ним производится через блок выборки, сигналом с каждого из выход которого возбуждается очередная ячей ка из группы (Лшксированных ячеек. Высокая помехоустойчивость данного устройства достигается за счет испол зования внешних устройств (JY) с дин мической памятью, информация в которых периодически обновляется под управлением блока выборки ij. Недостатком таких устройств является ограниченность возможностей по варьированию количеством и составом ВУ, обусловленная жесткостью соединений выходов блока выборки с ключами коммутаций, а также тем, что количество ВУ ограничено сверху количеством ячеек накопителя, выполняющих функции регистров связи. Последнее обстоятельство, а также то, что блок выборки должен управлять последовательностью опроса этих ячаеек, обусловливает другой недостаток - сложность блока выборки при большом количестве ВУ. Наиболее близким к предлагаемому по технической сущности является устройство для обмена информацией, содержащее накопитель, имеющий две группы ячеек, дешифраторы адреса считывания и записи, выходы которых подключены к адресным входам первой группы . ячеек накопителя, усилители считывания , входы которых подключены к разрядным шинам накопителя, а выходы подключены к числовой магистрали, регистр адреса, выходы которого подклю чены через первые ключи ко входу дешифратора считывания, а входы подключены к адресному полю числовой магистрали, блок выборки ячеек второй группы, выходы которого подключены к адресным шинам ячеек второй группы регистр регенерации, входы которого подключены к разрядным шинам записи накопителя, ключи коммутации, включенные между информационным полем числовой магистрали и узлом сопряжения, блок запросов на обмен, выходы которого подключены ко входам блока выборки ячеек второй группы, дешифратор, выходы которого подключены к управляющим входам ключей коммутации а входь через вторые ключи подключены к адресному полю числовой магистрали, блок управления, первый выход которого соединен со входом считыван блока выборки ячеек второй группы, т тий выход подключен к управляющим BX дам дешифратора считывания и вторых ключей, четвертьй выход подкгаочен к управляющим входам дешифратора запис регистра регенерации и первых ключей Такая структура обладает широкими возможностями для варьирования числом ВУ при постоянном и небольшом количестве выходов блока обращения к накопителю. Так как обеспечивается свободная адресация регистров связи в качестве которых используюся ячейки первой группы. В то же время кажд ячейка первой группы используется для хранения очередного адреса из поля адресов, соответствуюшего ей. Э дает возможность задавать программно как размеры поля свяяи ячеек, так и расположение его в накопителе. Общее количество ячеек первой Ipynnbi огран чивает количество полей, что составляет широкие возможности дця варьирования числом ВУ Г23. - Недостатком известного устройства является низкое быстродействие, так как обмен одним словом производится за два обращения к накопителю. В пер вом обращении производится извлечени из второй группы ячеек накопителя очередного адреса ячейки связи. Во втором обращении производится считы вание по данному адресу из первой группы ячеек накопителя ячейки связ Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем что в устройство, содержащее первый 4 блок памяти, соединенный информационным входом с выходом регистра регенерации, адресным входом - с выходом регистра адреса, входом управления считыванием - с первым выходом, блока синхронизации, входом управления записью - со вторым выходом блока синхронизации, а информационным выходом - с информационньм входом второго блока памяти, информационный выход которого соединен через блок усилителей адресного поля с первым информационным входом регистра регенерации, через блок усилителей информационного поля со вторым информационньм входом регистра регенерации, информационным входом коммутатора вывода и информационным выходом коммутатора ввода, входы управления записью и считыванием второго блока памяти подключены соответственно к третьему и четвертому выходам блока синхронизации, а адресные входы - к соответствующим выходам блока формирования запросов на обмен и входом первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выходом подключенного к управлянмцему входу блока усилителей информационного поля а вторым входом - к первому выходу блока синхронизации и первому входу второго элемента И, второй вход и выход которого соединены соответственно с выходом блока усилителей адресного поля и :входом: дешифратора, выходы которого подключены к соответствующим адресным входам коммутаторов ввода и вывода, информационные входы коммутатора ввода и информационные выходы коммутатора вывода соединены с соответствующими входами и выходами блока согласования с объектом, введены второй и третий элементы ИЛИ, группа элементов И и дешифратор нуля, причем входы второго и третьего элементов ИЛИ соединены соответственно со вторым и третьим выходами блоков синхронизации, а выходы - соответственно с синхронизирующими входами первого блока памяти и регистра регенерации, первый информационный вход которого соединен со входом регистра адреса и первыми входами элементов И группы, вторые входы которых подключены к первому выходу блока синхронизации, а выходы - ко входам дешифратора нуля, выходом соединенного со входом блока синхронизации. На чертеже изображена блок-схема предлагаемого устройства обмена информацией. Устройство содержит на.копители 1 и 2. Ячейки накопителя 1 выполниют функции регистров связи. Ячейки накопителя 2 предназначены для хранения начальнь1х адресов массивов ячеек обмена, расположенных в ячейках накопителя 1. Разрядные шины накопителя 2 подключены ко входам группы 3 блоков усилителей, блока 4 усилителей адресного поля, информационные выходы которого подключены к шинам 5 адресного поля числовой магистрали, и- блока 6 усилителей информационного поля, информационные выходы которого подключены к шинам 7 информационного поля числовой магистрали. Информационные шины 7 и адресные шины 5 числовой магистрали подключены ко входам регистра 8 регенерации, выходы дешифраторов 9 считывания и дешифраторов 10 записи подключены к адресным входам накопителя 1. Регистр 11 адреса через коммутатор 12 соединен со входом дешифратора 9 считывания, включающего дешифратор 13 первой ступени, коммутатор 14 и дешифратор 15 второй ступени. Совокупность накопителя 1, дешифр торов 9 и 10 и коммутатора 12 образует первый блок .памяти. Второй блок памяти состоит из накопителя 2 и бло ка 16 выборки, включающего узел 17 считывания и узел 18 записи,. Входь узлов 17 и 18 подключены к выходам блока 19 формирования запросов на обмен. Каждому выходу блока 19 соответствует единственная ячейка накопителя 2. Выходы 20 блока 19 соответствуют запросам на вывод информации из накопителя в приемники информации. Выходы 21 блока 19 соответствуют запросам на прием информации от источников в накопитель, при этой они подключены ко входам первог элемента ИЛИ 22, выход которого подк лючен к первому входу первого элемен та И 23. Шины 5 адресного поля числовой магистрали подключены к информационным входам второго элемента И 24,. выходы которого подключены ко входам дешифратора 25. Выходы дешифратора 2 ;подкл1рчены к адреснь1м входам ключей 26 и 27 коммутатора вывода и ключей 28 коммутатора ввода. Ключи 26 и 27 предназначены для коммутации сигналов из информационного поля числовой магистрали (шины 1) на устройства - приемники информации (например ЦАП. Поэтому информационные входы ключей 26 и 27 подклю чены к шинам 7, а выходы - ко входам блока 29 согласования с объектом управления. Ключи 28 предназначены для коммутации выходов устройства - источников информации (например АЦП) на числовую магистраль. Входы ключей 28 подключены к выходам блока 29, а выходы ключей 28 - к шинам 7 информационного поля числовой магистрали. Блок 30 синхронизации имеет вход 31, который подключен к выходу дешифратора 32 нуля, соединенного входами с элементами И 33 группы. Четвертый 34 и третий 35 выходы блока синхронизации подключены к управляющим входам считывания и записи второго блока памяти. Входы второго и третьего элементов ИЛИ 36 и 37 соединены с первым 38 и вторым 39 и входами блока 30. Устройство работает следующим образом. Допустим, имеется запрос на вывод информации, т.е. возбуждён один из выходов 20 блока 19. Этот сигнал готовит цепи узлов 17 и 18 для обращения к фиксированной ячейке из накопителя 2. Работа устройства происходит под управлением импульсов, появляющихся на выходах 34,35,38 и 39 блока 30. В первом такте появляется импульд на вькоде 34. Этот импульс, поступая на управляющий вход узла 17, инициирует считывание ячейки накопителя 2, в которой хранится адрес начальной ячейки из массива ячеек гакопителя Г, соответствующего поступившему запросу на обмен. На выходах блока 4 появляются сигналы. Эта информация через шины 5 записывается в регистр 14 и в резистр 8 регенерации. Во втором такте появляется импульс на выходе 35 блока 30. Под управлением этого сигнала, поступающего на управляющие входы узла 18 и регистра 8 регенерации, производится регенерация считанной в первом такте информации в прежней ячейке, а также запись адреса ячейки из регистра 11 через коммутатор 12 в дешифратор 13. В третьем такте появляется импульс на выходе 38 блока 30. Под управлением этого сигнала производится считы вание дешифратора 13, что вызывает считывание соответствующей ячейки накопителя 1, а также передача адреса в первую ступень дешифратора 10 записи. На выходе блока 3 появляются сигналы, которые записываются в регистр 8 регенерации. Информация адресного поля слова обмена по шинам 5 записывается в регистр 11 адреса, кроме того, через элемент И 24 .она поступает на дешифратор 25, в результате чего открываются одни из ключей коммутации, например ключи 28, и сигналы из информационного поля числовой магистрали по шинам 7 через ключи 26 поступают на входы блока 29. Кроме то го, к адресному полю числовой магистрали через элементы И 33 подключается дешифратор 32, который выявляет признак конца цикла (признаком конца цикла может быть равенство нулю (единице) всех разрядов адресного поля слова обмена . Если есть признак, то возникает сигнал на выходе блока 32, и после четвертого такта работа устройства обмена прекращается до появления нового запроса на обмен. При отсутствии сигнала на входе 31 блока 30 после четвертого такта цикл повторяется j начиная с третьего такта. В четвертом такте возбуждается выход 39 блока 30. Под управлением этого сигнала, поступающего на управляющие входы регистра 8 регенерации и дешифратора 10 записи, производится регенерация считанной к третьем такте информации по прежнему адресу в ячейке накопителя 1, а также передача адреса очередного обращения из регистра 1I через открытьш коммутатор 12 в дешифратор 13. Таким образом, в течение третьего и четвертого тактов работы устройств (один цикл обращения к накопителю производится вьщача одного слова на блок 29 и подготовка адресных цепей устройства кг вьщаче следунлцего слова обмена. Если признак конца цикла отсутствовал в третьем такте, то вновь возбуждается выход 38. Из ячейки накопителя 1 считывается очередное сло во обмена и т.д. до тех пор, пока не будет считан весь массив слов обмена, соответствующий данному запрос на обмен, т.е. пока не появится признак конца цикла. Работа по приему информации от источников отличается от описанного тем, что возбуждается один из выходов 21 блока 19 и присутствует сигнал на выходе элемента ИЛИ 22, который через элемент И 23, управляемый с выхода 38 блока 30, в третьем такте блокирует выходы блока 6 усилителей информационного поля разрядов слова обмена. Тем самым производится обнуление этого поля. Одновременно с выхода блока 29 информация поступает через ключи 28 и через числовую магистраль (шины 1) на входы регистра 8. В остальных тактах работы по приему информации не отличается от работы по вьщаче. Таким образом, для выдачи по запросу на обмен массива ячеек связи необходимо затратить количество обращений к накопителю, на единицу большее количества ячеек связи в этом массиве и плюс обращение к последней ячейке из массива ячеек, в которой находится признак конца цикла (для случая, если признаком конца является наличие нулей или единиц в адресном поле слова обмена}. Если-под признак конца цикла отвести один разряд в информационном поле слова обмена, то этого обращения не потребуется. В предлагаемом устройстве по сравнению с известным где на вьщачу одного слова обмена расходуется два обращения к накопителю, вьщача массива слов обмена осуществляется с числом обращенийпочти в два раза меньше. В качестве накопителей в предлагаемом устройстве может использоваться память ЦВМ, обращение к которой производится через общий дешифратор адреса, обновление информации в них осуществляется с помощью обычной команды засьшки, что устраняет необходимость в специальной команде и ведет к сокращению числа состояний микропрограммного автомата. Формула изобретения Устройство для обмена информацией, содержащее первый блок памяти, соединенный информационным входом с вы5СОДОМ регистра регенерации, адресным входом - с выходом регистра адреса, входом управления считыванием - с

98

;iepBbiM выходом блока синхронизации входом управления записью - со вторым выходом блока синхронизации, а информационным выходом - с информационным входом второго блока памяти, информационный выход которого соединен через блок усилителей адресного поля с первым информационным входам регистра рег.енерации, через блок усилителей информационного поля со вторым информационным входом регистра регенерации, информационным входом коммутатора вывода и информационным выходом коммутатора ввода, входы управления записью и считыванием второго блока памяти подключены соответственно к третьему и четвертому выходам блока синхронизации, а адресные входы к соответствующим выходам блока формирования запросов на обмен и входом первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выходом подключенного к управляющему входу блока усилителей информационного поля, а .вторым входом - к первому выходу блока синхронизации и первому входу второго эле- . мента И, второй вход и выход которого соединены соответственно с выходом блока усилителей адресного поля и входом дешифратора, выходы которого подключены к соответствуюпщм адрес310

ным входам коммутаторов ввода и вывода, информационные входы коммутатора ввода и информационные выходы коммутатора -вывода соединены с соответствующими входами и выходами блока согласования с объектом, отличающееся тем, что, с целью повышения быстродействия, в устройство введены в1Орой и третий элементы ИЛИ, группа элементов И и дешифратор нуля, причем входы второго и третьего элементов ИЛИ соединены соответственно со вторым и третьим выходами блока синхронизации, а выходы - соответственно с синхронизирующими входами первого блока памяти и регистра регенерации, первый информационный вход которого соединен со входом регистра адреса и первыми входами элементов И группы, вторые входы которых подключены к первому выходу блока синхронизации, а выходы - ко входам-дешифратора нуля, выходом соединенного со входом блока .синхронизации.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 507865, кл. G 06F 3/00, 1974.

2.Авторское свидетельство СССР по заявке № 2550392/18-24,

кл. G -06 Р 3/00, 1977 прототип .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1977 |

|

SU705440A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Запоминающее устройство | 1984 |

|

SU1185394A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

Авторы

Даты

1981-07-23—Публикация

1979-11-06—Подача