Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных арифметических узлов.

Цель изобретения - повышение достоверности функционирования устройства.

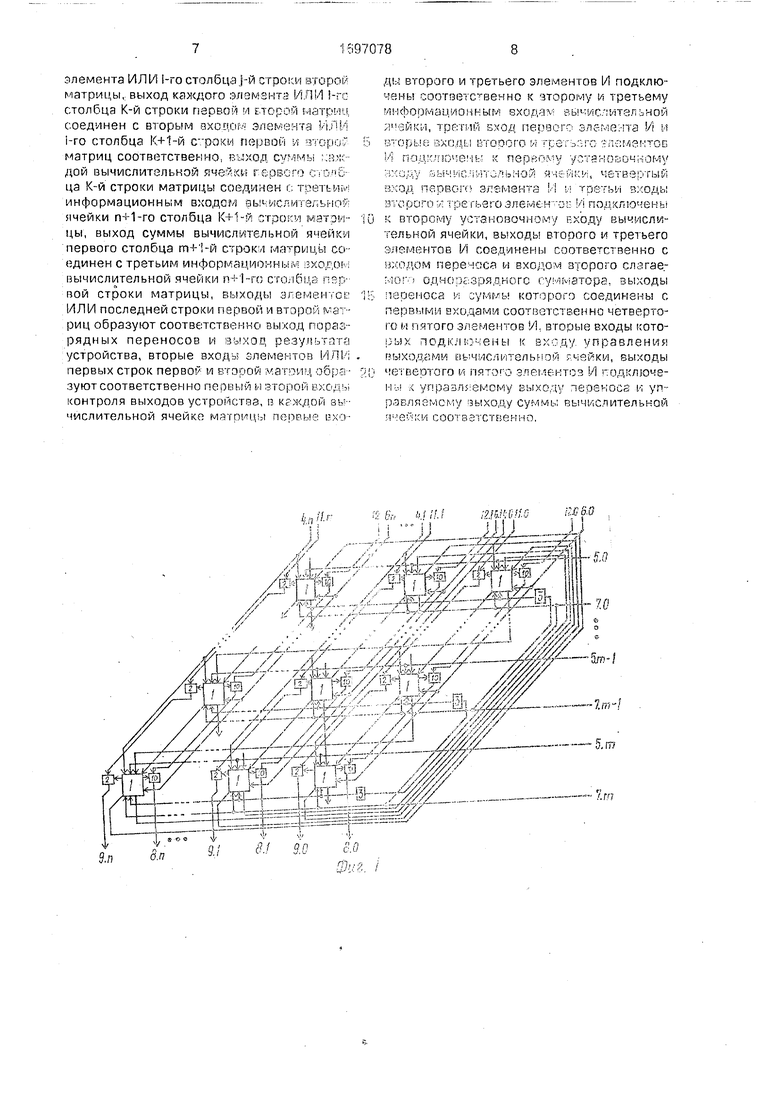

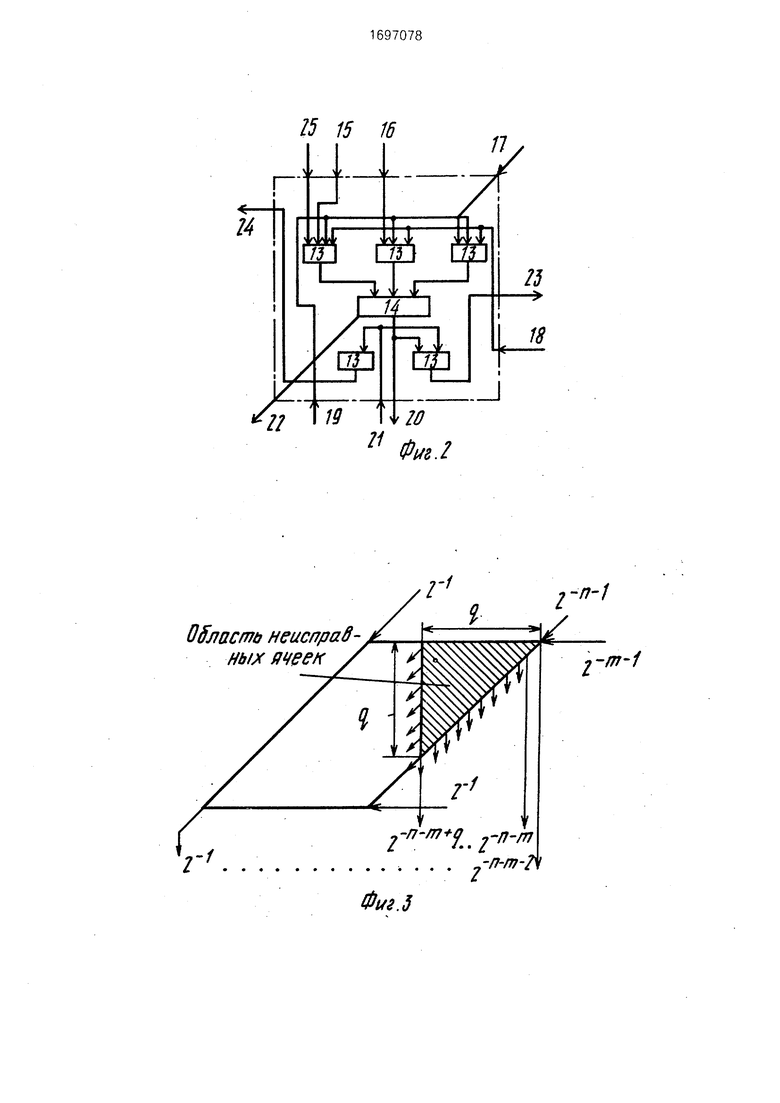

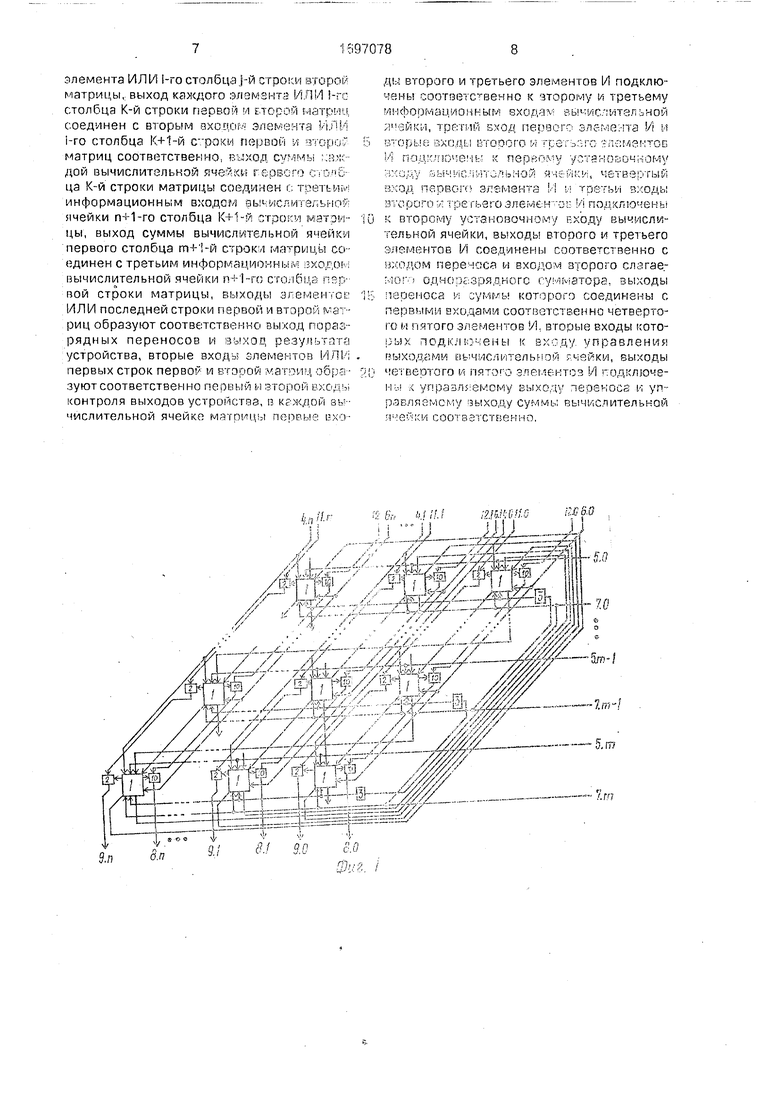

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема вычислительной ячейки матрицы; на фиг.З изображена рабочая область устройства с локальной областью неисправных ячеек; на фиг.4 приведен пример расположения неисправной области матрицы вычислительных ячеек.

Устройство, изображенное на фиг.1, содержит матрицу 1 вычислительных ячеек, первую матрицу элементов ИЛИ 2, .группу

элементов НЕ 3, вход 4 множимого устройства, вход 5 множителя устройства, вход 6 отключения столбцов матрицы устройства, вход 7 отключения строк матрицы устройства, выход 8 результатов устройства, выход 9 поразрядных переносов устройства, вторую матрицу элементов ИЛИ 10, входы 11, 12 контроля выходов устройства.

Вычислительная ячейка матрицы 1, пример исполнения которой приведен на фиг.2, содержит элементы И 13, одноразрядный сумматор 14, вход 15 блокировки первого слагаемого вычислительной ячейки, второй и третий информационные входы 16, 17 вычислительной ячейки, установочные входы 18,19 вычислительной ячейки, выход 20 суммы и вход 21 управления выходами вычисQv ю ч

о VJ

00

лительной ячейки, выход 22 переноса вычислительной ячейки, управляемые выходы 23, 24 суммы и переноса вычислительной ячейки, первый информационный вход 25 вычислительной ячейки.

Каждая I, j-я вычислительная ячейка матрицы 1 (I 17гГ; j Тдп) вычисляет произведение 1-го разряда множимого и j-ro разряда множителя, причем 1-й разряд множимого имеет вес 2 , а j-й разряд множителя имеет вес 2 (допустим, множимое и множитель представлены в виде чисел с плавающей запятой). При этом вес выхода суммы i, j-й вычислительной ячейки матрицы 1 равен а вес выхода переноса I, j-й вычислительной ячейки матрицы 1 равен . За счет сдвига множимого (множителя) влево-вправо можно изменять веса выходов переноса и суммы I.J-й вычислительной ячейки матрицы 1.

Предположим, матрица 1 содержит локальную область неисправных ячеек, В этом елучае результат вычислений S получается с ошибкой: S S + e (S - правильный результат вычислений, е - ошибка вычислений), причем чем выше веса ячеек, входящих в локальную неисправную область, тем больше относительная величина ошибки.

Устройство позволяет минимизировать веса неисправных ячеек и тем самым минимизировать ошибку вычислений.

Особенностью устройства является то, что граничные входы и выходы вычислительных ячеек первого и последнего столбцов и ряда соединены между собой в соответствии со схемой межсоединений вычислитель- ных ячеек внутри устройства, что обеспечивает возможность организации вычислений в различных областях замкнутого по столбцам и рядам устройства за счет циклического сдвига множимого и множителя на соответствующих информационных входах устройства.

Назовем область матрицы 1 размером n x m, в которой проводятся вычисления, рабочей областью матрицы, Тогда, если неисправные ячейки локализованы в ограниченной области матрицы 1, можно таким образом сместить рабочую область, чтобы неисправные ячейки участвовали в вычислениях с наименьшим весом. Сдвиг рабочей матрицы 1 производится за счет циклического сдвига операндов на информационных входах матрицы 1.

Устройство позволяет минимизировать ошибку вычислений, но не исключает ее полностью, поэтому определенное число К младших разрядов результата вычисляется неправильно (см. фш .3).

Рассмотрим влияние неисправной области матрицы 1 на результат вычислений. В худшем случае неисправность может проявляться по выходам переноса вычисли- тельных ячеек матрицы 1 q-й колонки (фиг.З) и по выходам суммы j-x вычислительных ячеек первого столбца матрицы (j fiq) (младшие разряды результата). Суммарная величина ошибки в этом случае равна:

1макс р-2-n-m+q+1+ J 2 п-т+. J i

(1)

1t- Второе слагаемое в формуле (1) не пре- 10 вышает величины

Таким образом,

1макс(д + 1)2-П-т+1+

(2)

Во многих практических случаях достаточно получить n старших разрядов результата вычислений. Для получения правильных старших разрядов результата необходимо, чтобы

макс 2

-п-г

(3)

-п-1

где 2 - вес n+1-ro разряда результата. Сравнивая (2) и (3), получим неравенство для определения параметра неисправной области q:

(q + 1) 2 n m+Hq .

Таким образом, в том случае, если вели- чина неисправной области такова, что ее можно локализовать в пределах q колонок матрицы, при соответствующем сдвиге операндов можно получить n правильных разрядов результата. Младшие m разрядов результата из устройства не выводятся.

Оценим величину возможной области неисправных ячеек. о Для n 32 и m 32 величина q 25:

(q + 1) ,

ос .0 65+25 9

.

Следовательно, устройство позволяет получить с n-разрядной точностью правильный результат, если область неисправных ячеек занимает до 30% площади матрицы 1. При этом считается, что входы 4-7 множимого, множителя, отключения столбцов и строк устройства и выходы 8, 9 устройства исправны. Входы б, 7 устройства обеспечивают условное размыкание устройства на границах рабочей области.

Устройство может работать в двух режимах: при наличии локальной области неисправных ячеек матрицы 1 и без неисправных вычислительных ячеек матрицы 1.

Устройство работает следующим образом.

Рассмотрим работу устройства в режиме без неисправных вычислительных ячеек матрицы 1. В этом случае перед началом вычислений на входы 7.1-7.т отключения строк и на входы 6.1-б.п отключения столбцов устройства подаются сигналы Т, а на входы 6 0 и 7.0 - сигналы О. Тем самым обеспечивается условное размыкание устройства на границах рабочей области и включается цепь съема старших п разрядов результата.

Процесс вычисления начинается с подачи на вход 4 множимого разрядов множимого и на вход 5 множителя разрядов множителя. После окончания переходного процесса в устройстве старшие п разрядов результата снимаются с выходов 8 и 9 устройства в двухрядном коде.

При обнаружении и локализации в устройстве области неисправных ячеек матрицы 1 любыми известными методами, например рабочая область матрицы 1 смещается таким образом, чтобы минимизировать веса неисправных ячеек.

Рассмотрим пример, изображенный на фиг,4 (п m 5). В этом случае перед началом вычислений на входы 6.2 и 7.2 отключения устройства подаются сигналы О, условно размыкая устройство на границах рабочей области, а на остальные входы блокировки подаются сигналы Г, определяющие положение рабочей области. В этом случае веса неисправных ячеек минимальны. Разряды множимого подается на входы 4.3-4.1 устройства, разряды множителя подаются на входы 53-5.1 устройства. По окончании переходного процесса старшие п разрядов результата снимаются с выходов 8.3-8.1 и 9.3-9.1 устройства в двухрядном коде.

Формула изобретения

Устройство для умножения, содержащее матрицу (n+1) x (m+1) вычислительных ячеек (п - разрядность множимого, m - разрядность множителя), каждая из которых содержит первый элемент И и одноразрядный сумматор, причем первые информационные входы вычислительных ячеек каждого 1-го столбца матрицы подключены к 1-му разряду входа множимого устройства (1 I п+ 1),

вход блокировки первого слагаемого вычислительных ячеек каждой j-й строки матрицы подключен к j-му разряду входа множителя устройства (1 j m +1), выход переноса 5 каждой вычислительной ячейки 1-го столбца К-й строки матрицы соединен с вторым информационным входом вычислительной ячейки 1-го столбца К+1-й строки матрицы (1 К т), выход суммы каждой вычисли0 тельной ячейки 1-го столбца К-й строки матрицы соединен с третьим информационным входом 1-1-го столбца К+ 1-й строки матрицы (2 I п+1), выход переноса каждой вычислительной ячейки 1-го столбца (т+1)-й стро5 ки матрицы соединен с вторым информационным входом вычислительной ячейки 1-го столбца первой строки матрицы, выход суммы каждой вычислительной ячейки 1-го столбца (т+ 1)-й строки матрицы сое0 динен с третьим информационным входом вычислительной ячейки 1-1-го столбца первой строки матрицы, в каждой вычислительной ячейке матрицы первый и второй входы первого элемента И подключены соответст5 венно к первому информационному входу и входу блокировки первого слагаемого вычислительной ячейки, выход первого элемента И соединен с входом первого слагаемого одноразрядного сумматора, вы0 ходы переноса и суммы которого являются соответственно выходами переноса и суммы вычислительной ячейки, отличающееся тем, что, с целью повышения достоверности функционирования, в чего введе5 ны группа элементов НЕ и две матрицы элементов ИЛИ, в каждую вычислительную ячейку матрицы введены четыре элемента И, причем первые установочные входы вычислительных ячеек каждого 1-го столбца

0 матрицы подключены к i-му разряду входа отключения столбцов матрицы устройства, вторые установочные входы вычислительных ячеек каждой J-й строки матрицы подключены к j-му разряду входа отключения

5 строк матрицы устройства, вход каждого К- го элемента НЕ группы подключен к К+1-му разряду входа отключения строк матрицы устройства, вход m+1-го элемента НЕ груп-1 пы подключен к первому разряду входа от0 ключения строк матрицы устройства, выход каждого j-ro элемента НЕ группы соединен с входами управления выходами вычислительных ячеек j-й строки матрицы, управляемый выход переноса каждой

5 вычислительной ячейки 1-го столбца J-й строки матрицы соединен с первым входом элемента ИЛИ 1-го столбца j-й строки первой матрицы, управляемый выход суммы каждой вычислительной ячейки 1-го столбца j-й строки матрицы соединен с первым входом

элемента ИЛ И 1-го столбцами строки второй матрицы, выход каждого элемента ИЛИ i-ro столбца К-й строки первой и второй матриц соединен с вторым входом элемента ИЛИ 1-го столбца К+1-й строки первой и второй матриц соответственно, выход суммы г.аж- дой вычислительной ячейки первого столбца К-й строки матрицы соединен с третьим информационным входом вычислительной ячейки n+1-ro столбца К+1-й строки матрицы, выход суммы вычислительной ячейки первого столбца rn+1-й строки матрицы соединен с третьим информационным входом вычислительной ячейки n+1-ro столбца первой строки матрицы, выходы элементов ИЛИ последней строки первой и второй матриц образуют соответственно выход поразрядных переносов и выход результата устройства, вторые входы элементов ИЛИ первых строк первой и второй матриц образуют соответственно первый и второй входы контроля выходов устройства, в каждой вычислительной ячейке матрицы первые входы второго и третьего элементов И подключены соответственно к второму и третьему информационным входам вычислительной ячейки, третий вход первого элемента И м

вторые входы второго и третьего глпмантов А подключены к первому установочному входу оычйслитольной ячейка, четвертый вход первого элемента / и третьи входы второго и третьего элемент ов л подключены

к второму установочному входу вычислительной ячейки, выходы второго и третьего элементов И соединены соответственно с входом переноса и входом второго слагаемого одноразрядного сумматора, выходы

пеоеноса и суммы которого соединены с первыми входами соответственно четвертого и пятого элементов И, вторые входы которых подключены к входу управления выходами вычислительной ячейки, выходы

четвертого и пятого элементов И подключены к управляемому выходу переноси и управляемому выходу суммы вычислительной ячейки соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Вычислительное устройство | 1989 |

|

SU1697077A2 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для умножения | 1989 |

|

SU1770960A1 |

Ы -я

д. 81 9.0 80

Фиг /

12 8п ki U

I2JMCKO

1т

25 15 16

Область неисправных tweex

Фм.2

t-m-1

Множимое блокировка J-2J -J ф

/ЕГа

-zfB.

жу. /D а а

а J-2/ЕГа

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-07—Публикация

1989-05-31—Подача