(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДАННЫХ

1

Изобретение относится к вычислительной технике и может быть использовано в электронной вычислительной машине.

Известны многомодульные устройства для обработки данных, содержащие ряд взаимосвязанных модулей памяти и процессорных модулей 1.

Однако в этих устройствах кснлплектование произвольных конфигураций модулей сопряжено с использованием сложной коммутирующей аппаратуры (типа матричных переключателей), а реконфигурация устройства.при обнаружении в каком-либо модуле неисправности или при необходимости изменить рабочую конфигурацию требует наличия специального блока управления реконфигурацией или применения развитии операционной системы.

Недостатками этих устройств являются их сложность и большой объем аппаратуры.

Наиболее близким к изобретению по технической сущности является устройство для обработки данных, содержащее М модулей памяти, N процессорных модулей и блок переключателей, причем адресные выходы и ин-

формационные входы и выходы всех процессорных модулей подключены к адресным входам и информационным выходам и входам соответственно всех. модулей памяти, каждый модуль памяти содержит блок управления, блок контроля и накопитель, выход которого соединен .с входом блока контроля и .,,. информационным выходом данного модуля памяти, информационный и адресный входы которого соединены соответственно с информационным входом накопителя и первым входом блока управления, первый выход которого соеди15нен с адресным входом накопителя, каждый процессорный модуль содержит командный блок, арифметический блок и регистр адреса, выход и адресный вход которого соединен соответствен20но с адресным выходом данногб процессорного модуля и первым выходсм арифметического б.пока, второй и третий выходы которого соединены, соответственно с информационным вы25ходом данного процессорного модуля и первым входом командного блока,выход которого подключен к управляющим входам регистра адреса и арифметического блока, к информационному

30 входу которого подключен информацинный вход данного процессорного одул я 2..

Недостатки известного устройства остоят в больших аппаратурных заратах и сложности, так как коммутаия модулей памяти выполняется сложными конфигураторами входных и выходных информационных потоков памяти. Их сложность обусловлена разделением информационных потоков различных . модулей памяти, из-за чего при реконфигурации в случае отказа одного из модулей приходится полностью отключать информационный поток неисправного модуля памяти и вместо него подключать информационный поток исправного.

Кроме того, для упраъления текущим состоянием (конфигурацией) в устройстве используются специальные регистры состояния со сложной логикой установки и модификации. Специализация этих регистров для целей управления конфигурацией в значительной мере затрудняет их использование для предоставления процессорным модулям информации о текущей конфигурации памяти в удобной для обработки и анализа форме.

При этом устройство может использоваться только для случаев, когда в отдельном модуле памяти помещается очень малое число (чаще всего один) бит всех слов массива памяти (бит- расслоенная память), что требует дополнительных затрат при комплектовании устройства произвольным количеством модулей памяти с целью расширения доступного массива ячеек памяти.

Цель изобретения - упрощение, устройства и расщирение области его применения.

Поставленная цель достигается тем, что в устройство, содержащее М процессоров, М блоков памяти и блок переключателей, причем каждый процессор состоит из арифметического блока, регистра адреса и командного блока, а блок памяти состоит из накопителя, узла управления и узла контроля, причем выходы регистров адреса каждого процессора соединены с первыми входами узлов управления, первые выходы которых подключены соответственно к адресным входам накопителей одноименных блоков памяти, инфбрмационные входы которых подключены 1с первым выходам арифметических блоков, выход командного блока каждого процессора соединен с первыми входами арифметического блока и регистра адреса того же -процессора, а первый вход - с.вторым выходом арифметического блока, третий выход которого подключен к второму входу регистра адреса торо же процессора, информационный выход

накопителя i-ro блока памяти (,M) соединен с входом узла контроля и третьим входом арифметического блока i-ro процессора, в каждый процессор, введена схема сравнения, а в каждый блок памяти - коммутатор, сумматор, входная схема сравнения и элемент ИЛИ, причем первый вход и выход схемы сравнения каждого процессора соединены соответственно с выходом регистра адреса и вторым входом командного блока того же самого процессора, а вторые входы . схемы сравнения всех процессоров подключены к выходу коммутатора М-то блока памяти, первый вход коммутатора i-ro блока памяти соединен с выходом сумматора того же блока памяти первым входом соединенного с вторым выходом узла управления, того же блока памяти, первый и второй входы которого подключены соответственно к первому входу и выходу входной схемы сравнения, а третий выход - к первому входу элемента ИЛИ того же блока памяти, вторые входы входной схемы сравнения, сумматора и коммутатора i-ro блока памяти соединены с выходом коммутатора (i-l)-r блока памяти, а вторые входы входной схемы сравнения, сумматора и коммутатора первого блока памяти соединены с .входом опросаустройства, третий вход коммутатора i-ro блока памяти соединен с выходом элемента ИЛИ того же блока памяти, вторым и третьим входами соединенного соответственно с выходом узла контроля того же блока памяти и i-ым выходом блока переключателей.

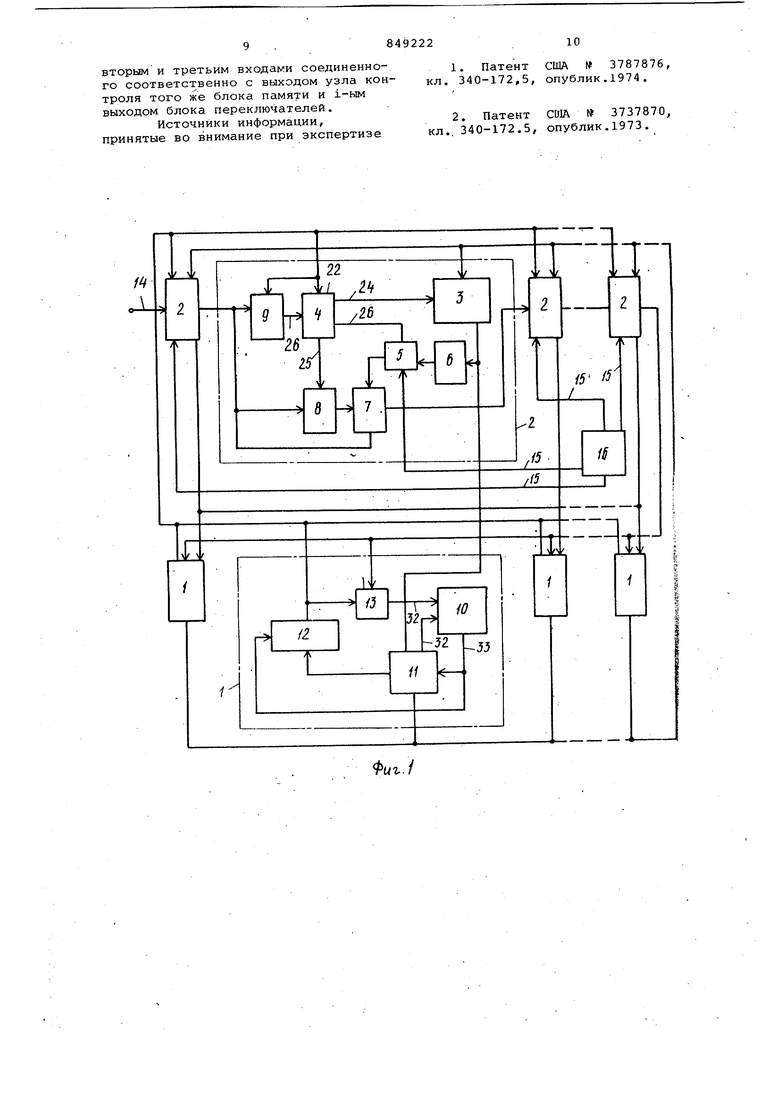

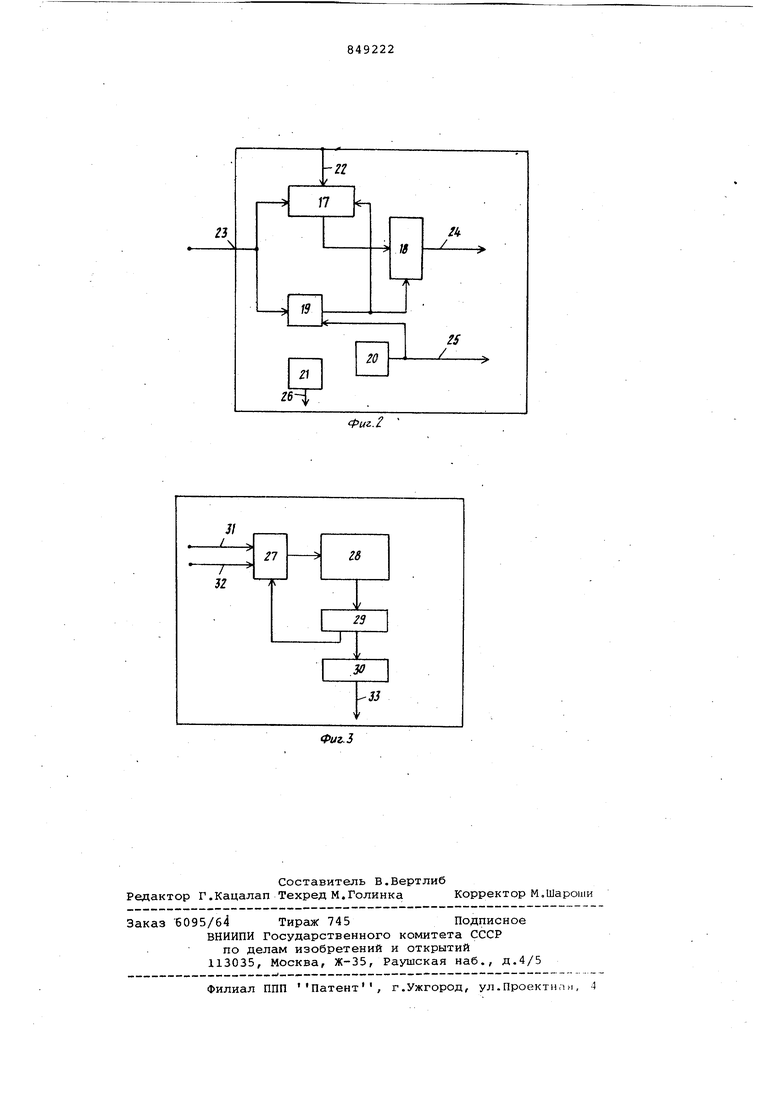

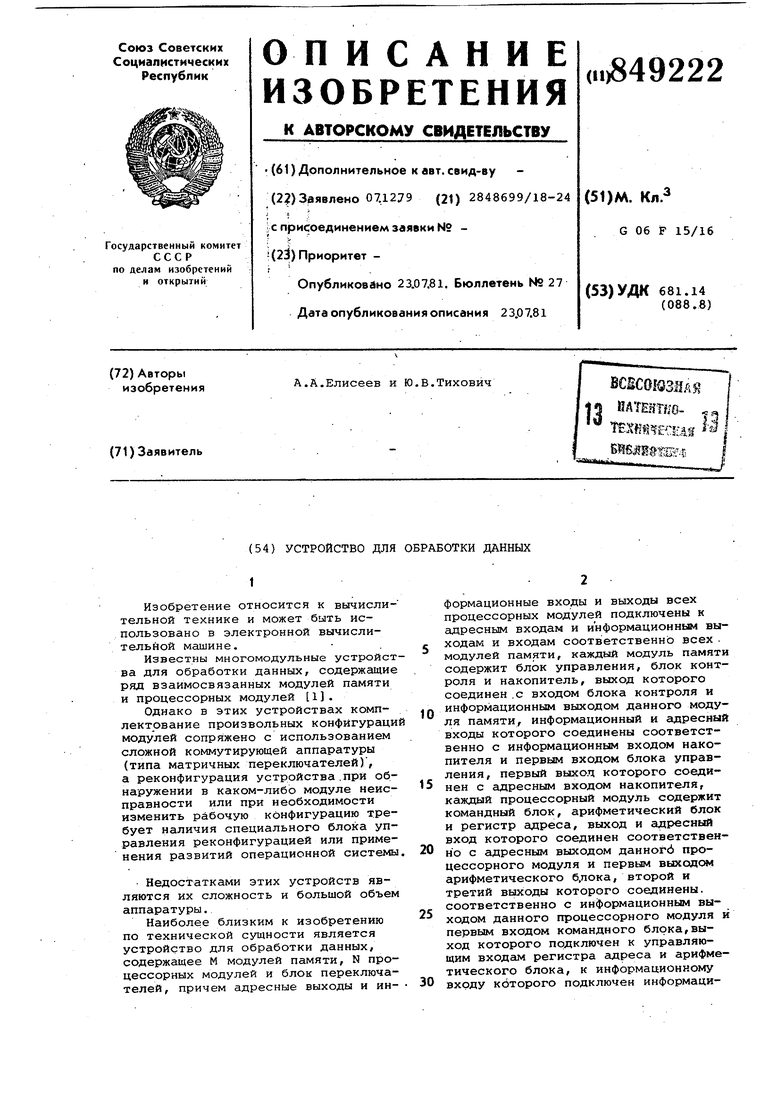

На-фиг.1 представлена блок-схема устройства; на фиг. 2 - функциональная схема узла управления; на фиг.Зсхема командного блока.

Устройство содержит процессоры 1, блоки 2 памяти, накопитель 3, узел 4 управления, элемент 5 ИЛИ, узел 6 контроля, коммутатор 7, сумматор 8, входную схему 9 сравнения, командный блок 10, арифметический блок 11, регистр 12 адреса, схему 13 сравнения, вход 14.опроса устройства и управляющие выходы 15 блока 16 переключателей.

Узел 4 управления (фиг.2) включает регистр 17 текущего адреса, дешифратор 18 адреса, генератор 19 синхроимпульсов, переключатель 20 режима работы, формирователь 21 логической единицы, первый 22 и второй 23 входы и первый 24, третий 25 и второй 26 выходы узла.

Командный блок (фиг.З) включает регистр 27 адреса микрокоманды, память 28 микропрограмм, регистр 29 микрокоманды, дешифратор 30 микрокоманды, первый 31 и второй 32 входы и выход 33 командного блока 10.

Устройство работает следующим образом.

Программы и данные хранятся в накопителях 3 блока 2 памяти. Выполнение программ, обработку данных и замещение программ в блоках 2 производят процессоры 1,каждый из которых может быть как универс ального типа, так и рассчитан на выполнение узкого, специализированного класса функций,например на выполнение операций по вводу-выводу. Во время работы любой из процессоров 1 может обратиться к памяти по единым для всех процессоров 1 адресным шинам.

В каждом блоке 2 памяти хранится информация, расположенная в-порядке возрастания адресов памяти, т.е. один блок 2 содержит непрерывную последовательность ячеек памяти.При каком-либо обращении к памяти одного из процессоров 1этот процессор получает доступ только к одному блоку 2 , в котором расположена ячейка с адресом, сформированном в регистре 12 процессора. 1, затребовавшего обращение к памяти. При этом,, если выполняется чтение памяти, информация, прочитанная из ячейки адресованного блока 2, выдается этим блоком на свой информационный выход. Если выполняется операция записи в память, информация, подлежащая записи, передается с выхода арифметического блока 11 на информационный выход-процессора 1, затребовшего выполнение записи и по информационному входу блока 2, в котором выполняется запись, указанная информация записывается в накопитель 3 этого блока.

Текущая конфигурация памяти од- , нозначно отражается словом опроса. которое формируется на выходе опроса М-го блока 2 памяти и передается на вход схемы сравнения каждого процессора 1.

Исходное значение слова опроса на входе 14 в простейшем варианте реализации устройства принимается нулевым. В процессе распространения сигналов опроса каждый рабочий блок 2 производит модификацию в сумматоре 8 поступившего к нему входного слова опроса на величину, определяемую узлом 4.

Например, для полностью идентичных блоков 2 памяти такая модификация может выполняться простым прибавлением единицы к входному слову опроса (подсчет количества рабочих блоков 2). Единица вырабатывается формирователем 21. дополнительное подключение или отключение одного из нескольких блоков 2 (при сохранении непрерывности цепочки опроса) позволяет только на результирующее значение слрва опроса, поступающего на вход схемы 13 сравнения каждого

процессора 1. При каждом обращении любого процессора 1 к памяти адрес ячейки памяти, к которой требуется обращение, сравнивается с результирующим словом опроса в схеме 13 сравнения. Может случиться, что адрес нужной ячейки соответствует массиву адресов блока 2 памяти, отсутствующего в текущей конфигурации устройства, т.е. этот адрес выходит за пределы массива доступных адре0сов всех рабочих блоков 2. В этом случае схема 13 формирует специальный сигнал, по которому командный блок 10 запускает специальную процедуру обработки особого случая,выз5ванного неверной адресацией памяти. Эта процедура заключается в занесении в регистр 27 адреса микрокоманды начального адреса микропрограммы, обрабатывающей особый случай, вы0полнении указанной микропрограммы и выходе в программное прерывание.

Блок 2 памяти участвует в -модификации слова опроса только в том случае, если он находится в рабочем состоянии. Нерабочее состояние про5извольн.ого блока 2 может быть вызвано функционированием блока 2, приводящим к срабатыванию узла б контроля, или тем, что блок находится в автономном режиме рабо0ты, заданном переключатег:ем 20 узла 4 (фиг.2), или отключен от устройства сигналом отсоединения, поступившим от переключателей конфигурации, расположенных в блоке 16.

Любая из этих причин вызывает срабатывание элемента 5 ИЛИ, сигнал с выхода которого настраивает коммутатор 7 на прямую передачу входного слова опроса без изменения в сумматоре 8 со входа на выход опроса данного блока 2.

Реакция ва отключение от блока 2 электропитания и на физическое отсоединение блока 2 от устройстване является существенной в предлагаемом устройстве, однако и в этих случаях сохраняются как общий подход к понятию нерабочего состояния блока 2 памяти, так и единая трактовка устройством этого состояния. Обеспечить нужную реакцию на одну из двух или на обе эти причины позволяет выбор конкретного варианта реализации коммутатора.. Например, помимо электронных компонентов коммутатор 7 может содержать электромеханические и/или механические компоненты.Как вариант реализации можно рассматривать использование электромагнитных реле с нормально замкнутыми контактами,шунтирующих внутриблочную цепочку опроса при отключении электропитания блока 2, Нужная реакция на физическое отключение блока 2 обеспечивается специальной конструкцией блочных разъемов и кабели цепочки опроса устройства.Разъемы могут быть снабжены контакторами, замыкающими соответствующие входы и выходы опроса какоголибо блока 2 при отсоединении разъемов этого блока.

Таким рбразоМг слово опроса, проходя через рабочий блок 2, модифи.цируется сумматором 8, тогда как неработоспособным блоком 2 оно транслируется без изменения.в устройстве, содержащем М блоков 2, путем подачи сигналов отключения по вы- ходам 15 или путем перевода определенных блоков 2 в автономный режим в исходнЬм состоянии может быть задана произвольная конфигурация памяти.

При выходе из строя одного из рабочих блоков 2 или при необходимости отключить этот блок от устройства элемент 5 ИЛИ по сигналу на одном из его входов настраивает коммутатор 7 на логическое отключение (шунтирование цепочки опроса) данног блока 2 от устройства.

Для нормальной работы с памятью при отключении какого-либо из блоков2 памяти необходимо сохранить непрерывную последовательность адресуемых ячеек. Поэтому в каждом блоке 2 предусмотрена входная схема 9 сравнения позволяющая определить, содержится ли в данном блоке адресуемая ячейка. В простейшем варианте реализации устройства во входной схеме 9 сравнивается группа старших разрядов адреса ячейки (номер адресуемого блока 2) и текущий номер блока 2 определяемый входным словом опроса этого блока. Таким образом, входное слово опроса рабочего блока 2 фактически определяет адрес самой первой ячейки этого блока.

Использование изобретения позволяет:

а)комплектовать конфигурацию блоков памяти из любого количества блоков при любом соотношении и размещении в данной конфигурации рабочих и резервных (отключенных , нерабртоспособных или т.п.) блоков памяти;

б)получать в удобной форме оперативную информацию о текущей рабочей конфигурации блоков памяти, которая непосредственно может использоваться процессорными модулями при обращении к памяти;

в)выполнять реконфигурацию подключенного к устройству комплекта блоков памяти по сигналу неисправности блока, вырабатУваемому самим блоком памяти, по сигналу переключения блока памяти, в автономный режим или по внешнему управляющему сигналу реконфигурации (например, с,пульта управления устройства).

При этом вводимое оборудование отличается простотой, регулярностью и повторяемостью.

Формула изобретения

Устройство для обработки данных, содержащее М процессоров, М блоков памяти и блок переключателей, причем каждый процессор состоит из арифметического блока, регистра адреса и .командного блока, а блок памяти состоит из накопителя, узла управления и узла контроля, причем выходы регистров адреса каждого процессора соединены с первыми входами узлов управления, первые выходы которых подключены соответственно к адресным входам накопителей одноименных блоков памяти, информационные входы которых подключены к первым входам арифметических блоков, выход командного блока каждого процессора соединен с первыми входами арифметического блока и регистра адреса того же процессора, а первый вход - с вторым выходом арифметического блока, третий выход которого подключен к второму входу регистра адреса того же процессора, информационный выход накопителя i-ro блока памяти (,M) соединен с входом узла контроля и третьим входом арифметического блока 1-го процессора, отличающееся тем, что, с целью упрощения устройства и сокращения-аппаратурных затрат, в каждый процессор введена схема сравнения, а в каждый блок памяти - коммутатор, сумматор, входная схема сравнения и элемент ИЛИ, причем первый вход и выход схемы сравнения каждого процессора соединены соответственно с выходом регистра адреса и вторым входом командного олока того же самого процессора, а вто.рые входы схемы сравнения всех процессоров подключены к выходу коммутатора М-го блока памяти, первый вход коммутатора i-го блока памяти соединен с выходом сумматора того же блока памяти, первым входом соединенного с вторым выходом узла управления того же блока памяти, первый и второй входы которого подключены соответственно к первому входу и выходу входной схемы сравнения, а третий выход - к первому входу элемента ИЛИ того же блока памяти, вторые входы входной схемы сравнения сумматора и коммутатора i-ro блока памяти соединены с выходом коммутатора (1-1)-го блока памяти, а вторые входы входной схемы сравнения сумматора и коммутатора первого блока памяти соединены с входом опроса устройства, третий вход коммутатора i-ro блока памяти соединен с выходом элемента ИЛИ того же блока памяти,

вторым и третьим входами соединенного соответст;венно с выходом узла контроля того же блока памяти и i-ым выходом блока переключателей. Источники информации, принятые во внимание при экспертизе

1. Патент США № 3787876, кл. 340-172,5, опублик .1974 . 2. Патент США № кл.. 340-172.5, опублик.19/J.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| РАДИАЛЬНО-КОЛЬЦЕВОЕ УСТРОЙСТВО ДЛЯ СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2076352C1 |

Фиг./

Авторы

Даты

1981-07-23—Публикация

1979-12-07—Подача