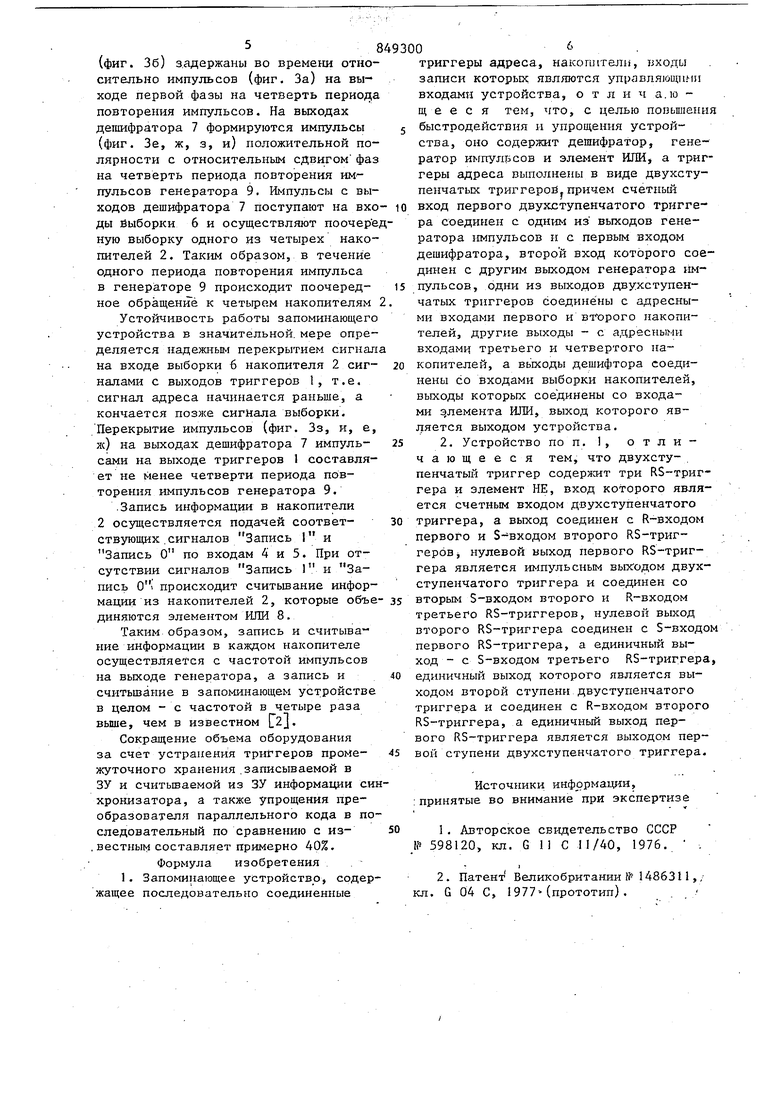

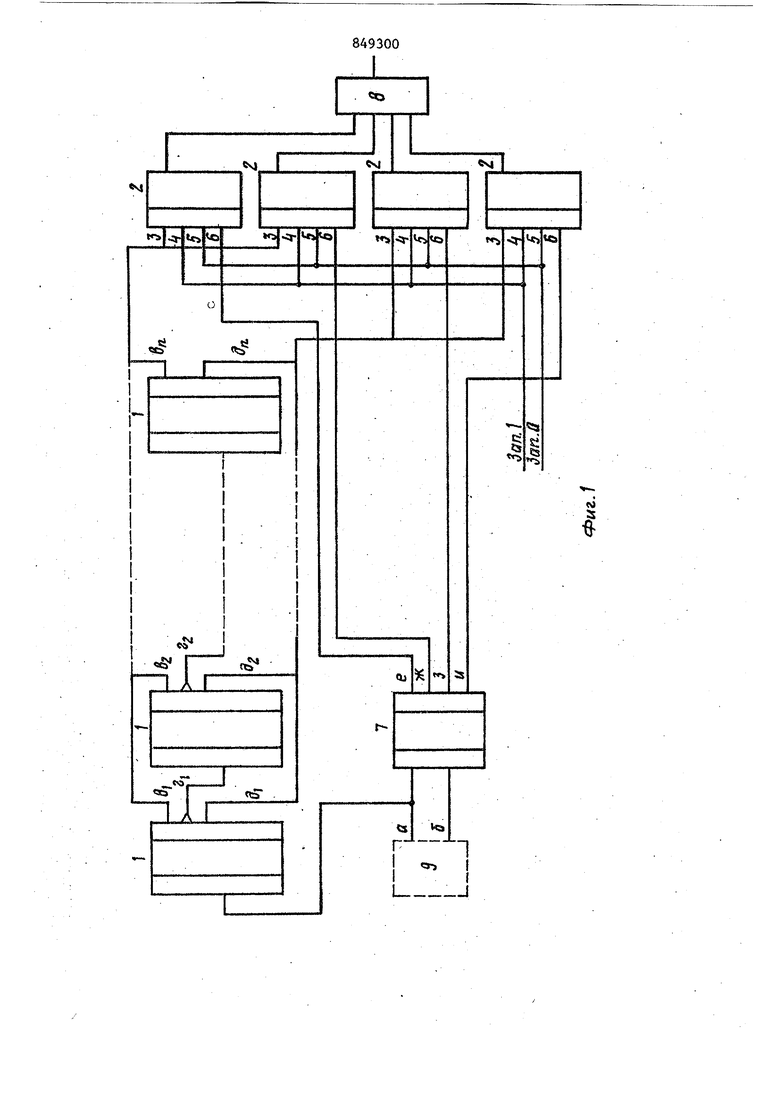

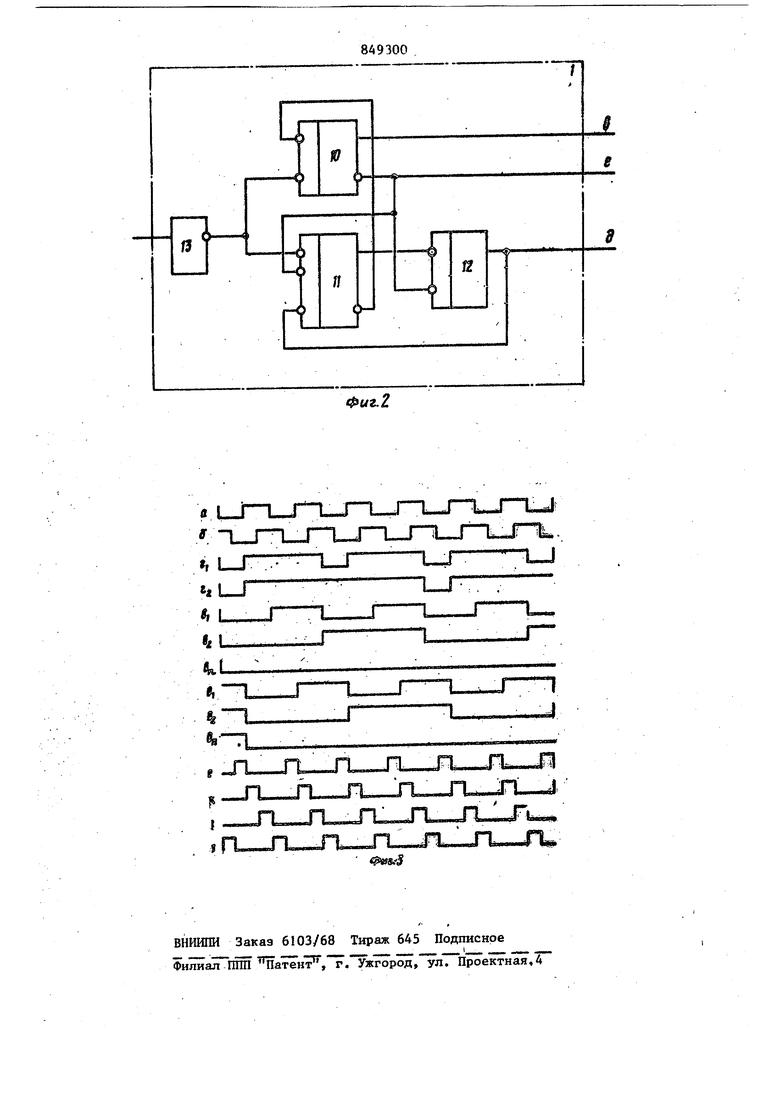

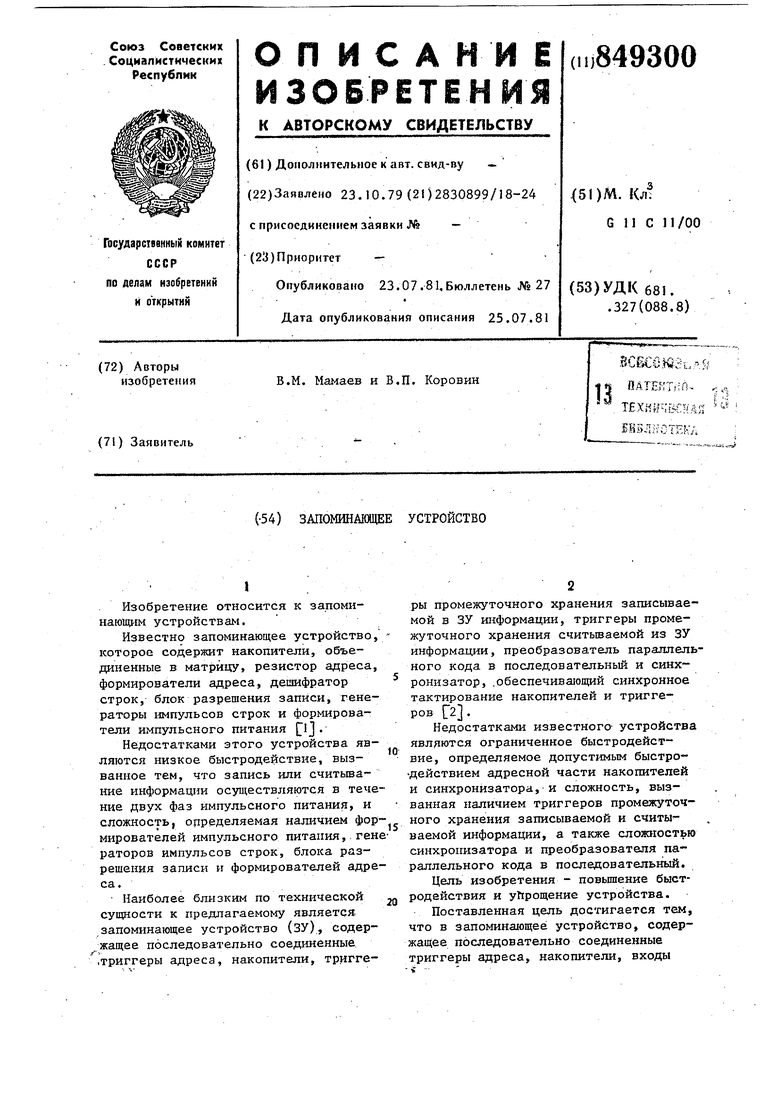

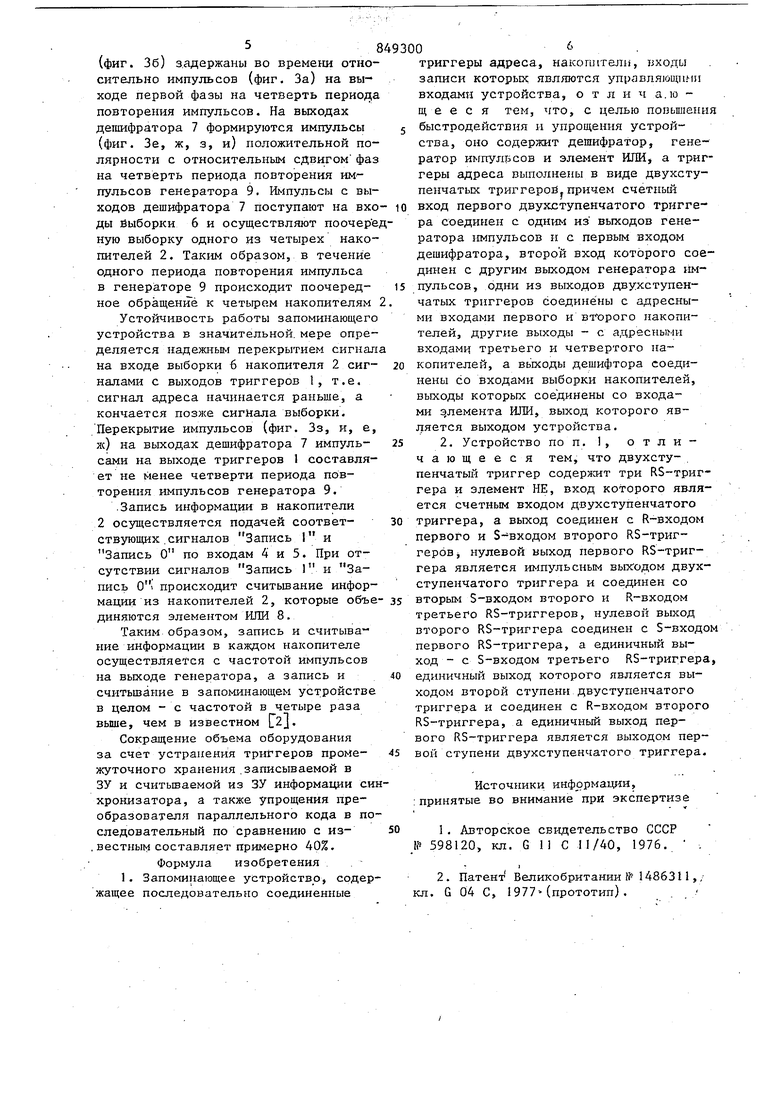

Изобретение относится к запоминающим устройствам. Известно запоминающее устройство которое содержит накопители, объединенные в матрицу, резистор адреса формирователи адреса, дешифратор строк, блок разрешения записи, генераторы импульсов строк и формирователи импульсного питания PJ. Недостатками этого устройства являются низкое быстродействие, вызванное тем, что запись или считьшание информации осуществляются в тече ние двух фаз импульсного питания, и сложность, определяемая наличием Фор мирователей импульсного питания, ген раторов импульсов строк, блока разрешения записи и формирователей адре са. Наиболее близким по технической сущности к предлагаемому является запоминающее устройство (ЗУ), содержащее последовательно соединенные .триггеры адреса, накопители, триггеры промежуточного хранения записываемой в ЗУ иисформации, триггеры промежуточного хранения считываемой из ЗУ информации, преобразователь параллельного кода в последовательньй и синхронизатор, .обеспечивающий синхронное тактирование накопителей и триггеров 2 . Недостатками известного- устройства являются ограниченное быстродействие, определяемое допустимым быстро- действием адресной части накопителей и синхронизатора, и сложность, вызванная наличием триггеров промежуточного хранения записываемой и считываемой информации, а также сложностью синхронизатора и преобразователя параллельного кода в последовательный. Цель изобретения - повышение быстродействия и упрощение устройства. Поставленная цель достигается Т(гм, что в зaпo raнaJoщeё устройство, содержащее последовательно соединенные триггеры адреса, накопители, входы записи которых являются управляющими входами устройства, введены дешифратор, генератор импульсов и элемент ИЛИ, а триггеры адреса выполнены в виде двухступенчатых триггеров, причем счетиый вход первого двухступенчатого триггера соединен с одним из выходов генератора импульсов и с первым входом дешифратора, второй вход которого соединен с другим выходом генератора импульсов, одни из выходов двухступенчатых триггеров соединены с адресными входами первого и второго накопителей, другие выходы - с адресными входами третьего и четвертого нако1|5 телей, а выходы дешифратора соединены со входами выбо ки накопителей, выходы которых соединены со входами элемента ИЛИ,, выход которого является выходом устройства При этом двухступенчатыйтриггер целесообразно вьшолнить в виде блока содержащего три RS-триггера и элемен НЕ, вход которого является счетным входом двухступенчатого триггера, а вьпсод соединен с R-входом первого и S-входом второго RS-TpHrrepoBj нулевой выход первого RS-триггера является импульсным выходом двухступенча того триггера и соединен со вторым S-входом второго и R -входом третьего RS-триггеров, нулевой выход второго RS-триггера соединен с S-входом первого RS-триггера, а еди ничный выход - с S-входом третьего RS-триггера, единичный выход которого является выходом второй ступени двух ступенчатого триггера и соединен с R-входом второго RS-триггера, а единичный выход первого RS-триггера является выходом первой ступени двухступенчатого триггера. На фиг. 1 изображена функциональная схема запоминающего устройства; на фиг. 2 - функциональная схема дву ступенчатого триггера; на фиг. 3временные диаграммы, поясняющие рабо ту устройства. Устройство содержит (фиг. 1.) триг геры 1 адреса, выполненные на двухступенчатых триггерах, накопители 2, имеющие адресные входы 3, входы запи си единицы 4 и нуля 5, входы выборки 6. Устройство также содержит дешифра тор 7, элемент ИЛИ 8 и генератор 9 импульсов. При этом счетный вход первого три гера 1 (левый на фиг. 1) соединен с выходом первой фазы генератора 9 и с первым входом дешифратора 7, второй вход которого соединен с выходом второй фазы генератора 9. Выходы первой ступени триггеров 1 соединены с адресными входами 3 первого (верхний на фиг. 1) и второго накопителей 2. Импульсный выход каждого предьщушего триггера 1 соединен со счетным входом последующего триггера 1. Выходы второй ступени триггеров 1 соединены с адресными входами третьего и четвертого накопителей 2. Выходы дешифратора 7 соединены со входами выборки 6 накопителей 2, а выходы накопителей 2 - со входами элемента ИЛИ 8, выход которого является выходом устройства. Двухступенчатый триггер J {фиг.2) выполнен в виде блока, содержащего три RS-триггера 10-12 и элемент НЕ 13, вход Которого является счетным входом двухступенчатого триггера 1, а выход соединен с R-входом первого 10 и S-входом второго 11 RS-триггеров, нулевой выход первого RS-триггера 10 является импульсным выходом двухступенчатого триггера и соединен со вторым S-входом второго II и R-входом третьего 12 RS-триггеров, нулевой выход второго RS-триггера 11 соединен с S-входом первого RS-триггера 10, в единичный выход - с S-входом третьего 12 RS-триггера, единичный выход которого является выходом второй ступени двухступенчатого триггера и соединен с R-входом второго RS-триггера 11, а единичный выход первого RS-триггера 10 является выходом первой ступени двухступенчатого триггера 1. Устройство работает следующим образом. Импульсы (фиг. За) с. выхода генеР тора 9 поступают на счетный вход первого триггера 1. Длительность отрицательных импульсов (фиг. Зг) на импульсных выходах всех триггеров одинакова и равна длительности отрицательного импульса (фиг. За) на выходе генератора 9. Напряжения (фиг. Зд) на выходах второй ступени триггеров 1 задержаны относительно напряжений (фиг. Зв) на выходах первой ступени триггеров I на величину длительности импульсов генератора 9. Генератор 9 формирует последовательность двухфазных симметричных импульсов, причем импульсы на выходе второй фазы 5 (фиг. Зб) з.адержаны во време ш отно сительно импульсов (фиг. За) на выходе первой фазы на четверть период повторения импульсов. На выходах депшфратора 7 формируются импульсы (фиг. Зе, ж, 3, и) положительной по лярности с относительным сдвигом фа на четверть периода повторения импульсов генератора 9, Импульсы с выходов дешифратора 7 поступают на вхо ды йыборки 6 и осуществляют поочере ную выборку одного из четырех накопителей 2. Таким образом, в течение одного периода повторения импульса в генераторе 9 происходит поочередное обращение к четьфем накопителям Устойчивость работы запоминающего устройства в значительной, мере определяется надежным перекрытием сигнал на входе выборки 6 накопителя 2 сигналами с выходов триггеров 1, т.е. сигнал адреса начинается раньше, а кончается позже сигнала выборки. Перекрытие импульсов (фиг. Зз, и, е, ж) на выходах дешифратора 7 импульсами на выходе триггеров 1 составляет не менее четверти периода повторения импульсов генератора 9. .Запись информации в накопители 2 осуществляется подачей соответствующих.сигналов Запись I и Запись О по входам 4 и 5. При отсутствии сигналов Запись 1 и Запись происходит считьшание информации из накопителей 2, которые объе диняются элементом ИЛИ 8. Таким образом, запись и считывание информации в каждом накопителе осуществляется с частотой импульсов на выходе генератора, а запись и считьшание в запоминающем устройстве в целом - с частотой в четыре раза. выше, чем в известном Г2. Сокращение объема оборудования за счет устранения триггеров промежуточного хранения .записываемой в ЗУ и считываемой из ЗУ информации си хронизатора, а также упрощения преобразователя параллельного кода в последовательный по сравнению с из. вестным составляет примерно 40%. Формула изобретения 1. Запоминающее устройство, содержащее последовательно соединенные 0 триггеры адреса, накопители, входы записи которых являются упрявляющими входами устройства, о т л и ч ало щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит дешифратор, генератор импулБсов и элемент ИЛИ, а триггеры адреса выполнены в виде двухступенчатых триггерой,причем счетньй вход первого двухступенчатого триггера соединен с одним из выходов генератора импульсов и с первым входом дешифратора, второй вход которого соединен с другим выходом генератора импульсов, одни из выходов двухступенчатых триггеров соединены с адресными входами первого и вгорого накопителей, выходы - с адресными входами третьего и четвертого накопителей, а выходы дешифтора соединены со входами выборки накопителей, выходы которых соединены со входами элемента ИЛИ, выход которого является выходом устройства. 2. Устройство по п. 1, отличающееся тем, что двухступенчатЫ11 триггер содерясит три RS-триггера и элемент НЕ, вход которого является счетньпу входом двухступенчатого триггера, а выход соединен с R-входом первого и S-входом второго RS-тригrepoBj нулевой выход первого RS-триггера является импульсным выхгодом двухступенчатого триггера и соединен со вторым S-входом второго и R-входом третьего RS-триггеров, нулевой выход второго RS-триггера соединен с S-входом первого RS-триггера, а единичный выход - с S-БХОДОМ третьего RS-триггера, единичный выход которого является выходом второй ступени двуступенчатого триггера и соединен с R-входом второго RS-триггера, а единичный выход первого RS-трнггера является выходом первой ступени двухступенчатого триггера. Источники инфррмаци:и, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 598120, кл. G 11 С 11/40, 1976. . 2.Патент Беликобритаянн № 1486311,, л. G 04 С, 1977(прототип).

«м

Щ

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU826419A1 |

| Устройство для контроля магистралей в ЭВМ | 1981 |

|

SU970376A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Весоизмерительное устройство для грузов, подвешенных в захвате конвейера | 1991 |

|

SU1806331A3 |

я

«|.

Wjto

tit

1

I I

I I

Ir

tstcs

lO

Ъ

I

li

M

w

I -- 1

О

/I

и

иг.2

Авторы

Даты

1981-07-23—Публикация

1979-10-23—Подача