1

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с последовательной обработкой информации .

По основному авт. св. i- 565326 известно постоянное запоминающее устройство (ПЗУ), содержащее кольце вой регистр сдвига, шины управления элементы И по количеству разрядов кольцевого регистра сдвига и элемен ИЛИ, причем выходы разрядов кольцевого регистра сдвига соединены с информс.ционньми входами элементов И, управляющие входы которых подключены к соответствующим адресным шинам, а выходы соединены со входами элемента ИЛИ, информационные входы кольцевого регистра сдвига подключены к соответствующим шинам логических О.и 1, вход разрешения записи кольцевого регистра сдвига соединен с шиной обращение Ц .

Недостатком этого устройства является равенство количества адресных шин с количеством хранимых чисел в устройстве, так как при большом количестве записанных чисел требуется один дешифратор на такое же количество выходов, для построения которого требуется много оборудования-.

Цель изобретения - упрощение устройства и уменьшение потребляемой мощности устройством.

Указанная цель достигается тем, что в устройство введена вторая группа адресных шин, к которой подключены соответствую1;ие улрэвляюо1ие

0 входы элементов И.

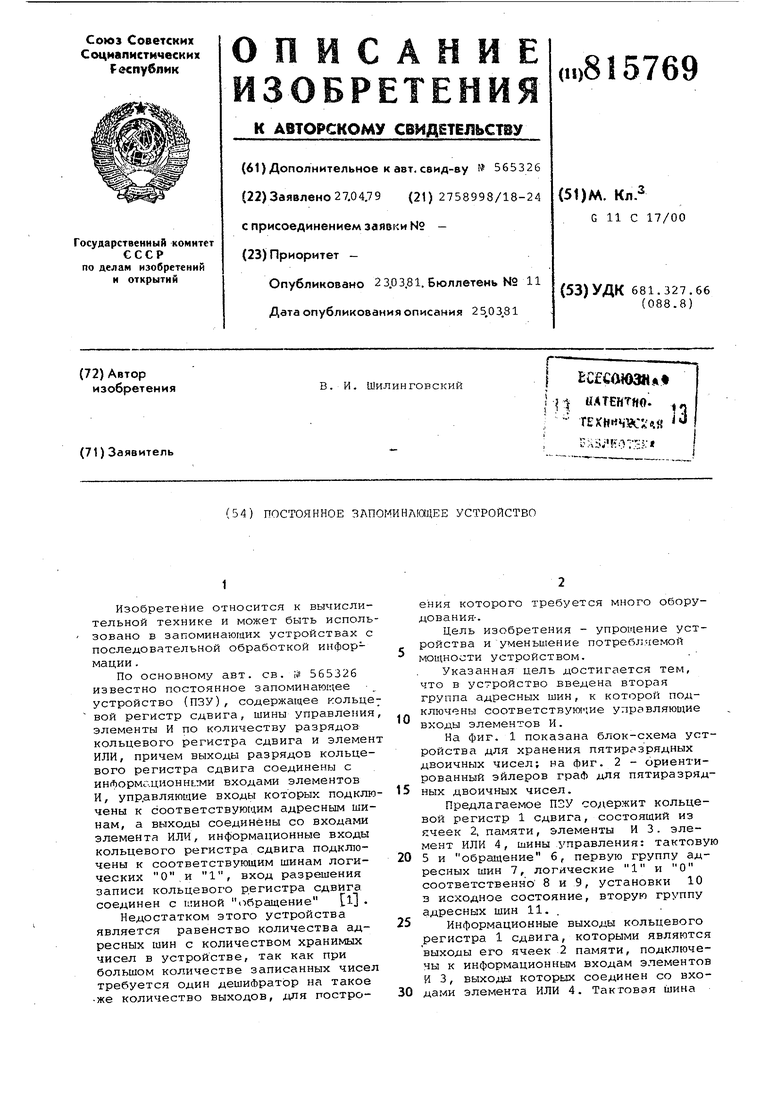

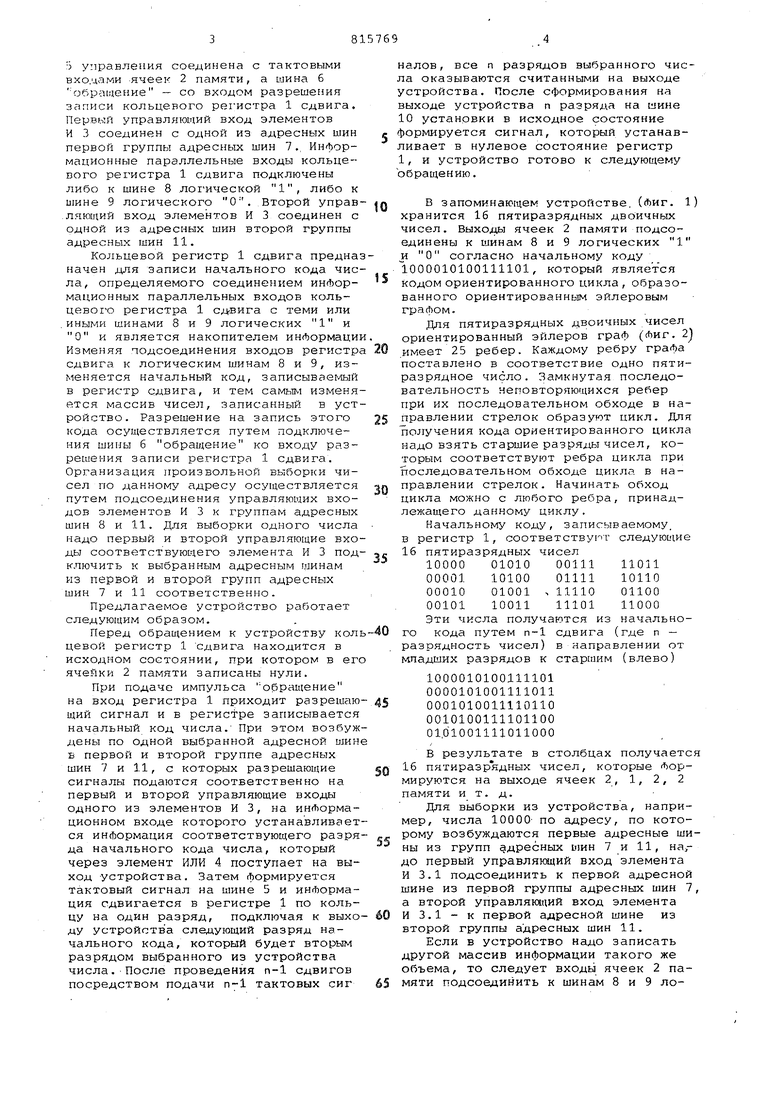

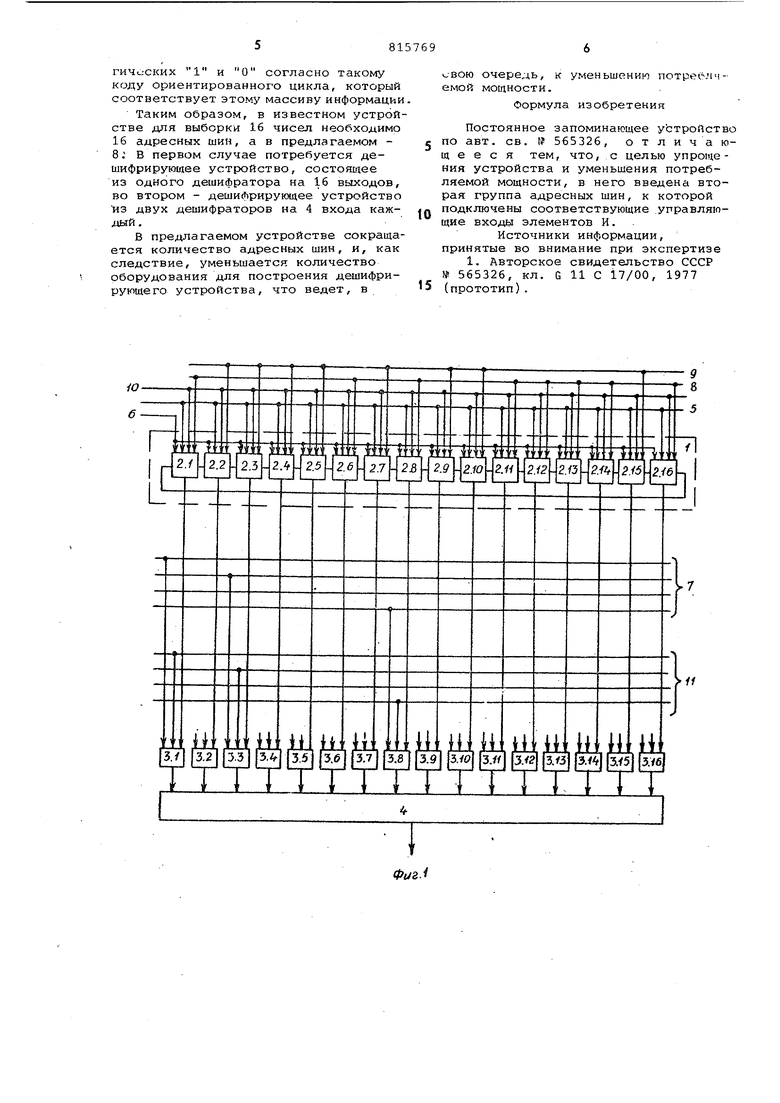

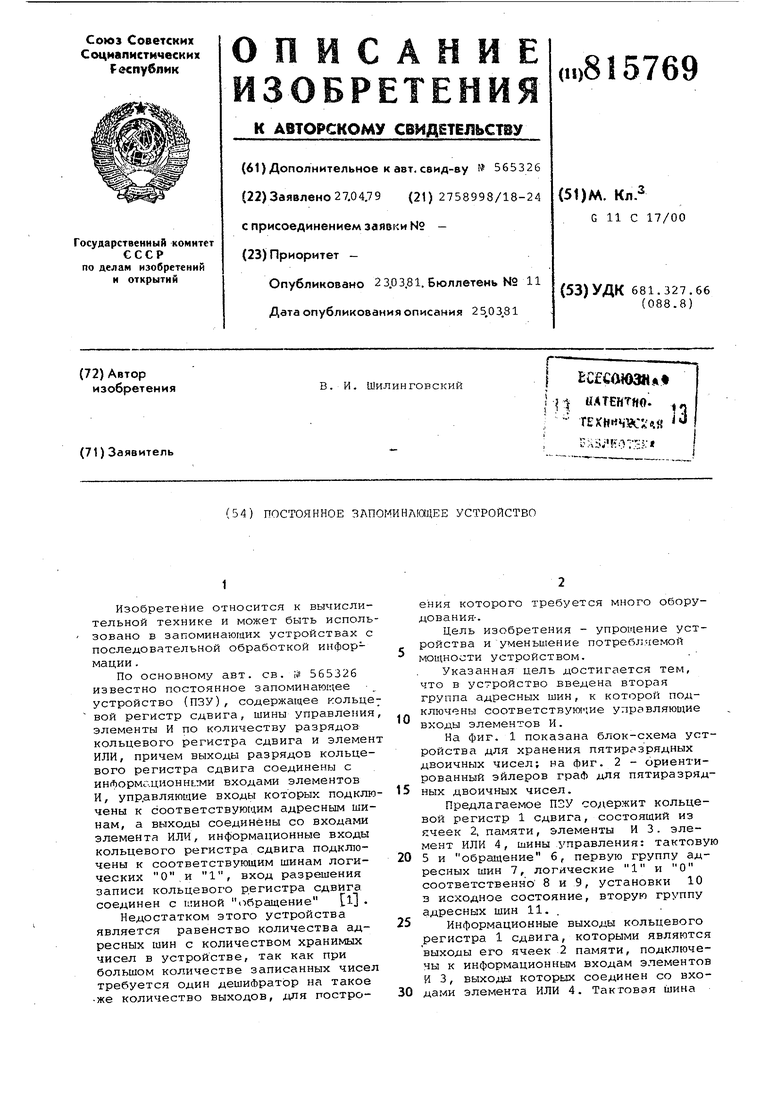

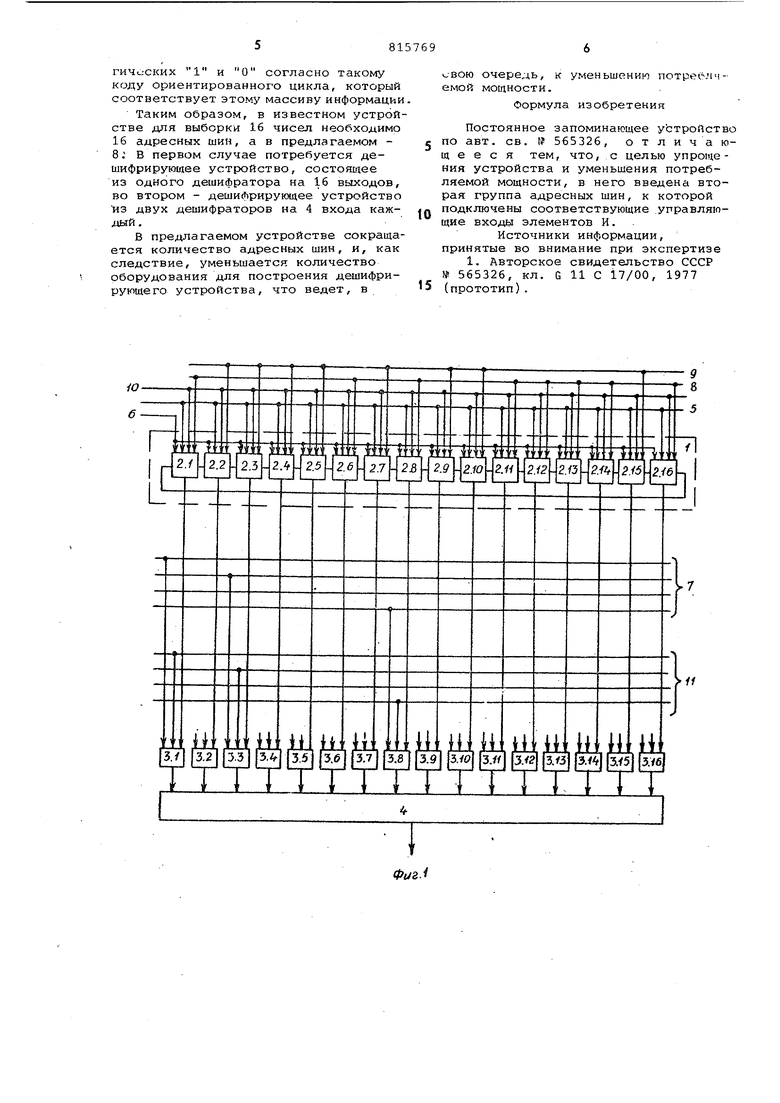

На фиг. 1 показана блок-схема устройства для хранения пятиразрядных двоичных чисел; на фиг. 2 - ориентированный эйлеров граф для пятиразряд5ных двоичных чисел.

Предлагаемое ПЗУ содержит кольцевой регистр 1 сдвига, состоящий из ячеек 2, памяти, элементы И 3. элемент ИЛИ 4, шины управления: тактовую 5 и обращение б, первую группу ад0ресных шин 7, логические 1 и О соответственно 8 и 9, установки 10 в исходное состояние, вторую группу адресных шин 11. .

5

Информационные выходы кольцевого регистра 1 сдвига, которыми являются выходы его ячеек 2 памяти, подключечы к информационным входам элементов И 3, выходы которых соединен со входами элемента ИЛИ 4. Тактовая шина

i управления соегдинена с тактовыми вхо.цами ячеек 2 памяти, а шина 6 обращение - со входом разрешения записи кольцевого рехистра 1 сдвига. Первый управляющий вход элементов И 3 соединен с одной из адресных шин первой группы адресных шин 7., Информационные параллельные входы кольцевого регистра 1 сдвига подключены либо к шине 8 логической 1, либо к шине 9 логического О. Второй управ.ляющий вход элементов И 3 соединен с одной из адресных шин второй группы адресных шин 11.

Кольцевой регистр 1 сдвига предназначен для записи начального кода числа, определяемого соединением информационных параллельных входов кольцевохо регистра 1 сд-вига с теми или

.иными шинами 8 и 9 логических 1 и О и является накопителем информации Изменяя подсоединения входов регистра сдвига к логическим шинам 8 и 9, изменяется начальный код, записываемый в регистр сдвига, и тем самым изменяется массив чисел, записанный в устройство. Разрешение на запись этого кода осуществляется путем подключения шины 6 обращение ко входу разрешения записи регистра 1 сдвига. Организация произвольнорТ выборки чисел по данному адресу осуществляется путем подсоединения управляющих входов элементов И 3 к группам адресных шин 8 и 11. Для выборки одного числа надо первый и второй управляющие входы соответствующего элемента И 3 подключить к выбранным адресным шинам из первой и второй групп адресных шин 7 и 11 соответственно.

Предлагаемое устройство работает следующим образом.

Перед обращением к устройству кольцевой регистр 1 сдвига находится в исходном состоянии, при котором в его ячейки 2 памяти записаны нули.

При подаче импульса обращение на вход регистра 1 приходит разрешгхющий сигнал и в регистре записывается начальный код числа. При этом возбуждены по Одной выбранной адресной шине в первой и второй группе адресных шин 7 и 11, с которых разрешающие сигналы подаются соответственно на первый и второй управляющие входы одного из элементов И 3, на инЛормационном входе которого устанавливается информация соответствующего разряда начального кода числа, который через элемент ИЛИ 4 поступает на выход устройства. Затем формируется Тактовый сигнал на шине 5 и информация сдвигается в регистре 1 по кольцу на один разряд, подключая к выходу устройства следующий разряд начального кода, который будет вторым разрядом выбранного из устройства числа. После проведения п-1 сдвигов посредством подачи п-1 тактовых сиг

налов, все п разрядов выбранного числа оказываются считанными на выходе устройства. После сформирования на выходе устройства п разряда на иине 10 установки в исходное состояние формируется сигнал, который устанавливает в нулевое состояние регистр 1, и устройство готово к следующему обращению.

В запоминающем устройстве. (Лиг. 1 хранится 16 пятиразрядных двоичных чисел. Выхода ячеек 2 памяти подсоединены к шинам 8 и 9 логических 1 JJ О согласно начальному коду loOOOlOlOOllllOl, который является кодом ориентированного цикла , образованного ориентированнь 1М эйлеровым графом.

Для пятиразрядных двоичных чисел ориентированный эйлеров граф (Лиг. 2 имеет 25 ребер. Каждому ребру графа поставлено в соответствие одно пятиразрядное число. Замкнутая последовательность неповторяющихся ребер при их последовательном обходе в направлении стрелок образуют цикл. Для получения кода ориентированного цикла надо взять старшие разряды чисел, которым соответствуют ребра цикла при последовательном обходе цикла в направлении стрелок. Начинать обход цикла можно с любого ребра, принадлежащего данному циклу.

Начальному коду, записываемому, в регистр 1, соответствугч следующие 16 пятиразрядных чисел

10000 01010 00111 11011 00001 10100 01111 10110 00010 01001 , 11110 01100 00101 10011 11101 11000 Эти числа получаются из начального кода путем п-1 сдвига (где п - разрядность чисел) в направлении от младших разрядов к старшим (влево)

1000010100111101 0000101001111011 00,01010011110110 0010100111101100 Ol.OlOOllHOllOOO

в результате в столбцах получаетс 16 пятиразрядных чисел, которые Ьормируются на выходе ячеек 2, 1, 2, 2 памяти и т. д.

Для выборки из устройства, например, числа 10000- по адресу, по которому возбуждаются первые адресные шины из групп адресных шин 7 и 11, наг до первый управлякяций вход элемента И 3.1 подсоединить к первой адресной шине из первой группы адресных шин 7 а второй управлягаций вход элемента И 3.1 - к первой адресной шине из второй группы адресных шин 11.

Если в устройство надо записать другой массив информации такого же объема, то следует входы ячеек 2 памяти подсоединить к шинам 8 и 9 логич.;ских 1 И О согласно такому коду ориентированного цикла, который соответствует этому массиву информации

Таким образом, в известном устройстве для выборки 16 чисел необходимо 16 адресных шин, а в предлагаемом 8; В первом случае потребуется дешифрирующее устройство, состоящее из одного дешифратора на 16 выходов, во втором - дешифрирующее устройство из двух дешифраторов на 4 входа каждый,

В предлагаемом устройстве сокращается количество адресных шин, и, как следствие, уменьшается количество оборудования для построения дешифрирующего устройства, что ведет, в

ч-вою очередь, к уменьшении потреолчемой мощности.

Оормула изобретения

Постоянное запоминающее устройство по авт. св. № 565326, отличающееся тем, что, с целью упрощения устройства и уменьшения потребляемой мощности, в него введена вторая группа адресных шин, к которой подключены соответствующие управляющие входы элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 565326, кл. G 11 С 17/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

| Запоминающее устройство | 1980 |

|

SU900317A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Постоянное запоминающее устройство | 1974 |

|

SU741321A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

Т7| flJjpJ) рл} ( 3j){з 7||зТ||3J| {з

гтттт

I т

Фиг t: ..:

ооооо

Авторы

Даты

1981-03-23—Публикация

1979-04-27—Подача