(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1981 |

|

SU983748A1 |

| Многоканальное буферное запоминающее устройство | 1980 |

|

SU903971A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для регистрации информации | 1985 |

|

SU1273983A2 |

| Устройство для сопряжения | 1981 |

|

SU966687A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1290423A1 |

Изобретение относится к запоминающим устройствам.

Известно буферное запоминающее устройство, содержащее блок приоритета, дешифратор записи, дешифратор считывания, - информационный блок, блоки разрешения записи, блок временной задержки, блок накопителей, блок разрешения считывания 1.

Однако в случае сбоев информационного блока или блока приоритета устройство не возвращается в исходное состояние, при этом может вырабатываться ложный сигнал о заполнении накопителя, т.е. устройство обладает недостаточной помехоустойчивостью.

Наиболее близким к предлагаемому является буферное запоминающее, устройство, содержащее блок сумматоров по модулю два, входы которого подключены к выходам датчика адресов записи, а выходы - к одним входам блока формирования сигнала занятости накопителя, другие входы которого соединены с выходами датчика адресов считывания. При этом датчики адресов записи и считывания можно выполнить в виде

счетчиков или регистров с линейной обратной связью 2.

Однако устройство обладает недостаточной помехоустойчивостью и надежностью, так как при сбоях датчиков адресов записи и считывания устройство не возвращается в исходное состояние, при этом может вырабатываться ложный сигнал о заполнекии накопителя.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что

10 в буферное запоминающее устройство, содержащее накопитель, блок управления, счетчик адресов записи и счетчик адресов считывания, причем одни из входов накопителя подключены к выходам счетчиков адресов записи и считывания, а другой вход и выход являются соответственно входом и выходом устройства, введены схема сравнения и блок синхронизации, причем один вход схемы сравнения подключен к выходу счетчика адресов записи, другой вход -

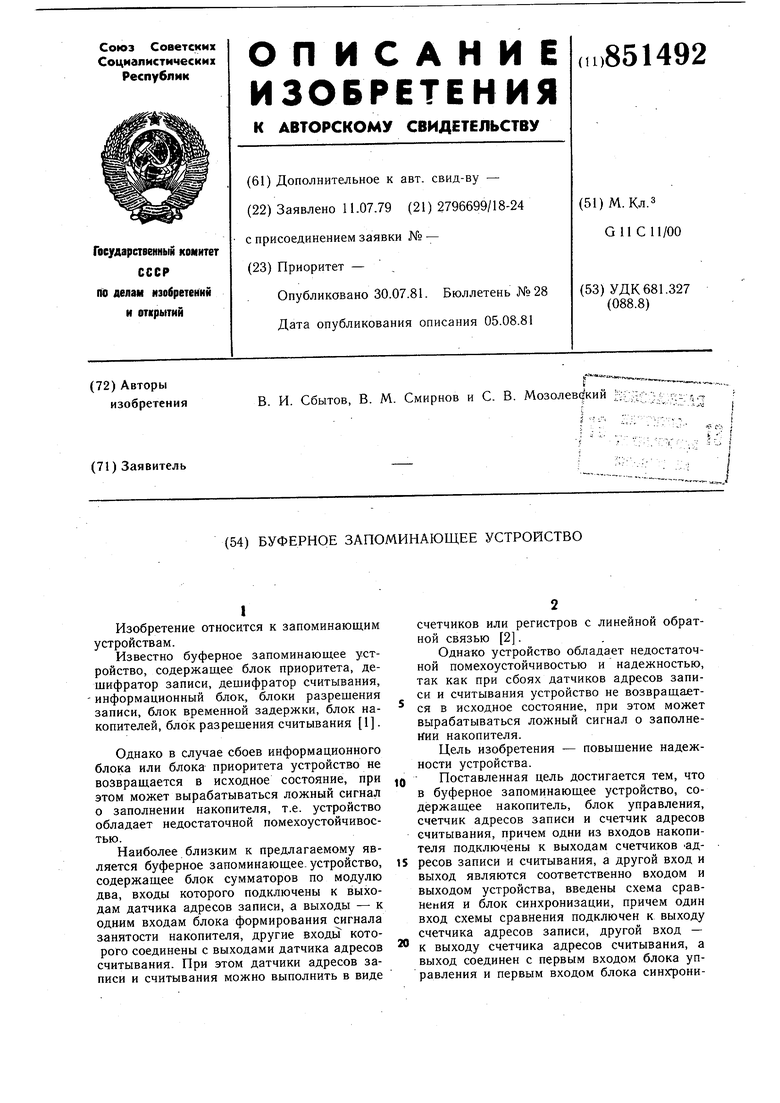

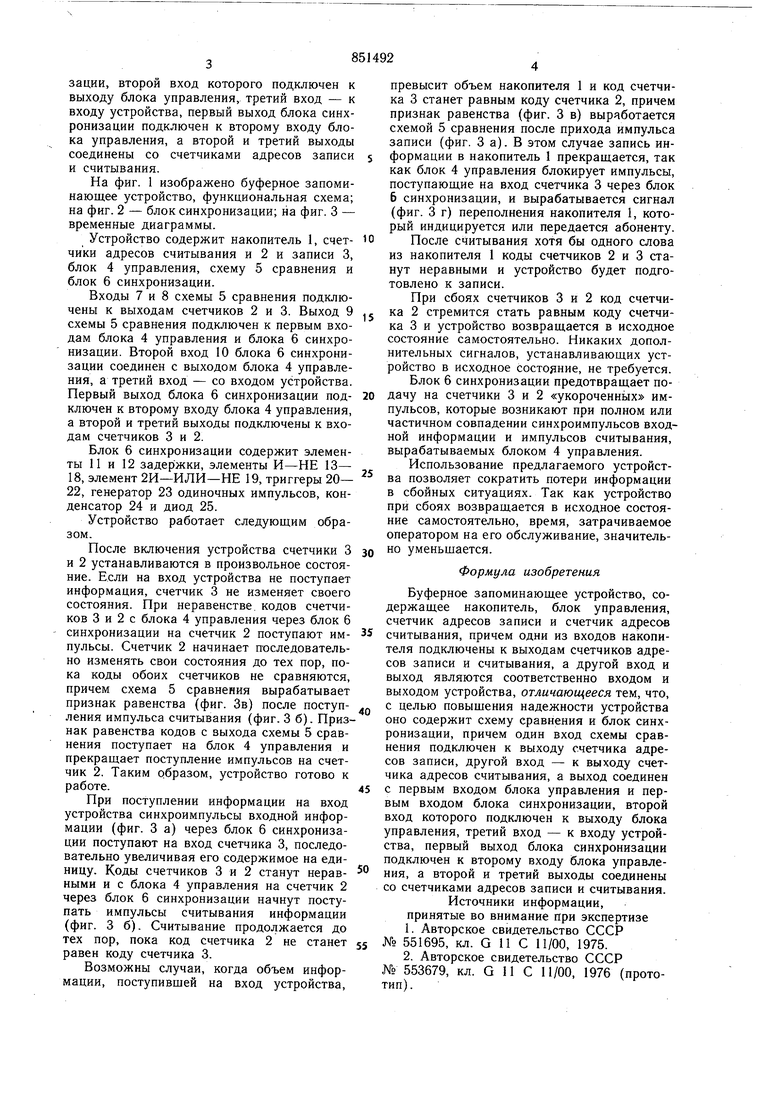

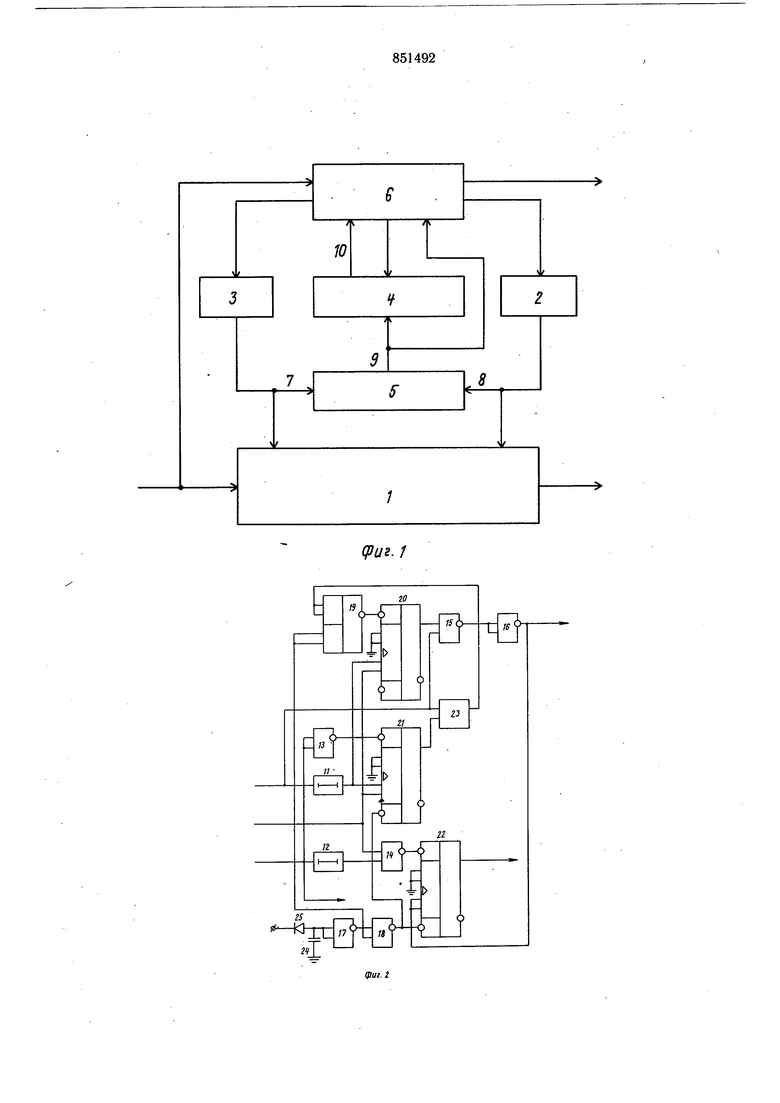

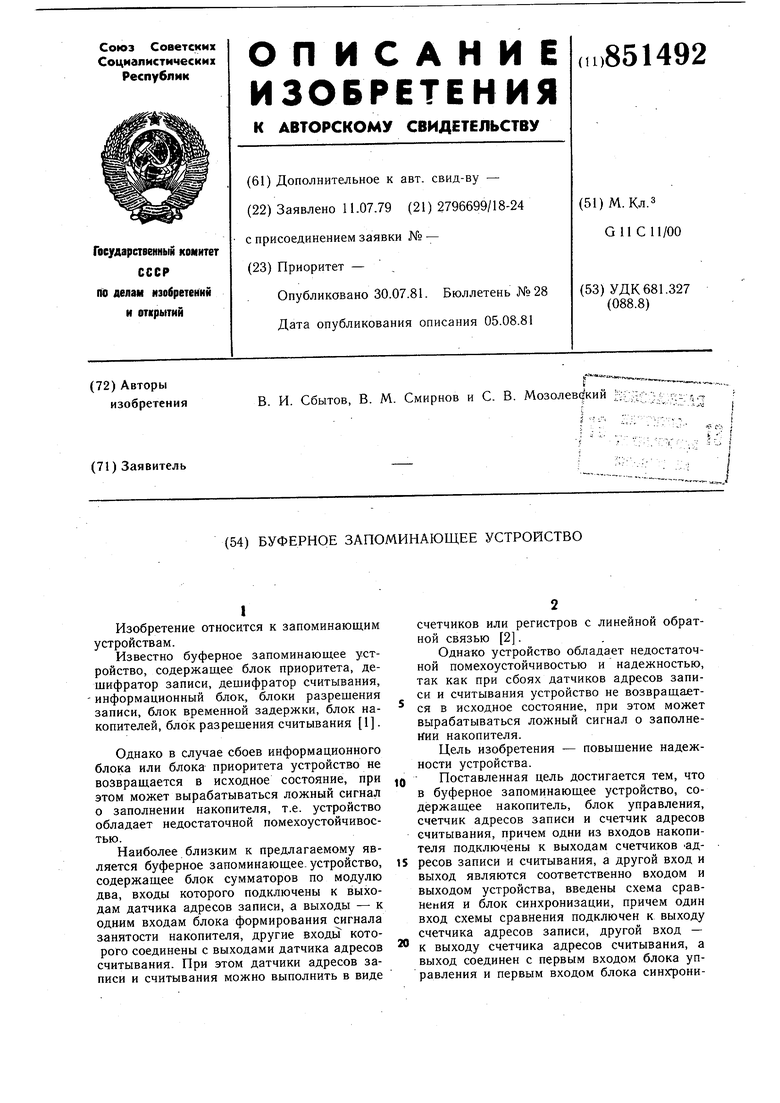

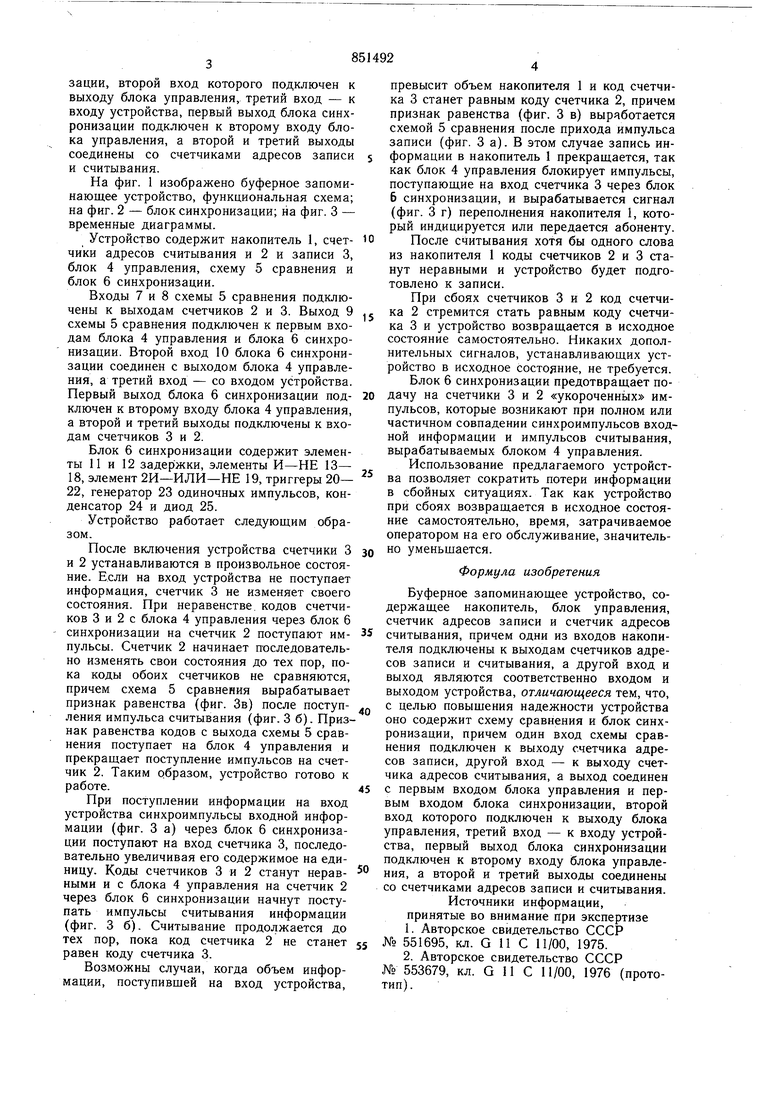

20 к выходу счетчика адресов считывания, а выход соединен с первым входом блока управления и первым входом блока синхронизации, второй вход которого подключен к выходу блока управления, третий вход - к входу устройства, первый выход блока синхронизации подключен к второму входу блока управления, а второй и третий выходы соединены со счетчиками адресов записи и считывания. На фиг. 1 изображено буферное запоминающее устройство, функциональная схема; на фиг. 2 - блок синхронизации; на фиг. 3 - временные диаграммы. Устройство содержит накопитель 1, счетчики адресов считывания и 2 и записи 3, блок 4 управления, схему 5 сравнения и блок 6 синхронизации. Входы 7 и 8 схемы 5 сравнения подключены к выходам счетчиков 2 и 3. Выход 9 схемы 5 сравнения подключен к первым входам блока 4 управления и блока 6 синхронизации. Второй вход 10 блока 6 синхронизации соединен с выходом блока 4 управления, а третий вход - со входом устройства. Первый выход блока 6 синхронизации подключей к второму входу блока 4 управления, а второй и третий выходы подключены к входам счетчиков 3 и 2. Блок 6 синхронизации содержит элементы 11 и 12 задержки, элементы И-НЕ 13- 18, элемент 2И-ИЛИ-НЕ 19, триггеры 20- 22, генератор 23 одиночных импульсов, конденсатор 24 и диод 25. Устройство работает следующим образом. После включения устройства счетчики 3 и 2 устанавливаются в произвольное состояние. Если на вход устройства не поступает информация, счетчик 3 не изменяет своего состояния. При неравенстве, кодов счетчиков 3 и 2 с блока 4 управления через блок 6 синхронизации на счетчик 2 поступают импульсы. Счетчик 2 начинает последовательно изменять свои состояния до тех пор, пока коды обоих счетчиков не сравняются, причем схема 5 сравнения вырабатывает признак равенства (фиг. Зв) после поступления импульса считывания (фиг. 3 б). Признак равенства кодов с выхода схемы 5 сравнения поступает на блок 4 управления и прекращает поступление импульсов на счетчик 2. Таким образом, устройство готово к работе. При поступлении информации на вход устройства синхроимпульсы входной информации (фиг. 3 а) через блок 6 синхронизации поступают на вход счетчика 3, последовательно увеличивая его содержимое на единицу. Коды счетчиков 3 и 2 станут неравными и с блока 4 управления на счетчик 2 через блок б синхронизации начнут поступать импульсы считывания информации (фиг. 3 б). Считывание продолжается до тех пор, пока код счетчика 2 не станет равен коду счетчика 3. Возможны случаи, когда объем информации, поступивщей на вход устройства. превысит объем накопителя 1 и код счетчика 3 станет равным коду счетчика 2, причем признак равенства (фиг. 3 в) выработается схемой 5 сравнения после прихода импульса записи (фиг. 3 а). В этом случае запись информации в накопитель 1 прекращается, так как блок 4 управления блокирует импульсы, поступающие на вход счетчика 3 через блок б синхронизации, и вырабатывается сигнал (фиг. 3 г) переполнения накопителя 1, который индицируется или передается абоненту. После считывания хотя бы одного слова из накопителя 1 коды счетчиков 2 и 3 станут неравными и устройство будет подготовлено к записи. При сбоях счетчиков 3 и 2 код счетчика 2 стремится стать равным коду счетчика 3 и устройство возвращается в исходное состояние самостоятельно. Никаких дополнительных сигналов, устанавливающих устройство в исходное состояние, не требуется. Блок 6 синхронизации предотвращает подачу на счетчики 3 и 2 «укороченных импульсов, которые возникают при полном или частичном совпадении синхроимпульсов входной информации и импульсов считывания, вырабатываемых блоком 4 управления. Использование предлагаемого устройства позволяет сократить потери информации в сбойных ситуациях. Так как устройство при сбоях возвращается в исходное состояние самостоятельно, время, затрачиваемое оператором на его обслуживание, значительно уменьщается. Формула изобретения Буферное запоминающее устройство, содержащее накопитель, блок управления, счетчик адресов записи и счетчик адресов считывания, причем одни из входов накопителя подключены к выходам счетчиков адресов записи и считывания, а другой вход и выход являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повыщения надежности устройства оно содержит схему сравнения и блок синхронизации, причем один вход схемы сравнения подключен к выходу счетчика адресов записи, другой вход - к выходу счетчика адресов считывания, а выход соединен с первым входом блока управления и первым входом блока синхронизации, второй вход которого подключен к выходу блока управления, третий вход - к входу устройства, первый выход блока синхронизации подключен к второму входу блока управления, а второй и третий выходы соединены со счетчиками адресов записи и считывания. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 551695, кл. G 11 С 11/00, 1975. 2.Авторское свидетельство СССР № 553679, кл. G 11 С 11/00, 1976 (прототип).

(риг. 1

гш

п

п п

п

IT

лп

iv

L

(риг.З

Авторы

Даты

1981-07-30—Публикация

1979-07-11—Подача