I

Изобретение относится к вычислительной технике, в частности к устройствам буферизации данных, и может быть использовано в системах обработки, данных, а также в системах накопления и передачи информации.

Цель изобретения - повьшение надежности устройства.

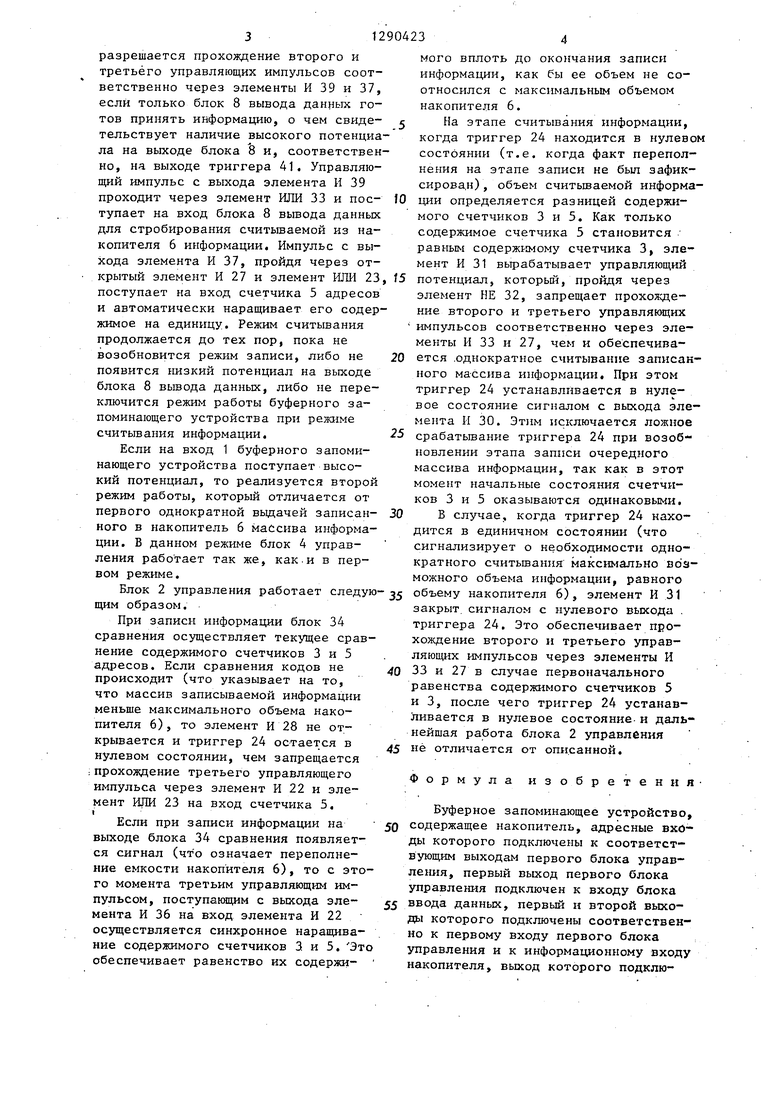

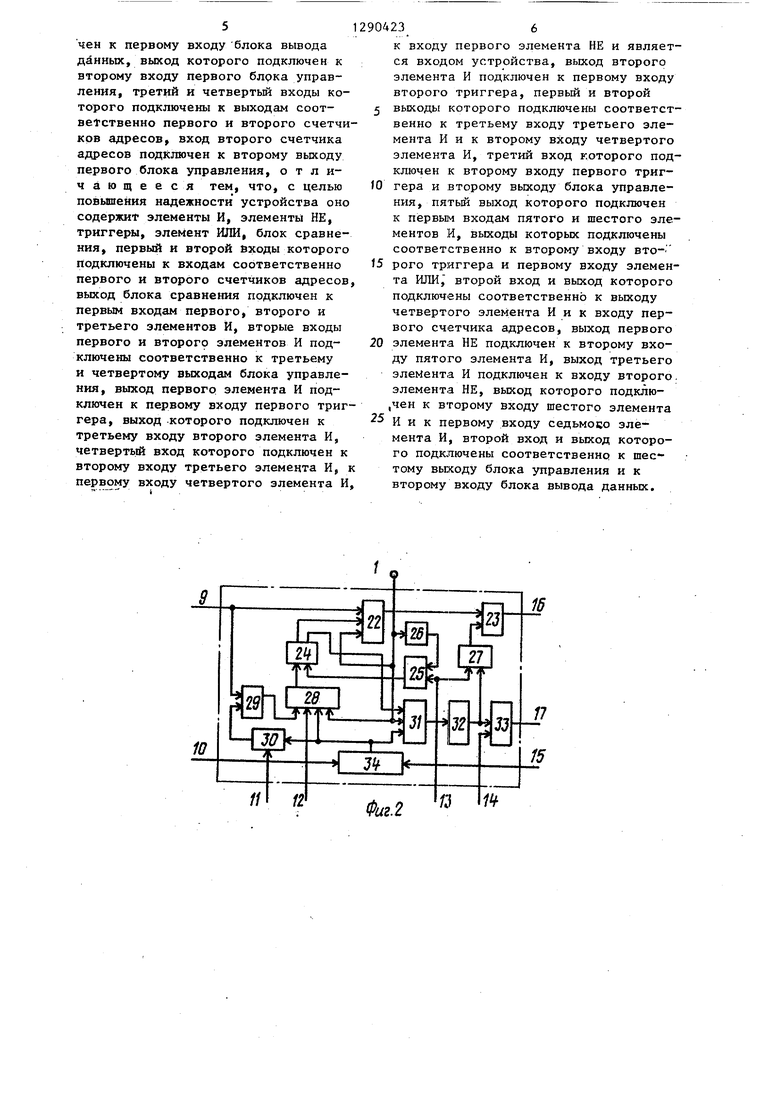

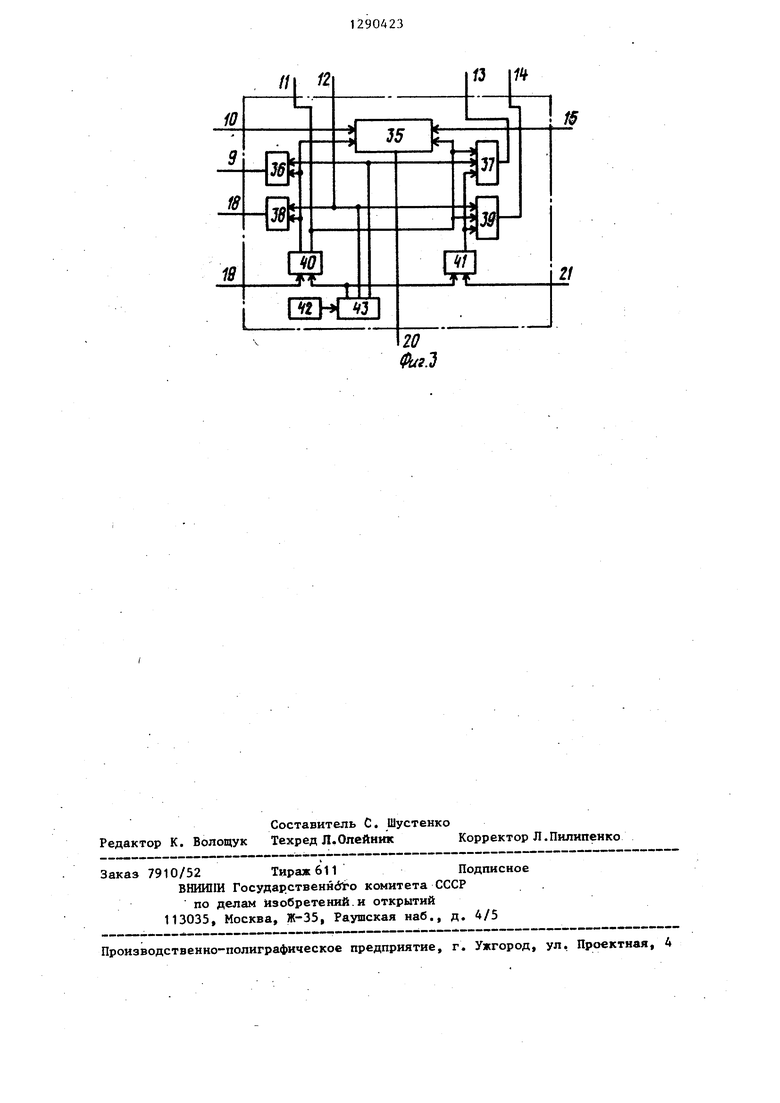

На фиг. 1 приведена структурная

схема устройства; на фиг. 2 и 3 - с труктур ные схемы блоков управления

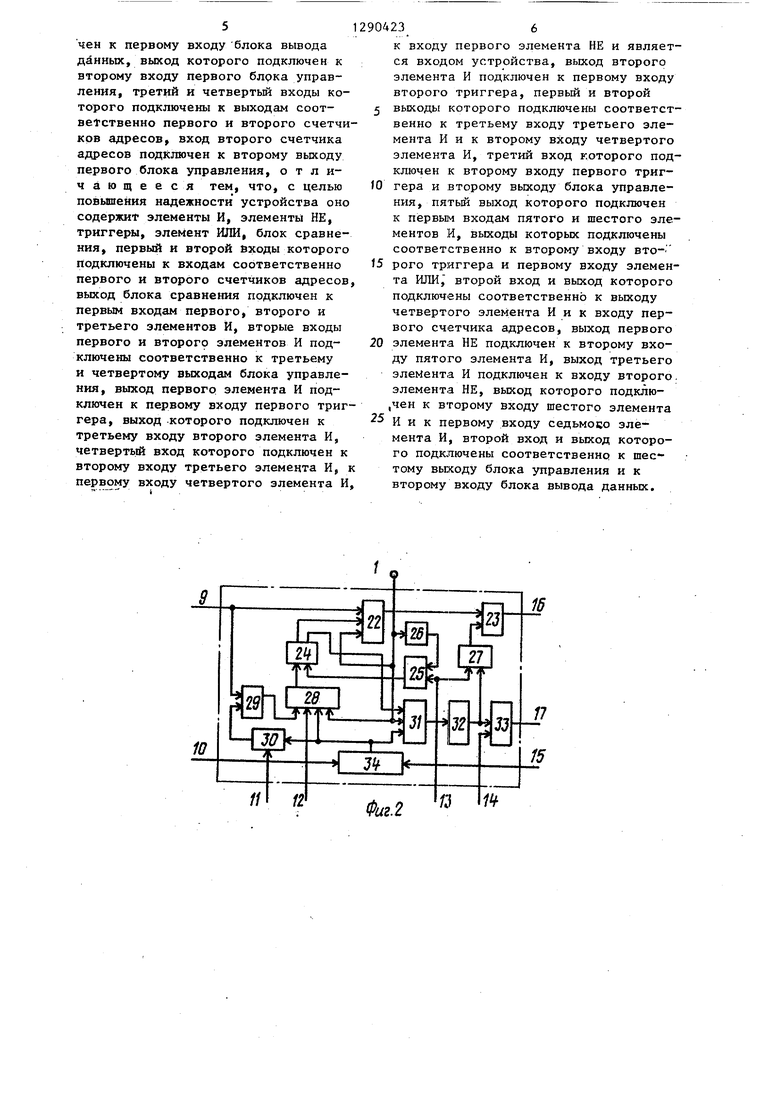

Буферное запоминающее устройство содержит управляющий вход 1, блок 2 управления, счетчик 3 адресов, блок 4 управления, счетчик 5 адресов, накопитель 6, блок 7 ввода данных, блок 8 вывода данных, входы 9-15 блока 2 управления, выходы 16 и 17 блока 2 управления, выход 18, вход 19, адресные выходы 20, вход 21 блока 4 управления.

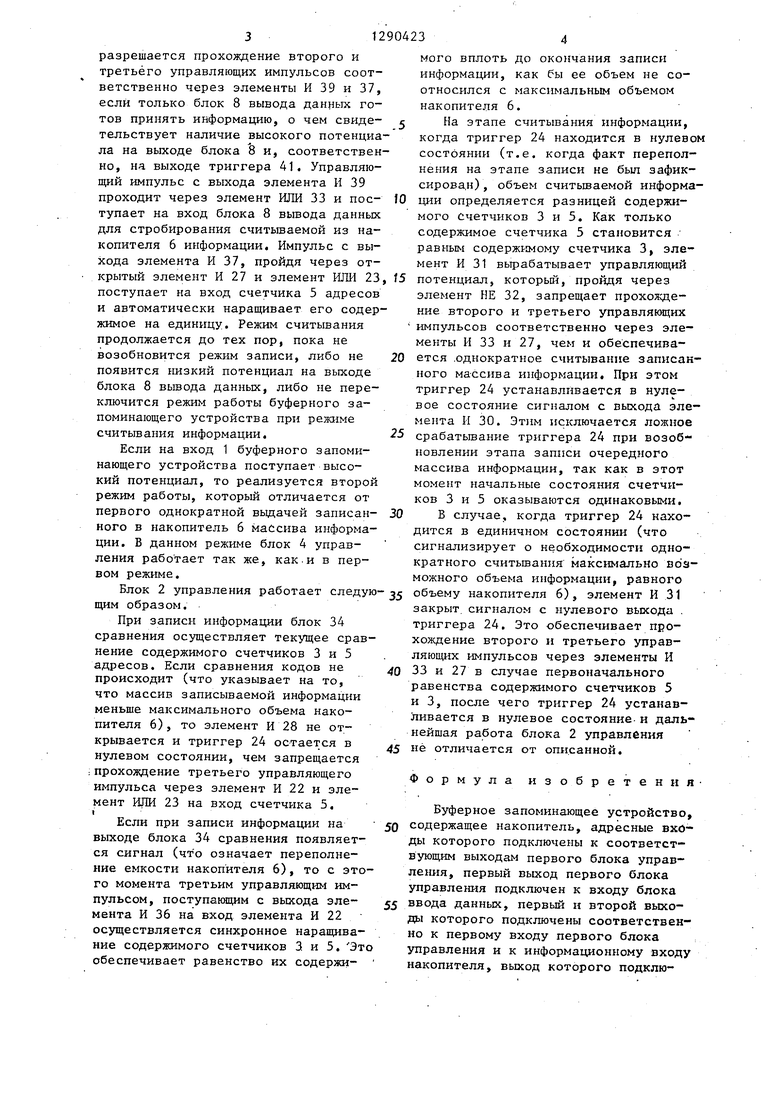

Блок 2 управления (фиг. 2) содержит элемент И 22, элемент ИЛИ 23, триггер 24, элемент И 25, элемент НЕ 26, элементы И 27 и 28, триггер 29, элементы И 30 и 31, элемент НЕ 32, элемент И 33 и блок 34 сравнения. .

Блок 4 управления (фиг. 3) содержит мультиплексор 35, элементы И 36-39, триггеры 40 и 41, генера- :тор 42 импульсов, распределитель 43 импульсов.

Блок 2 управления предназначен для включения одного из двух режимов работы буферного запоминающего устройства, выбор которого определяется управляющим потенциалом, поступающим на вход 1. Первый режим работы обеспечивает приоритетную запись информации в накопитель 6 и многократное ее считывание в разрешенные моменты времени. Во втором режиме обеспечивается также приоритетная запись информации в накопитель 6, но с однократным считыванием массива информации, объем которого определяется разницей содержимого счетчиков 3 и 5 адресов. Счетчик 3 адресов предназначен для формирования адреса ячеек накопителя 6, в которые осуществляется запись информации. Счетчик 5 адресов предназначен для формирования адреса ячеек накопителя 6, из которых информация, считывается. БЛОК 4 управления предназначен для выбора режима записи или считывания информации для синхронизации работы блоков ввода и вывода данных, а также обеспечивает соот1

;

20

25

2904232

ветствующее подключение выходов счет чиков 3 и 5 адресов к адресным входам накопителя 6, Накопитель 6 предназначен для временного запоми-

5 нания и хранения информации.

Устройство работает следующим образом.

Если на вход 1 буферного запоминающего устройства поступает низкий

10 управляющий потенциал, то реализуется первый режим работы устройства. При этом в блоке 4 управления с помощью генератора 42 импульсов и трехтактного распределителя 43 им 5 пульсов цикл::чески формируются три, неперекрывающихся во времени управляющих импульса. Первым по времени управляющим импульсом осуществляется циклический опрос состояний блока 7 ввода данных и блока 8 вывода данных, в результате чего триггеры 40 и 41 устанавливаются в одинаковые состояния. При единичном состоянии триггера 40 реализуется этап записи информации, а при нулевом его состоянии и единичном состоянии триггера 41 - этап считьша- i ния информации.

При реализации режима записи открывается соответствующий вход мультиплексора 35, в результате чего выход счетчика 3 подключается к ад- ресному входу накопителя 6. В то же время открываются элементы И 38

35 и 36, чем обеспечивается прохождение второго и третьего управлякнцих импульсов, формируемых распределителем 43 импульсов, соответственно на входы блока 7 и счетчика 3. По

40 второму управляющему импульсу, формируемому элементом И 38, блок 7 ввода данных обеспечивает вьвдачу в накопитель 6 записываемой информации и сигнала записи. По третьему уп45 равляющему импульсу, формируемому элементом И 36, осуществляется наращивание на единицу счетчика 3 адресов. В случае отсутствия информации, подлежащей вводу в буферное за50 поминающее устройство, на первом выходе блока 7 устанавливается низкий потенциал, в результате чего триггер 40 переключается в нулевое состояние. Этим разрешается реали55 эация ре:жима многократного считыва- ння информации. В этом случае через мультиплексор 35 адресный вход накопители 6 подключается к выходу счетчика 5 адресов. В то же время

30

разрешается прохождение второго и третьего управляющих импульсов соответственно через элементы И 39 и 37, если только блок 8 вывода данных готов принять информацию, о чем свиде- тельствует наличие высокого потенциала на выходе блока 8 и, соответственно, на выходе триггера 41, Управляющий импульс с выхода элемента И 39 проходит через элемент ИЛИ 33 и пос- тупает на вход блока 8 вывода данных для стробирования считываемой из накопителя 6 информации. Импульс с выхода элемента И 37, пройдя через открытый элемент И 27 и элемент ИЛИ 23 поступает на вход счетчика 5 адресов и автоматически наращивает его содержимое на единицу. Режим считывания продолжается до тех пор, пока не возобновится режим записи, либо не появится низкий потенциал на выходе блока 8 вывода данных, либо не переключится режим работы буферного запоминающего устройства при режиме считьтания информации,

Если на вход 1 буферного запоминающего устройства поступает высокий потенциал, то реализуется второй режим работы, который отличается от первого однократной выдачей записан- ного в накопитель 6 массива информации. В данном режиме блок 4 управления работает так же, как.и в первом режиме.

Блок 2 управления работает следую щим образом.

При записи информации блок 34 сравнения осуществляет текущее сравнение содержимого счетчиков 3 и 5 адресов. Если сравнения кодов не происходит (что указывает на то, что массив записываемой информации меньше максимального объема накопителя 6), то элемент И 28 не открывается и триггер 24 остается в нулевом состоянии, чем запрещается ;прохождение третьего управляющего импульса через элемент И 22 и элемент ИЛИ 23 на вход счетчика 5, I

Если при записи информации на

выходе блока 34 сравнения появляется сигнал (чт о означает переполнение емкости накопителя 6), то с этого момента третьим управляющим импульсом, поступаклцим с выхода эле- мента И 36 на вход элемента И 22 осуществляется синхронное наращивание содержимого счетчиков 3 и 5. Это обеспечивает равенство их содержи

fO J5 0 5

0

0

0

5

мого вплоть до окончания записи информации, как бы ее объем не соотносился с максимальным объемом накопителя 6.

На этапе считывания информации, когда триггер 24 находится в нулевом состоянии (т.е. когда факт переполнения на этапе записи не был зафиксирован) , объем считьшаемой информации определяется разницей содержимого Счетчиков 3 и 5, Как только содержимое счетчика 5 становится равным содержимому счетчика 3, элемент И 31 вырабатывает управляющий потенциал, который, пройдя через элемент НЕ 32, запрещает прохождение второго и третьего управляющих импульсов соответственно через элементы И 33 и 27, чем и обеспечивается .однократное считывание записанного массива информации. При этом триггер 24 устанавливается в нулевое состояние сигналом с выхода элемента И 30. Этим исключается ложное срабатывание триггера 24 при возобновлении этапа записи очередного массива информации, так как в этот момент начальные состояния счетчиков 3 и 5 оказываются одинаковыми,

В случае, когда триггер 24 находится в единичном состоянии (что сигнализирует о необходимости однократного считьтания максимально возможного объема информации, равного объему накопителя 6), элемент И 31 закрыт сигналом с нулевого выхода . триггера 24. Это обеспечивает прохождение второго и третьего управляющих импульсов через элементы И 33 и 27 в случае первоначального равенства содержимого счетчиков 5 и 3, после чего триггер 24 устанавливается в нулевое состояние, и дальнейшая работа блока 2 управления не отличается от описанной.

Формула изобретенияБуферное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к соответствующим выходам первого блока управ- леш1я, первый выход первого блока управления подключен к входу блока ввода данных, первый и второй выходы которого подключены соответственно к первому входу первого блока управления и к информационному входу накопителя, выход которого подключен к первому входу блока вывода данных, выход которого подключен к второму входу первого блока управления, третий и четвертьй входы которого подключены к выходам соответственно первого и второго счетчиков адресов, вход второго счетчика адресов подключен к второму выходу первого блока управления, отличающееся тем, что, с целью повышения надежности устройства оно содержит элементы И, элементы НЕ, триггеры, элемент ИЛИ, блок сравнения, первый и второй йходы которого подключены к входам соответственно первого и второго счетчиков адресов выход блока сравнения подключен к первым входам первого, второго и третьего элементов И, вторые входы первого и второго элементов И подключены соответственно к третьему и четвертому выходам блока управления, выход первого элемента И подключен к первому входу первого триггера, выход которого подключен к третьему входу второго элемента И, четвертьй вход которого подключен к второму входу третьего элемента И, первому входу четвертого элемента И

,

2904236

к входу первого элемента НЕ и является входом устройства, выход второго элемента И подключен к первому входу второго триггера, первый и второй 5 выходы которого подключены соответственно к третьему входу третьего элемента И и к второму входу четвертого элемента И, третий вход которого подключен к второму входу первого триг- tO гера и второму выходу блока управления, пятый выход которого подключен к первьим входам пятого и шестого элементов И, выходы которых подключены соответственно к второму входу вто-

15 рого триггера и первому входу элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу четвертого элемента И и к входу первого счетчика адресов, выход первого

20 элемента НЕ подключен к второму входу пятого элемента И, выход третьего элемента И подключен к входу второго, элемента НЕ, выход которого подклю- ,чен к второму входу шестого элемента

25 и и к первому входу седьмосо элемента И, второй вход и выход которого подключены соответственно к шестому вьЕкоду блока управления и к второму входу блока вывода данных.

//I 12

« П

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

Изобретение относится к вычислительной технике, в частности к устройствам буферизации данных, и может быть использовано в системах обработки данных и в системах накопления и передачи информации. Цель изобретения - повьшение надежности буферного запоминающего устройства. Устройство содержит управляющий вход ,1, блок 2 управления, счетчик 3 адресов, блок 4 управления, счетчик 5 адресов, накопитель 6, блок 7 ввода данных, блок 8 вывода данных Устройство работает в двух режимах ;. зада ваемых блоком 2. Первый режим Обеспечивает приоритетную запись данных в накопитель 6 и многократное считывание в разрешенные моменты времени. Второй режим обеспечивает приоритетную запись данных в накопитель 6 и однократное считывание массива дан- ньрс, объем которого определяется значениями счетчиков 3 и 5 адресов, Блок 4 управления организует работу, накопителя 6 в режиме записи и считывания и синхронизирует работу блоков 7 и 8 ввода и вывода данных и счетчиков 3 и 5 адресов. Кроме того, блок 4 осуществляет подключение выхо- до счетчиков 3 и 5 к адресным входам накопителя 6. 3 ил. i W ю со

| Устройство для сопряжения блоков памяти | 1977 |

|

SU624231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-06-25—Подача