(54) УСТРОПСТЮ ДЛЯ НОРМАЛИЗАЦИИ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

| Устройство для нормализации чисел | 1980 |

|

SU862139A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал | 1983 |

|

SU1124452A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

Изобретение относится к вычислительной технике. Известны устройства нормгшизации сигналов, содержащие блок преоб разования с.игналов в цифровую форму подключенный к регистрам сдвига, комбинационный су1«олатор, соединенный со счетчиками, и блок памяти. Нормализация сигнала осуществляется за счет изменения коэффициента передачи в нужное число раз ij и Недостатком данных устройств яв ляется сложность их выполнения для обеспечения точного измерения параметров сигнала и соответствующего измерения коэффициента передачи. Наиболее близким к предлагаемому по технической сущности является устройство для нормализации, содержащее ансшого-цифровой преобразователь, соединенный с регистрами сдвиг подключенными к комбинационному сумматору, первый и второй цифроана логовые преобразователи, причем вхо одного из них подключены к выходу комбинсщионного сумматора, а второго - к выходам регистров сдвига, а выходы цифроаналоговых преобразователей подключены к выходам делителя напряжений. Делитель напряжений в совокупности с двумя цифроаналоговыми преобразователями образуют блок деления. Нормгшизация сигнгша осуществляется делителем напряжения для которого , сигнал подвергается обратному преобразованию в аналоговую форму, а коэффициент деления определяется в числовой форме 3. Недостатком данного устройства является также сложность его выполнения за счет непосредственного соединения регистров сдвига с комбинационным сумматором. Общее число соединений равно n,N (где п - число регистров сдвига, N - число отсчетов информации). Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройство для нормализации сигналов, содержащем регистры сдвига, блок деления и сумматор, причем входы регистров сдвига соединены с соответствующими разрядными входами устройства, выход блока деления является выходом устройства, сумматор выполнен накапливающим, входы его соединены с соответствующими разрядными входами устройства, первая группа входов блока деления соединена с выходами регистров сдвига, а вторая группа входов блока деления - с выходс1ми сумматора.

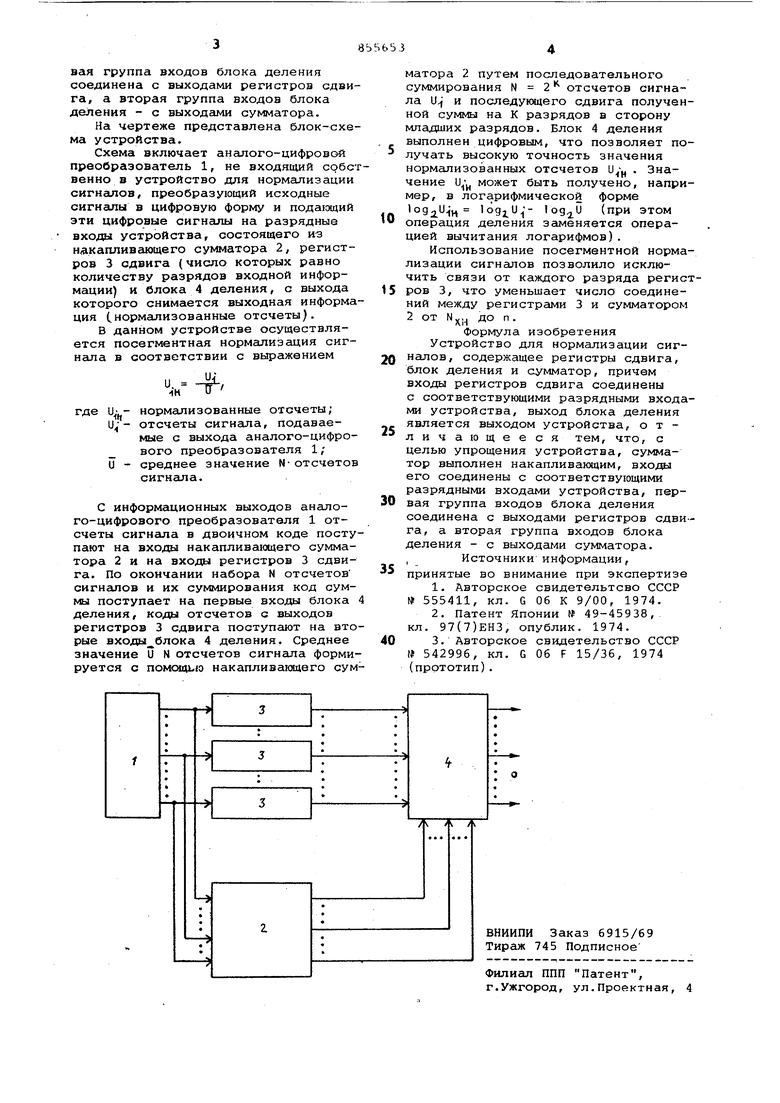

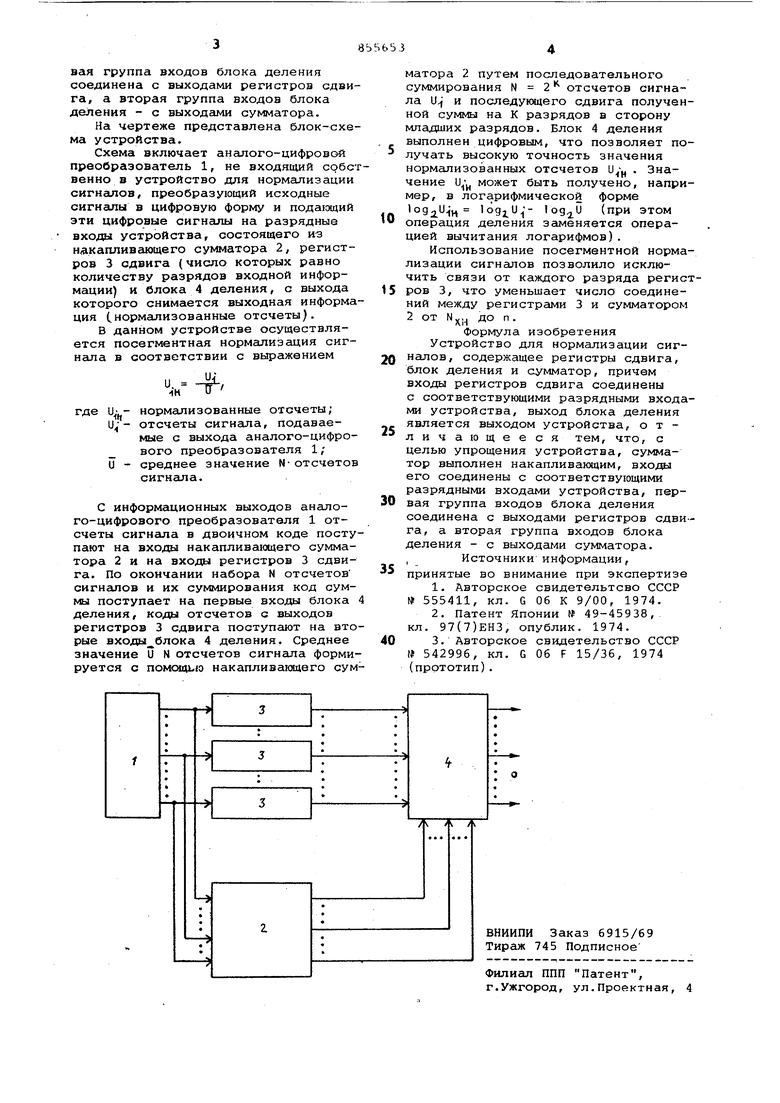

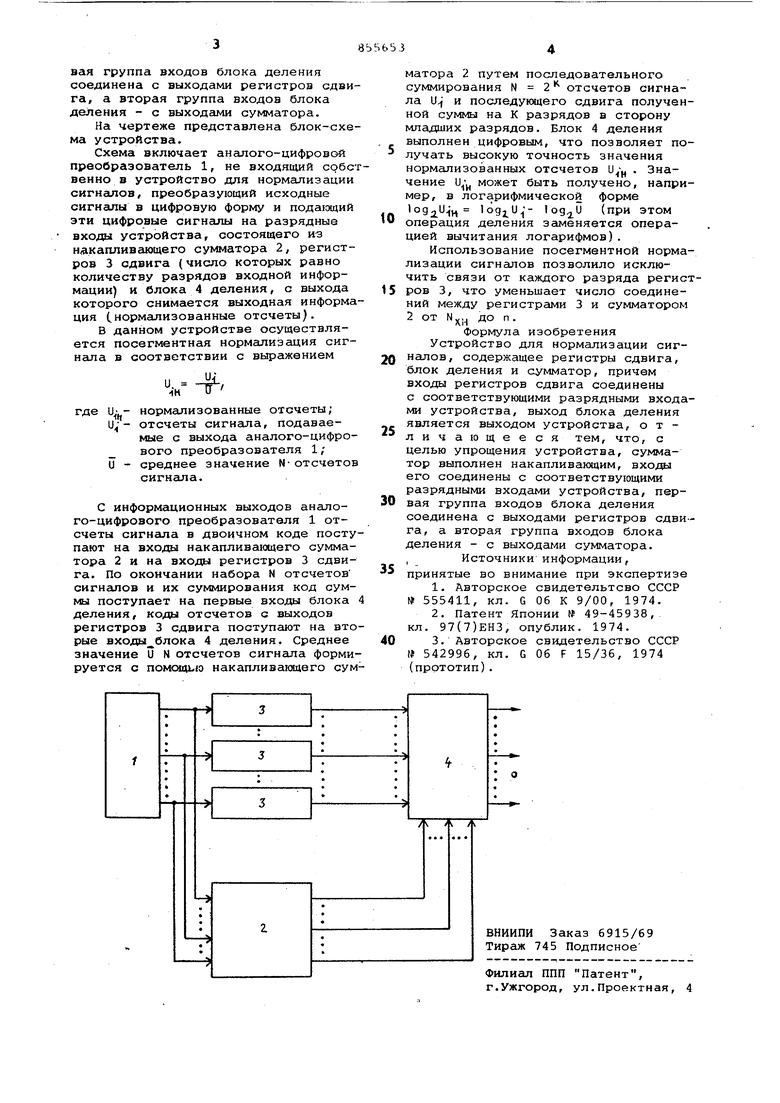

На чертеже представлена блок-схема устройства.

Схема включает аналого-цифровой преобразователь 1, не входящий собсвенно в устройство для нормализации сигнешов, преобразующий исходные сигнсшы в цифровую форму и подающий эти цифровые сигналы на разрядные входы устройства, состоящего из ндкапливающего сумматора 2, регистров 3 сдвига (число которых равно количеству разрядов входной информации) и блока 4 деления, с выхода которого снимается выходная информация С нормализованные отсчеты).

В данном устройстве осуществляется посегментная нормгипиэация сигнала в соответствии с выражением

и. -iH С1

IH

где нормализованные отсчеты;

отсчеты сигнала, подаваемые с выхода аналого-цифро вого преобразователя 1;

и - среднее значение N-отсчетов сигнала.

С информационных выходов аналого-цифрового преобразователя 1 отсчеты сигнсша в двоичном коде поступают на входы накапливающего сумматора 2 и на входы регистров 3 сдвига. По окончании набора N отсчетов сигналов и их суммирования код суммы поступает на первые входы блока деления, коды отсчетов с выходов регистров 3 сдвига поступгиот на вторые входы блока 4 деления. Среднее значение U N отсчетов сигнала формируется с помощью накапливающего сумматера 2 путем последовательного суммирования N 2 отсчетов сигнала и последующего сдвига полученной суммы на К разрядов в сторону младших разрядов. Блок 4 деления выполнен цифровым, что позволяет получать высокую точность значения нормализованных отсчетов . Значение может быть получено, например, в логарифмической форме (при этом операция деления заменяется операцией вычитания логарифмов).

Использование посегментной нормализации сигналов позволило исключить связи от каждого разряда регистров 3, что уменьшает число соединений между регистрами 3 и сумматором 2 от NVM до п.

Л IT

Формула изобретения Устройство для нормализации сигналов, содержащее регистры сдвига, блок деления и сумматор, причем входы регистров сдвига соединены с соответствующими разрядными входами устройства, выход блока деления является выходом устройства, отличающееся тем, что, с целью упрощения устройства, сумматор выполнен накапливающим, входаа его соединены с соответствующими разрядными входами устройства, первая группа входов блока деления соединена с выходами регистров сдвига, а вторая группа входов блока деления - с выходами сумматора.

Источники информации, принятые во внимание при экспертизе

7

Авторы

Даты

1981-08-15—Публикация

1979-05-25—Подача