(54) УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

-,. , . , . 1 , .

Изобретение относится к области цифррвой вычислительной техники и : цожет быть использовано для, по строе НИИ процессоров, работающих в регшьвом масштабе времени, и процессоров с комплексной арифметикой.

Извастно арифметико-логическое устройство для обработки символьной информации flj , которое содержит блок сдвигателя, который содержит схемы для выполнения операций определения пятиразрядного двоичного кода Б позиции крайне левой единицы в слове В. Если В (старший разряд имеет единичное значение), то . Если , то (старший разряд кода ). При выполнении рассматриваемой операции используется схема комбинационного сдвигателя.

Недостатком известного устройства является низкая производительность, обусловленная аппаратно-программным выполнением алгоритма нормализации, выполнение которого только аппаратурными средствами приводит к сложным комбинационным схемам.

Наиболее близким техническим решением к изобретению является устройство для нормализации чисел 2}

Для получения в прототипе сумм, которые имейт лишь одну значащуй единицу в (m+n) разряде регистра множителя-остатка, процесс сравнения разряда () накапливамщего сумматора для получения нормализованных чисел необходимо повторить н раз .,, Л; .;, ; ,. . . .

10

N - 2 ЙвИ-п). - 2(),

где п : количество разрядов мантиссы суммы, расположенной в разрядах (т%1 .,., 1Я+п) накапливающего суммато15ра и регистра множителя-остатка.

Усредненное Время нормализации при равномерном распределении вероятностей появления различных Чисел равно. ;..:. ; , . - : . .

20

:-.

где t(- время сравнения разряда (ffl+1) нахагшиваюшего сумматора с

25 константой. В связи с этим плавающая занятай не нашла применения в процессорах, равотаювйих в реальном масштабе времени, несмотря на то, что она значительно расширяет ди30намиЧесКйй диапазон чисел.

Целью изобретения является сокращение времени нормализации путем незначительного увеличения аппаратурных затрат, которые позволяют определить двоичный код номера позиции первой значащей единицы слева в мантиссе полученной суммы, который, в свою .очередь, позволяет получить порядок нормализованной суммы и осуществить быстрый сдвиг . влево с частотой задающего генератора.

Поставленная цель достигается тем что устройство для нормализации чисел, содержащее буферной регистр памяти, накапливающий сумматор, регистр множителя остатка, триггер знака, первый дешифратор, триггер переполнения порядка, триггер исчезновения порядка, второй дешифратор, триггер переполнения при делении, счетчик сдвигов, причем первая и вторая группы выходов буферного регистра. памяти соединены соответственно с входаг. первой и второй групп накапливаюшего сумматора и регистра множитеЛя-остатка, а третья группа выходов соединена с третьей группой входов регистра множителя-остатка, первый выход накапливающего cyMi iaтора соединен с входом триггера знака и первым входом первого дешифра -; тора, второй вход которого соединен с втором выходом накапливаквдего сумматора, а первый и второй выходы соединены с входом триггера переполнения порядка и входом триггера исчезновения порядка соответственно, третья группа выходов накапливающего регистра соединена с первой группой входов второго Дешифратора, вторая группа входов которого соединена с четвертой группой выходов накапливающего сумматора, а выход соединен с входом Триггера переполнения при делении, пятый выход накапливающего сумматора соединен с четвертым входом регистра множителя остатка, первый выход которого соединен с третьим входом накапливающего сумматора. отличаглщееся тем, что, с целью, сокраидения времени нормализации, оно содержит преобразователь прямого кода числа в дополнительный код, группу элементов И, шифратор и коммутатор, третьяс группа выходов буферного регистра памяти соединена с первой группой входов коммутатора, выходы которого соединены с четвертой группой входов накапливающего сумматора четвертая группа выходов которого соединена с первой группой входов Преобразователя прямогокода числа в дополнительный код и с первой группой входов группы элементов И, вторая группа выходов, регистра 2 шожнтеля-остатка соединена со второ группой входов группы элементов И и с второй группой входов преобразователя прямого кода числа в дополнительный код, группа выходов которог соединена с третьей группой входов группы элементов И, выход которой сединен b входом дешифратора, выход, которого г соединен с вторым вхолом коммутатора.

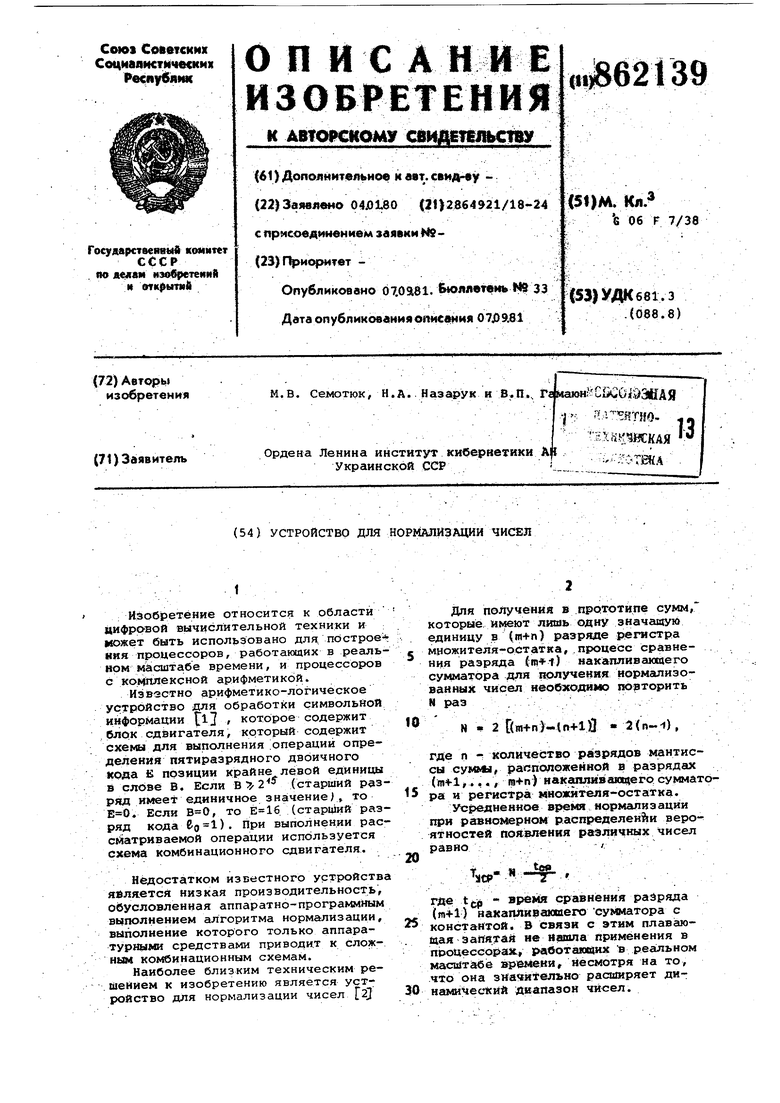

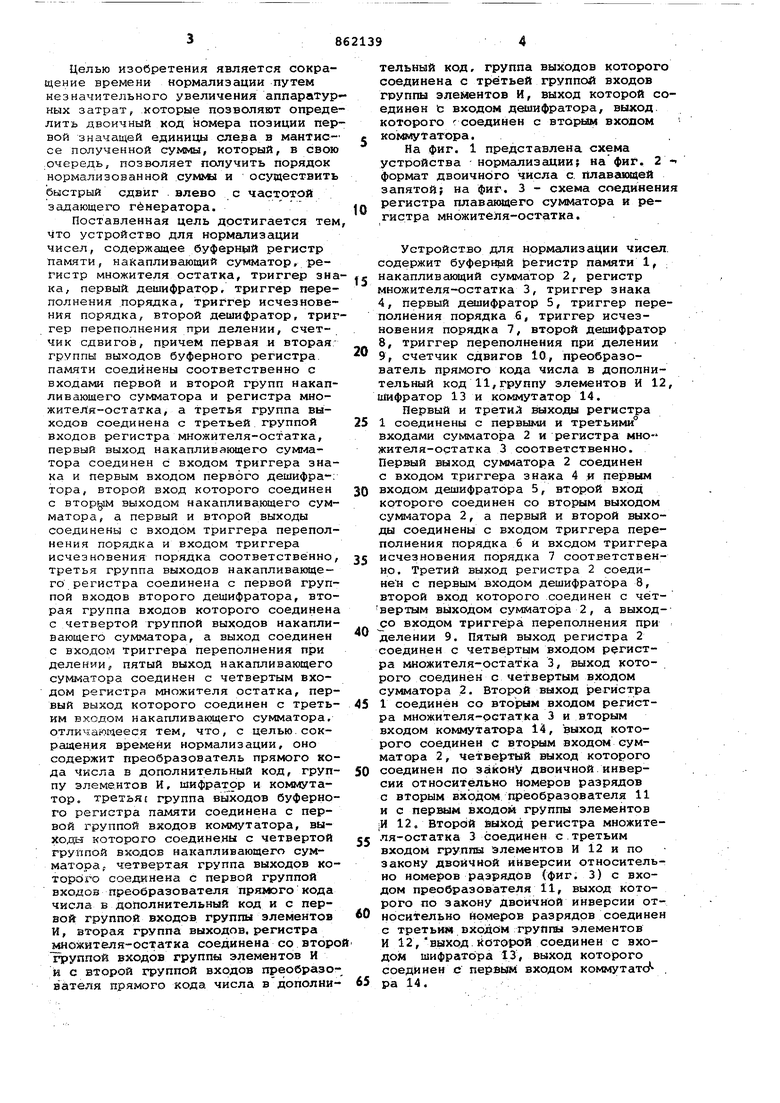

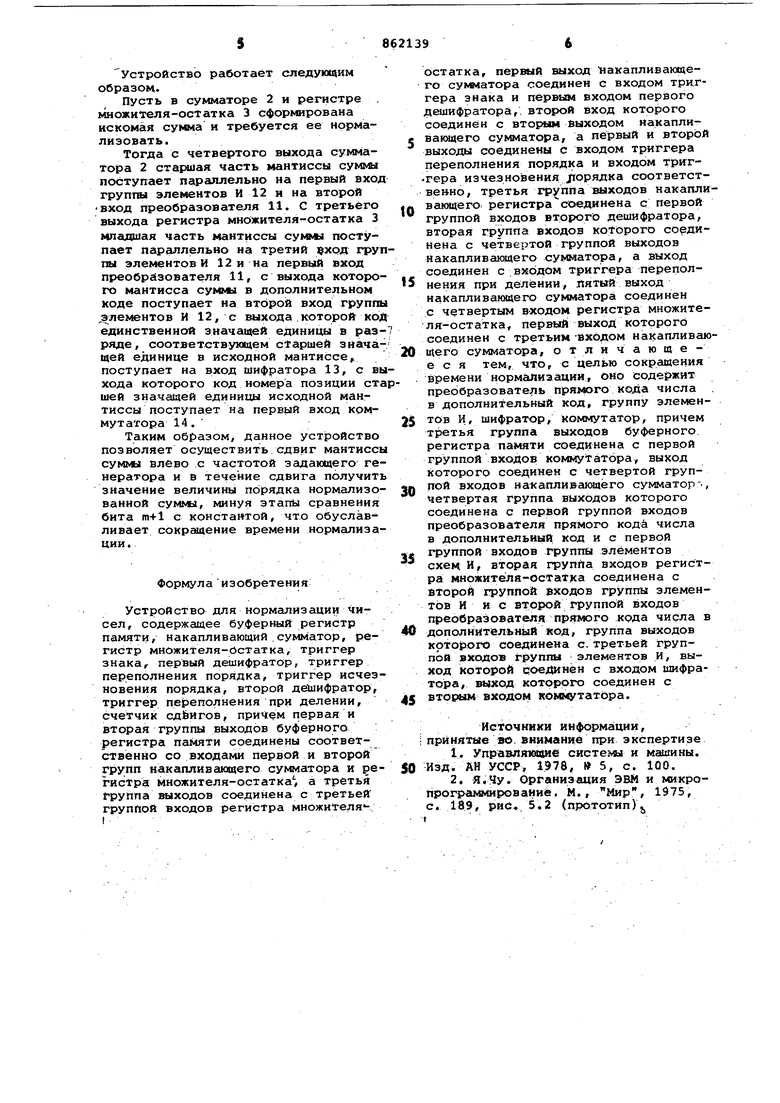

На фиг. 1 представлена схема устройства нормализации} на фиг. 2 формат двоичного числа с. йлавакяаей запятой; на фиг. 3 - схема соединен регистра плавающего сумматора и регистра множителя-осгатка.

Устройство для нормализации чисел содержит буферный регистр памяти 1, накапливаклций сумматор 2, регистр множителя-остатка 3, триггер знака 4, первый дешифратор 5, триггер переполнения порядка 6, триггер исчезновения порядка 7, второй дешифратор

8,триггер переполнения при делении

9,счетчик сдвигов 10, преобразователь прямого кода числа в дополнительный код 11,группу элементов И 12 шифратор 13 и коммутатор 14.

Первый и третий выходы регистра 1 соединены с первыми и третьими входами сумматора 2 и регистра множителя-остатка 3 соответственно. Первый выход сумматора 2 соединен с входом триггера знака 4 .и первым входом дешифратора 5, второй вход которого соединен со вторым выходом сумматора 2, а первый и второй выходы соединены с входом триггера переполнения порядка б и входом триггера исчезновения порядка 7 соответственно. Третий выход регистра 2 соединен с первым входом дешифратора 8, второй вход которого соединен с чётвертым выходом сумматора 2, а выход о входом триггера переполнения при делении 9. Пятый выход регистра 2 соединен с четвертым входом регистра множителя-остатка 3, выход которого соединен с четвертым входом суьшатора 2. Второй выход регистра 1 соединён со вторым входом регистра множителя-остатка 3 и вторым входом коммутатора 14, выход которого соединен с вторым входом сумматора 2, четвертый выход которого соединен по закону двоичной.инверсии относительно номеров разрядов с вторым входом преобразователя 11 и с первым входом группы элементов |И 12. Второй выход регистра множителя-остатка 3 соединен с третьим входом группы элементов И 12 и по закону двоичной инверсии относительно номеров разрядов (фиг. 3) с входом преобразователя 11, выход которого по закону двоичной инверсии относительно йомеров разрядов соединен с третьим входом группы элементов И 12,выход которой соединен с входом шифратора 13, выход которого соединен с первым входом кoммyтaтc ра 14. : Устройство работает следующим образом. Пусть в сумматоре 2 и регистре . кшожителя-остатка 3 сформирована искомая сумма и требуется ее нормализовать. Тогда с четвертого выхода сумматора 2 старшая часть мантиссы поступает параллельно на первый вход групты элементов И 12 и на второй вход преобразователя 11. С третьего выхода регистра множителя-остатка 3 младшая часть мантиссы cyi«« i поступает параллельно на третий ход гру твл элементов И 12 и на первый вход преобр 1зователя 11, с выхода которо го мантисса суммы в дополнительном коде поступает на второй вход группы длементов И 12, с выхода кЬд единственной значащей единицы в разряде, соответствумцем старшей значащей единице в исходной мантиссе, поступает на вход шифратора 13, с вы хода которого код номера позиции ста шей значащей единицы исходной мантиссы поступает на первый вхрд коммутатора 14. Таким образом, данное устройство позволяет осуществить сдвиг мантиссы сумлл влево с частотой задающего генератора и в течение сдвига получить значение величины порядка нормализованной сум(1, минуя этапы сравнения бита т+1 с конста«той, что обуславливает сокроодение времени нормализации. Формулаизобретения: Устройство для нормализации чисел, содержащее буферный регистр памяти, накапливающий сумматор, регистр множителя-Остатка, триггер знака, первый дешифратор, триггер переполнения порядка, триггер исчезновения порядка, второй дешифратор, триггер переполнения при делении, счетчик сдбигов, причем первая и вторая группы выходов буферного регистра памяти соединены соответственно со входами первой и второй групп накапливающего сумматора и регистру множителя-остатка; а третья группа выходов соединена с третьей группой входов регистра множителя ь. остатка, первый выход Иакапливающего cyNwaTopa соединен с входом триггера знака и первым входом первого дешифратора,, второй вход которого соединён с вторым выходом накапливакядего cyNwaTopa, а первый и второй выходы соединены с входом триггера переполнения порядка и входом тркг-гера изчезно1вения тторядка соответственно, третья группа выходов накапливающего регистра соединена с первой группой входов второго дешифратора, вторая группа входов которого соединена с четвертой группой выходов накапливающего сумматора, а выход соединен с входом триггера переполнения при делении, пятый выход накапливающего сумматора соединен с четвертым входом регистра множителя-остатка, первый выход которого соединен с третьим-входом накапливающего сумматора, отличающееся тем, что, с целью сокращения времени нормамиэации, оно содержит преобразователь прямого кода числа . в дополнительный код, группу элементов И, шифратор, KON tyTaTop, причем третья группа выходов буферного, регистра памяти соединена с первой группой входов коммутатора, выход которого соединен с четвертой группой входов накапливакяаёго сумматор-., четвертая группа выходов которого соединена с первой группой входов преобразователя прямого кода числа в дополнительный код и с первой группой входов группы элементов схем И, вторая группа входов регистра множителя-остатка соединена с второй группой входов группы злементЬв И и с второй группо й входов преобразователя прямого кодэ числа в дополнительный код, группа выходов которого соединена с. третьей группой входов группы -элементов И, выход которой соединён с входом шифратора, выход которого соединен с вторым входом коммутатора. Источники информации, принятые во. внимание при экспертизе 1.Управляюаи€ систе увз и Мсй;1ины. Изд. АН УССР, 1978, 5, с. 100. 2.Я.Чу. Организация ЭВМ и микропрограммирование, М. , Мир, 1975, с. 189, рис« 5.2 (прототип)j

фуг. J

Авторы

Даты

1981-09-07—Публикация

1980-01-04—Подача