(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ Изобретение относится к запоминаю щим устройствам и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Известно оперативное запоминающее устройство с автономным контролем, содержащее регистр адреса, адресный коммутатор, накопитель, элементы И, регистр числа,Олок управления, блок свертки по заданному модулю, блок сравнения, кодовые шины адреса и чис ла CiJ . Недостатком этого устройства явля ется невысокое быстроде ствие. Наиболее близким техническим решением к изобретению является устройство, содержащее дешифратор строк и буферный регистр, дешифратор столб цов и буферный регистр, выходы кото рых через усилители строк и усилител столбцов подключены к матрице памяти устройство синхронизации и управления, два выхода которого подключены к дешифратору строк и буферному регистру и дешифратору столбцов и буферному регистру, два других выхода - к усилителям столбцов, устройство ввода-вывода подключено к устройству синхронизации и управления. дешифратору столбцов и буферному регистру Г2 , Недостатком такого устройства является низкое быстродействие, обусловленное сложностью средств контроля при производстве и испытаниях устройства, вьтолненного в виде интегральной схема. Цель изобретения - повышение быстродействия устройства за счет введения средств автономного контроля в интегральную схему. Поставленная цель достигается тем, что в оперативное запоминающее устройство с автономным контролем,содержащее накопитель, дешифраторы,усилители, блок управления и блок ввода-вывода информации, причём выходы перрого дешифратора подключены соответственно ко входам первого усилителя, выходы которого соединены соответственно с одними из входов накопителя, другие, входы которого подключены к выходам второго усилителя, один из выходов блока ввода-вывода информации является первым выходом устройства, а другие выходы соединены с одними из входов второго дешифратора, выходы KOTOpoip подключены ко входам второго усилителя, выходы .

блока управления соединены соответ-; ственно с управляющими входами дешифраторов и усилителей, введены счетчик, генератор импульсов, формирователи импульсов, элементы ИЛИ и блок анализа, причем вход генератора импульсов является первым входом устройства и соединен с первыми входами счетчика, первого формирователя импульсов и блока анализа, выход генератора импульсов подключен к первому входу второго формирователя импульсов и второму входу счетчика, один из выходов которого соединен со вторым входом первого формирователя импульсов , а другие выходы подключены соответственно ко входам первого дешифратора , другим входом второго дешифратора и третьему входу первого формирователя импульсов, первый выход которого соединен со вторым входом второго формирователя импульсов, а второй выход - со вторым входом блока анализа, третий вход которого подключен к первому выходу устройства, первый выход второго формирователя импульсов соединен с четвертым входом блока анализа, второй выход с пятым входом блока анализа и первым входом первого элемента ИЛИ, а третий выход - с первым входом второго элемента ИЛИ, первый вход третьего элемента ИЛИ подключен к третьему выходу первого формирователя импульсов, выходы элементов ИЛИ соединены соответственно со входами блока ввода-вывода информации, вторые входы элементов ИЛИ и выход блока анализа являются соответственно в торым, третьим и четвертым входами и вторым выходом .устройства.

Кроме того, введены схема сравнения, элемент И и триггеры, причем выход схемы сравнения подключен к первому входу элемента И, выход которого соединен с первым входом первого триггера, выход которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно с первым входом и с выходом блока анализа, входы схемы сравнения подключены соответственно ко второму и к третьему входам блока анализа, а вторые входы элемента И и первого триггера - соответственно к четвертому и пятому входам блока анализа.

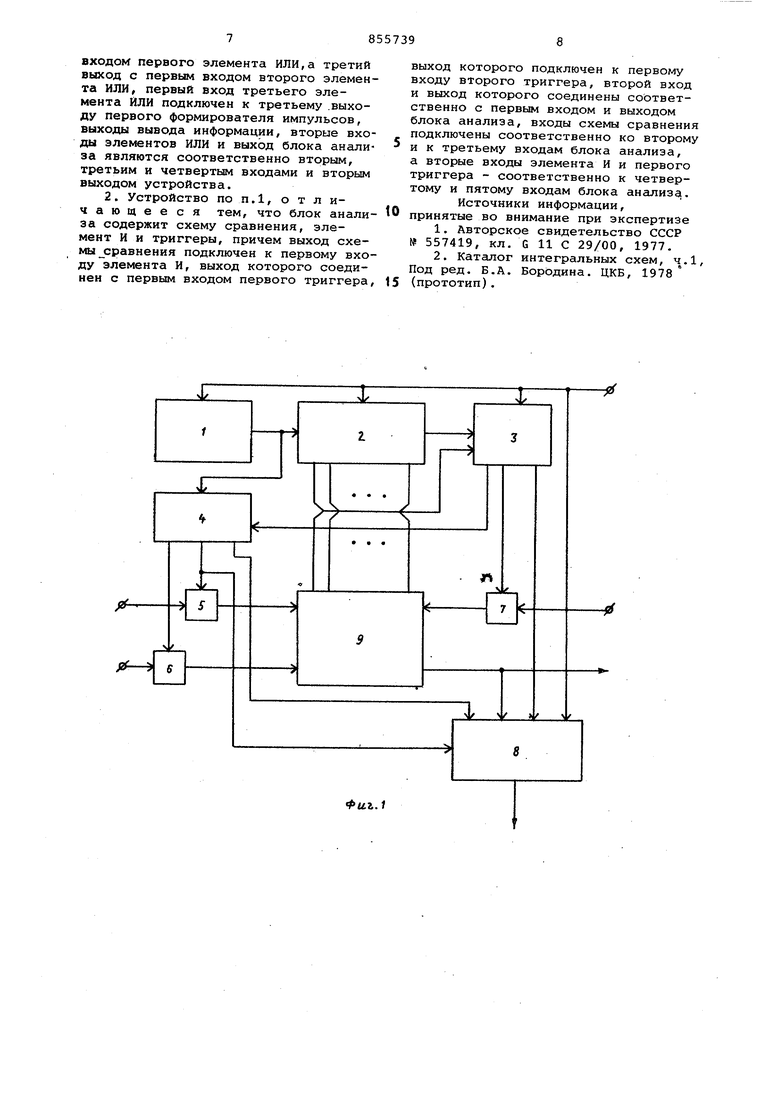

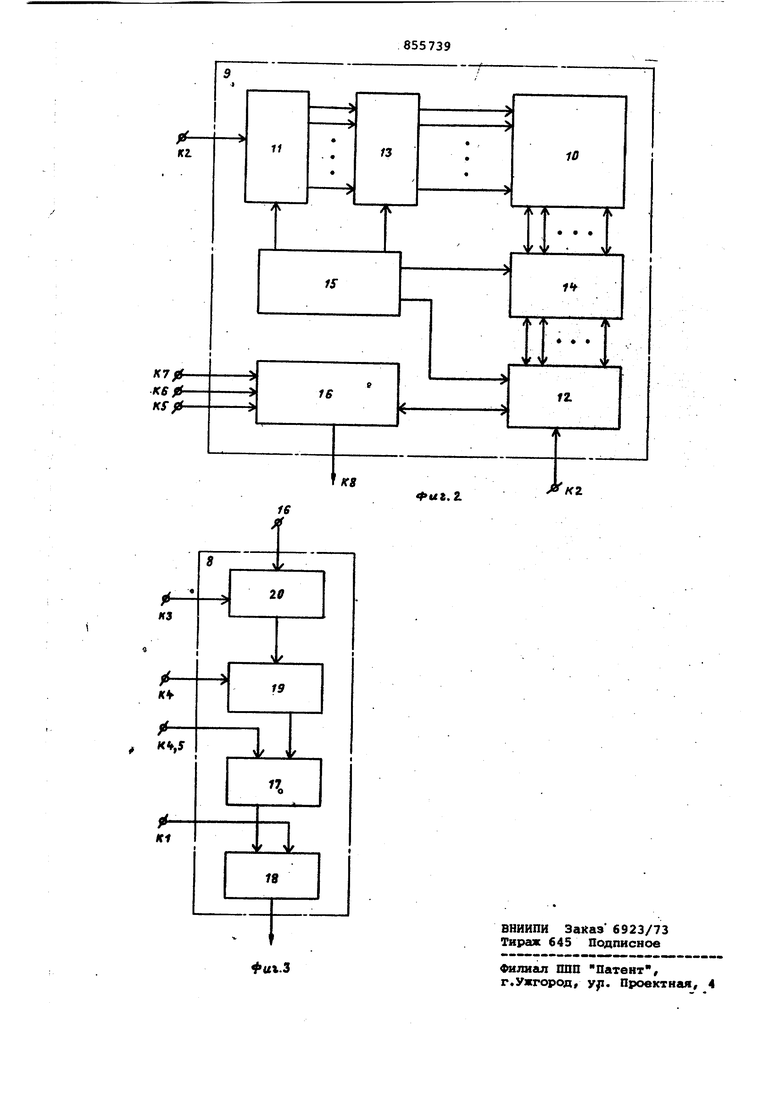

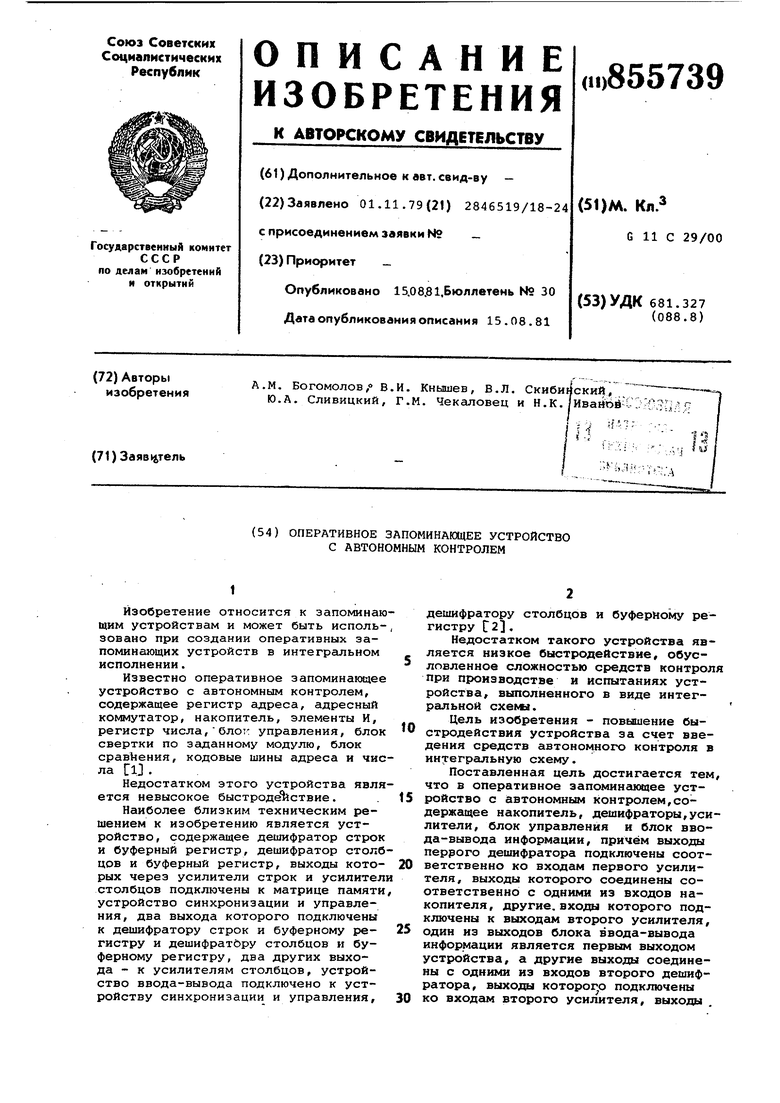

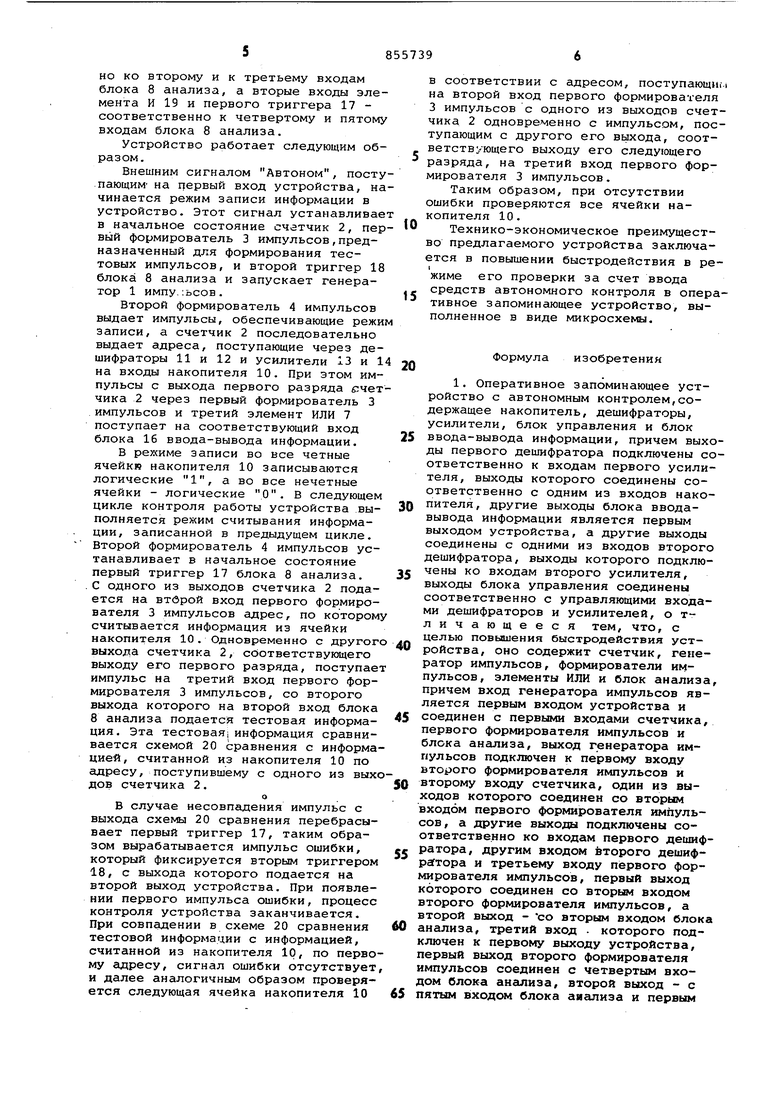

Нафиг.1 и 2 приведена функциональная схема предлагаемого устройства; на фи|г. 3 - функциональная схема , блока анализа.

Устройство содержит генератор 1 импульсов,счетчик 2, первый 3 и второй 4 формирователи импульсов, первый 5, второй б и третий 7 элементы ИЛИ, блок 8 анализа и блок 9 оперативной памяти, состоящий из накопителя 10, первого 11 и второго 12 дешифратора, первого 13 и второго 14

усилителей, блока 15 управления и блока 16 ввода-вывода информации.

Выходы первого дешифратора 11 подключены соответственно ко входам первого усилителя 13, выходы которого соединены соответственно с одними из входов накопителя 10. Другие входы накопителя 10 подключены к выходам второго усилителя 14. Один из выходов блока 16 ввода-вывода информации является первым входом устройства, а

другие выходы соединены с одними из входов второго дешифратора 12, выходы которого подключены ко входам второго усилителя 14. Выходы блока 15« управления соединены соответственно

5 с управляющими входами дешифраторов 11 и 12 и усилителей 13 и 14.

Вход генератора 1 импульсов является первыг/ входом устройства и соединен с первыми входами счетчика 2,

0 первого формирователя 3 импульсов и блока 8 анализа. Выход генератора 1 импульсов подключен к первому входу второго формирователя 4 импульсов и второму входу счетчика 2, один из выходов которого соединен со вторым входом первого формирователя 3 импульсов, а другие выходы подключены соответственно ко входам первого дешифратора 11, другим входом второго деQ шифратора 12 и третьему входу первого формирователя 3 импульсов. Первый выход первого формирователя 3 импульсов соединен со вторым входом второго формирователя 4 импульсов, а второй

с выход - со вторым входом блока 8 анализа, третий вход которого подключен к первому выходу устройства. Первый выход второго формирователя 4 импульсов соединен с четвертыгл входом блока 8 анршиза, второй выход - с пятым

0 входом блока 8 анализа и первым входом, первого элемента ИЛИ 5, а третий выход - с первым входом второго эле- . мента ИЛИ 6. Первый вход третьего элемента ИЛИ 7 подключен к третьему

5 выходу первого формирователя 3 импульсов. Выходы элементов ИЛИ 5,6 и 7 соединены соответственно со входами блока 16 ввода-вывода информации. Вторые входы элементов ИЛИ 5,6

Q и 7 и выход блока 8 анализа являются соответственно вторым, третьим и четвертым входами и вторым выходом устройства. При этом блок 8 анализа выполнен содержащим первый 17 и

„ второй 18 триггеры, элемент И 19 и схему 20 сравнения.

Выход схемы 20 сравнения подключен к первому входу элемента И 19, выход которого соединен с первым входом первого триггера 17. Выход

0 первого триггера 17 подключен к первому входу второго триггера 18,второй вход и выход которого соединены соответственно с первым входом и с выходом блока 8 анализа. Входы схемы

5 20 сравнения подключены соответственно ко второму и к третьему входам блока 8 анализа, а вторые входы элемента И 19 и первого триггера 17 соответственно к четвертому и пятому входам блока 8 анализа. Устройство работает следующим образом. Внешним сигналом Автоном, посту пающим на цервый вход устройства, на чинается режим записи информации в устройство. Этот сигнал устанавливае в начальное состояние счетчик 2, пер вый формирователь 3 импульсов,предназначенный для формирования тестовых импульсов, и второй триггер 18 блока 8 анализа и запускает генератор 1 импу. :ьсов. Второй формирователь 4 импульсов выдает импульсы, обеспечивающие режи записи, а счетчик 2 последовательно выдает адреса, поступающие через дешифраторы 1.1. и 12 и усилители 13 и 1 на входы накопителя 10. При этом импульсы с вЕлхода первого разряда й:чет чика 2 через первый формирователь 3 импульсов и третий элемент ИЛИ 7 поступает на соответствующий вход блока 16 ввода-вывода информации. В режиме записи во все четные ячейки накопителя 10 записываются а во все нечетные логические ячейки - логические О. В следующем цикле контроля работы устройства выполняется режим считывания информации, записанной в предыдущем цикле. Второй формирователь 4 импульсов устанавливает в начальное состояние первый триггер 17 блока 8 анализа. .С одного из выходов счетчика 2 подается на втСрой вход первого формирователя 3 импульсов адрес, по котором считывается информация из ячейки накопителя 10. Одновременно с другог выхода счетчика 2, соответствующего выходу его первого разряда, поступае импульс на третий вход первого формирователя 3 импульсов, со второго выхода которого на второй вход блока 8 анализа подается тестовая информа ция. Эта тестовая; информация сравнивается схемой 20 сравнения с информа цией, считанной из накопителя 10 по адресу, поступившему с одного из вых дов счетчика 2. в случае несовпадения импульс с выхода схемы 20 сравнения перебрасывает первый триггер 17, таким образом вырабатывается импульс ошибки, который фиксируется вторым триггером 18, с выхода которого подается на второй выход устройства. При появлении первого импульса ошибки, процесс контроля устройства заканчивается. При совпадении в схеме 20 сравнения тестовой информации с информацией, считанной из накопителя 10, по перво му адресу, сигнал ошибки отсутствует и далее аналогичным образом проверяется следующая ячейка накопителя 10 ,в соответствии с адресом, поступающие на второй вход первого формирователя 3 импульсов с одного из выходов счетчика 2 одновременно с импульсом, поступающим с другого его выхода, соответствующего выходу его следующего разряда, на третий вход первого формирователя 3 импульсов. Таким образом, при отсутствии ошибки проверяются все ячейки накопителя 10. Технико-экономическое преимущество предлагаемого устройства заключается в повышении быстродействия в реIжиме его проверки за счет ввода средств автономного контроля в оперативное запоминающее устройство, выполненное в виде микросхемы. Формула изобретения 1. Оперативное запоминающее устройство с автономным контролем,содержащее накопитель, дешифраторы, усилители, блок управления и блок ввода-вывода информации, причем выходы первого дешифратора подключены соответственно к входам первого усилителя, выходы которого соединены соответственно с одним из входов накопителя , другие выходы блока вводавывода информации является первым выходом устройства, а другие выходы соединены с одними из входов второго дешифратора, выходы которого подключены ко входам второго усилителя, выходы блока управления соединены соответственно с управляющими входами дешифраторов и усилителей, о тличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик, генератор импульсов, формирователи импульсов, элементы ИЛИ и блок анализа, причем вход генератора импульсов является первым входом устройства и соединен с первыми входами счетчика, первого формирователя импульсов и блока анализа, выход генератора импульсов подключен к первому входу второго формирователя импульсов и второму входу счетчика, один из выходов которого соединен со вторым входом первого формирователя импульсов, а другие выходы подключены соответственно ко входам первого дешифратора, другим входом второго дешифpafTOpa и третьему входу первого формирователя импульсов, первый выход которого соединен со вторым входом второго формирователя импульсов, а второй выход - со вторым входом блока анализа, третий вход которого подключен к первому выходу устройства, первый выход второго формирователя импульсов соединен с четвертым входом блока анализа, второй выход - с пятым входом блока анализа и первым

ВХОДОМ первого элемента ИЛИ,а третий выход с первым входом второго элемента ИЛИ, первый вход третьего элемента Или подключен к третьему .выходу первого формирователя импульсов, выходы вывода информации, вторые входы элементов ИЛИ и выход блока анализа являются соответственно вторым, третьим и четвертым входами и вторым выходом устройства.

2. Устройство по П.1, о т л ичающее ся тем, что блок анализа содержит схему сравнения, элемент И и триггеры, причем выход схемы сравнения подключен к первому входу элемента И, выход которого соединен с первым входом первого триггера.

выход которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно с первым входом и выходом блока анализа, входы схемы сравнения подключены соответственно ко второму и к третьему входам блока анализа, а вторые входы элемента И и первого триггера - соответственно к четвертому и пятому входам блока анализа.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 557419, кл. G 11 С 29/00, 1977.

2.Каталог интегральных схем, ч.1. Под ред. Б.А. Бородина. ЦКБ, 1978

5 (прототип).

11

Ki

ID

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое постоянное запоминающее устройство с контролем | 1979 |

|

SU951398A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ТОРМОЗНОГО ПРОЦЕССА ТРАНСПОРТНОГО СРЕДСТВА | 1993 |

|

RU2038237C1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

ff

-

16

1

M кг

Фиъ,г

Авторы

Даты

1981-08-15—Публикация

1979-11-01—Подача