(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯ&КЕНИЯ В ИНТЕГРАЛ ВРЕМЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1984 |

|

SU1314457A1 |

| Интегрирующий аналого-цифровой преобразователь | 1982 |

|

SU1202056A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Устройство для измерения неэлектрических величин | 1981 |

|

SU1055958A1 |

| Делительное устройство | 1979 |

|

SU805342A1 |

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

Изобретение относится к электроизмерительной технике, в частности к анапого о Щ фрОБЫм преобразователям двухтактного интегрирования и может быть Использовано в цифровых вольтметрах, измерительных системах. Известен аналого-цифровой преобразов тель с однополярным источником опорно. го разрядного напряжения и выпрямителем напряжения в канале прохонсдения из- меряемого напряжении Uy Cll Недостаток этого преобразователя - н личие погрешности преобразования при превышении сигналом помех величины преобразуемого напряжения. Цель изобретения - уменьшение погрешности преобразования напряжения. Поставленная цеяь достигается тем, что в преобразователь напряжения в интервал времени, содержащий входной усилитель, вход которого соединен с шиной входного сигнала, а выход соединен через первый ключ со входом интегратора, вход которого через второй ключ подключен к выходу первого опорного, источника, а выход соединен со входом компаратора, при этом шина запуск соединена с первыми входами триггеров такта и иикла, а выход триггера цикла чераз формирователь длительности первого такта подключен ко второму ЗХОДУ триггера цикла, выход которого соединен с управляющим входом первого ключа, введены инвертор, элемент 2И-НЕ, первый и второй триггеры полярности, второй опорный источник и третий ключ, причем вход инвертора со единен с выходом компаратора и с единичным входом первого триггера полярности, а выход соединен с единичным входом второго триггера пол1фности, первый нулевой вход которого соединен с выходом триггера такта и первым нулевым входом первого триггера полярности, а нулевой вход соединен со вторым выходом триггера 1шкла и вторым нулевт.м входом первого триггера полярности, прямой выход соединенс управляющим входом третьего ключа, а инверсный выход соединен с первым входом элемента , второй вход которого соединен с инверсным выходом первого триггера полярности а выход под|шючен ко второму входу триггера цикпа, при этом прямой выход первого триггера поля эности соединен с управляющим входом второго ключа, а второй опорный источник через третий кпюч подключен ко. входу интегратора.

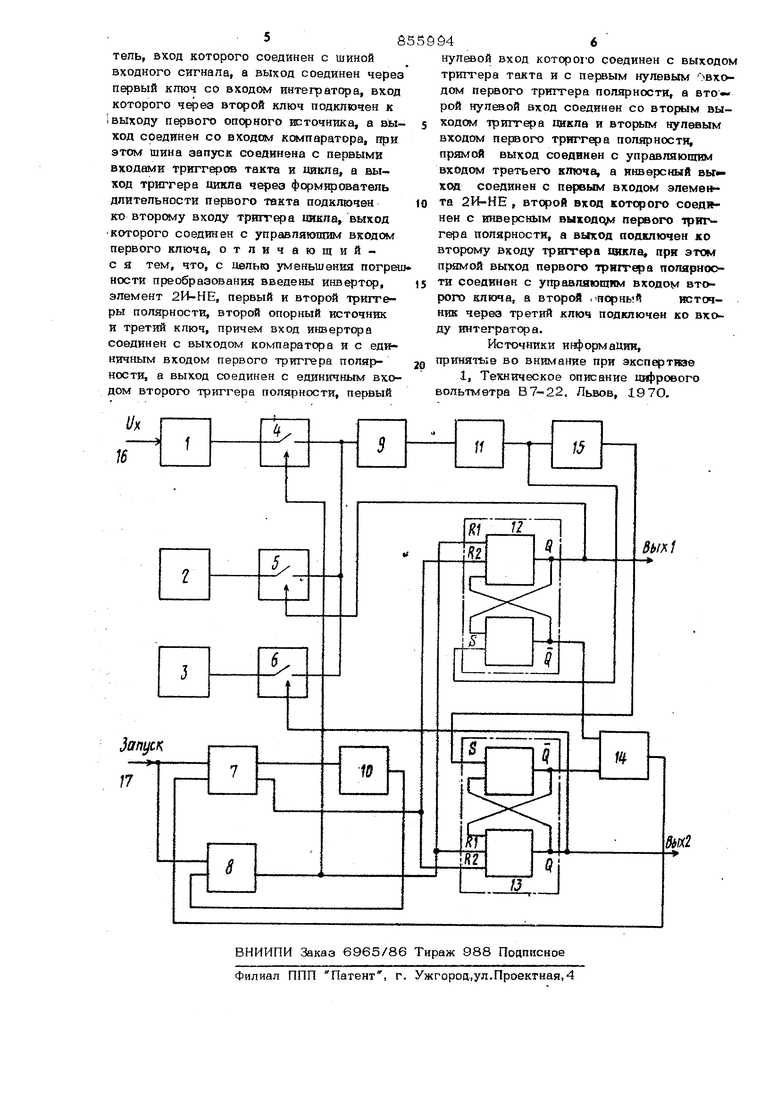

На чертеже представлена структурная схема преобрааоватепя напряжения в интервал времени. Преофаэоватепь содержит входной усилитель 1„ опорные источники 2 и 3, ключи 4-6, триггер 7 цикпа, триггер 8 такта, интегратор 9, фсрмщзоватепь Ю длительности первого такта, компаратор И, первый и второй триггер 12 и 13 полярности, элемент 2И-НЕ 14, инвертор 15, шину 16 входного сигнала, шину 17 запуска, Устройствоработает следую: 1гам

образом.

В исходном состоянии ключи 4-6 разомкнуты, интегратор 9 разряжен. Ключи 4-6 замыкаются, когда потенциал на .управпяюшем входе соответствует логическому нулю, и размыкаются при логической единице. С приходом . запускающго ю пульса триггеры 7 и 8 изменяют состояние, при этом ключ 4 замыкается, начинается заряд интегратора 9. Потенциалы на первых выходах триггеров 12 и 13 не изменяются. Компаратор 11 устанавливается в состояние, определяемое полярностью преобразуемого напря жения и,( , величиной напряжения, помех состоянием интегратора.

Во время первого такта интегрирования при любом состоянии инвертера и интегратора на одном входе элемента 2И- НЕ 14 присутствует потенциал:, соответствующий логической единице, а на другом входе - логическому нулю. Поэтому независимо от полярности преобразуемого напряжения U на выходе элемента 254-НЕ 14 присутствует потенциал, соответствующий логической единице. Длительность первого такта интегр$фования Т определяется формтфойатепем 1О длитепьнсжти пе{юаго такта, который через интервал длительностью Т с момента запуска, возвращает триггер такта в исходное состояние. Напряжение на выходе интегратора к концу первого такта интвгрир,свания будет равио :

0 :K5rUx U,SinCu;t4y5flt,

О гдеНпоЦ- напряжение помехи.

Интегрирование производится с учетом полярности преобразуемого сигнала, и интеграл от суммы равен сумме интегралов. В случае, еспи время интегрирования Т кратно периоду помехи, то

Р

(a;t4(, а L/H-K UxdH kT;ux

После возвращения в исходное состояние

триггера 8 такта, ключ 4 размыкается, и начинается второй такт интегрирования, когда производится разряд интегратора. Во время второго такта на всех входах сброса триггеров 12 и 13 присутствуют потенциалы, соответствующие логической единице, дальнейшее состояние триггеров определяется только потенциалами на входах установки. При положи-тельной полярности выходного напряжения интегратора, триггер 12 замыкает- ся, кпюч 5 замыкается, и начинается разряд интегратора от опорного источника 2. Как только ; 5пряж:ение на выходе интегратора достигает исходной величины,компаратор 11, а за ним я инвертор изменяют состояния.

При этом триггер 13 полярности изменяет состояние, а триггер 12 полярности остается в прежнем состоянии. После этого потенциалы на входах элемеь

та 2И-НЕ 14 соответствуют логической единице, а на выходе - ее нулю. Элемент 14 возвращает триггер 7 цикла по второму входу в исходное состояние. Триггер 7 цикла, опрокидьюаясь, возвра5 щает триггеры 12 и 13 полярности по вторым нулевым вxoдa в исходное сос«« тояние. Ключ 6 размыкается. Длительность интервала времени между опрокидыванием триггера 12 и аозвращением в

o исходное состояние определяется задержками прохождения информации и может быть сделана скопь угодно малой. Длительность второго такта интегрирования

Тп

равна :

-г Х Тл

оп

Выходная информация снимается с выхода триггер 12 и 13.

Таким образом, устройство исключает погрешность измерения при превышении напряжением помех величины постоянного преобразуемого напряжения Ux .

55 Формула изобретения

Преобразователь напряжения в интервал времени, содержащий входной усили

Авторы

Даты

1981-08-15—Публикация

1979-01-04—Подача