(54) УСТРОЙСТВО КОНТРОЛЯ ХАРАКТЕРИСТИК ЦИФРОВЫХ КАНАЛОВ СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство цикловой синхронизации | 1987 |

|

SU1515382A2 |

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| Устройство для декодирования циклических кодов | 1985 |

|

SU1241480A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1982 |

|

SU1113892A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство для кодирования и декодирования циклических кодов | 1985 |

|

SU1302440A1 |

1

Изобретение относится к электросвязи и может использоваться в аппаратуре многоканальных цифровых линий передачи и синхронных цифровых сетей.

Известно устройство контроля характеристик цифровых каналов связи, содержащее генератор эталонной последовательности, блок сравнения, выход которого подключен к информационному входу регистра сдвига, счетчик, выход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, и элемент ИЛИ 1 .

Однако точность контроля данным устройством недостаточна.

Цель изобретения - повышение точности контроля характеристик цифровых каналов связи.

Цель достигается тем, что в устройство контроля характеристик цифровых каналов связи, содержащее генератор этсшонной последовательности, блок сравнения, выход которого подключен к информационному входу регистра сдвига, счетчик, выход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, и элемент ИЛИ, введены два сумматора по модулю два,

три элемента И, два дополнительных счетчика и три элемента ИЛИ, при этом первый выход генератора эталонной последовательности через первый сумматор по модулю два подключен к первому входу первого элемента И, второй выход генератора эталонной последовательности подключен ко входу блока сравнения, к другому входу

10 первого сумматора по модулю два и ко входу второго сумматора по модулю два, другой вход которого соединен с третьим выходом генератора эталонной последовательности, выход

15 второго сумматора по модулю два подключен к первому входу второго элемента И, выход блока сравнения подключен ко вторым входам первого и второго элемента И, к другому входу блока

20 фазирования, к первому входу третьего элемента И, к первому входу элемента ИЛИ и к установочному входу счетчика, выход первого элемента И через первый дополнительный счетчик

25 подключен к первому входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и к третьему входу генератора этгшонной последовательности, выход второго элемента И че30рез второй дополнительный счетчик

1о,1К11ючян КО второму входу второго э.темсита ИЛИ, к первому входу треть« го .элемента КЛИ, вторые входы перво го и третьего элементов ИЛИ соединены с выходом счетчика, со вторым входом третьего элемента И и со вторым входом элемента ИЛИ, выход первого элемента ИЛИ подключен к установочному входу второго дополнительного счетчика, выход третьего элемента ИЛИ подключен к установочному входу первого дополнительного счетчика, выход второго элемента ИЛИ подключен к установочному входу регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ, При этом генератор эталонной последовательности выполнен в виде регистра сдвига, первый и второй выходы которого подключены соответственно к первому к второму входам сумматора по модулю два, выход которого подключен к первому входу регистра сдвига, третий выход регистра сдвигаявляется вторым выходом генератора эталонной последовательности, четвертый выход регистра сдвига является первым выходом генератора эталонной последовательности, второй выход регистра сдвига является третьим выходом генератора эталонной последовательности, все выходы регистра сдвига подключены к соответствующим входам элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого является первым входЬм генератора эталонной последовательности, третий вход элемента И является вторым входом генератора эташонной последовательности, выход элемента И подключен к первому входу дополнительного элемента ИЛИ, второй вход которого является третьим входом генератора эталонной последовательности, выход дополнительного элемента ИЛИ подключен к тактовому входу регистра сдвига.

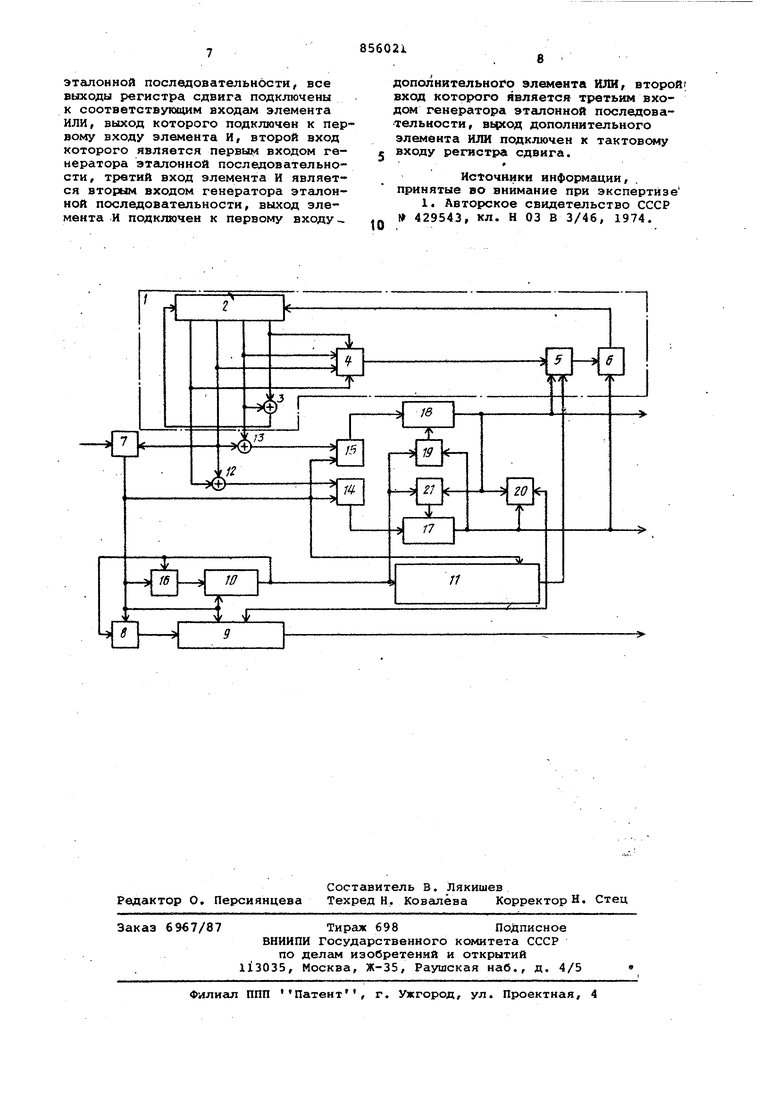

На чертеже приведена структурная электрическая схема предлагаемого устройства контроля характеристик 1ШФРОВЫХ кансшов связи.

Устройство содержит генератор 1 эталонной последовательности, в состав которого входят регистр 2 сдвига, сумматор 3 по модулю два, элемент ИЛИ 4, элемент И 5 и дополнительный элемент ИЛИ 6, блок 7 сравнения, элемент 8 ИЛИ, регистр 9 сдвига, счетЧик 10, блок 11 фазирования первый и второй сумматоры 12 и 13 по модулю два, первый, второй и третий элементы 14 - 16 И, первый и второй дополнительные счетчики 17 и 18, первый, второй и третий дополнительные элементы ИЛИ 19 - 21.

Устройство работает следуюсдим образом.

Блок 7 сравнения осуществляет посимвольное сравнение принимаемого сигнала с этгшонной последовательностью. Счетчик 10 подсчитывает импульсы совпадений, поступающие на ег счетный вход, через третий элемент И 16, а при несовпадении обнуляется импульсом на установочном входе. При отсутствии синхронизма блок 11 фазирования через элемент И 5 и элемент ИЛИ б подает импульсы на тактовый вход регистра 2 сдвига генератора 1 эталонной последовательности. Таким образом при несовпадении символов регистр 2 сдвига остается в прежнем состоянии. За счет таких остановок эталонный сигнал подстраивается под принимаемую последовательность. После окончания подстройки при отсутствии сбоев выходные импульсы счетчика 10 выключают блок 11 фазирований и редкие сбои принимаемого сигнала не влияют на работу генератора 1 эталонной последовательности.

Импульсы, соответствующие сбоям, поступают на информационный вход регистра 9 сдвига и вписываются тактовыми импульсами с элемента 8 ИЛИ. При отсутствии фаэового сдвига эти сбои сравнительно редки, поэтому счетчик 10 быстро вновь фиксирует наличие синхронизма и блокируется во включенном состоянии третьим элементом 16 И. При этом с выхода счетчика 10 через элемент 8 ИЛИ на тактовый вход регистра 9 сдвига поступают импульсы, продвигающие на выход регистра 9 сдвига сигналы, соответствующие сбоям.

Сигналы о. появлении дискретного сдвига выделяются первым и вторым элементами 14 и 15 И, на вторые входы которых поступают сигналы ошибки с блока 7 сравнения. При этом первый и второй сумматоры 12 и 13, сравнивающие эталонный сигнал на выходе регистра 2 сдвига генератора 1 эталоной последовательности с сигналами, сдвинутыми на величину ожидаемого фазового сдщнта в сторону опережения и отставания,, выдают импульсы исключакмдие иЭ рассмотрения тактовые позиции, на которых посылки этих сигналов совпадают. Действительно, искажение посылок принимаемого сигнала на этих позициях не может быть свидетельством ни наличия, ни отсутствия фазового сдвига, так как в обоих случаях фиксируется сбой входного сигнала. На остальных тактовых позициях элементы И 14 и 15 открыты и при наличии сигнала ошибки на выходе блока 7 сравнения пропускают импульсы на счетный вход дополнительных счетчиков 17 и 18. При отсутствии фазового сдвига дополнительные счетчики обнуляются импульсами с выхода счетчика 10. При появлении дискретного фазового сдвига ожидаемой величины на счетных Bxc5i«5ax обоих дополнительных счетчиков 17 и. 18 появляются импульсы, однако частота их на входе счетчика, фиксирующе го сдвиг в соответствующую сторону оказывается значительно выше. Поэтому при фазовс сдвиге в сторону опережения срабатывает дополнительный счетчик 18, который, запирая элемент И 5, эаприцает соответствую щее ожидаемому фазовому сдвигу числ импульсов на входе регистра 2 сдви га, корректиру Г фазу эталонн9й последовательности. При фазовом сдвиг в сторону отставания ангшогичная ко рекция производится дополнительным счетчиком 17, путем добавления соот ветствующего чис1аа тактовых импульсов на элементе ИЛИ 6. Сбои импульсов принятого сигнеипа не обнуляют дополнительные счетчики 17 и 18, а ускоряют принятие решения о фазовой коррекции. Соответствующие наличию фазового сдвига импульсы в зависимости от направления -сдвига поступа ют на вход одного из внешних индикаторов. Одновременно эти импульсы через первый и третий дополнительны элементы ИЛИ 19 и 21 обнуляют допол нительный счетчик, а через второй дополнительный элемент ИЛИ 20-ре гистр 9 сдвига. Поскольку емкость дополнительных счетчиков 17 и 18 вы бирается равной емкости регистра 9 сдвига, из сбоев, зафиксированных блоком сравнения, исключается лишь то число импульсов, которое потребо Вёшось ДЛЯ определения наличия дискретного фазового сдвига, остальные сбои, в том числе и отмеченные во время фазового сдвига при запертых элементах И 14 и 15 с выхода регистра 9 сдвига поступают на вход вн« него индикатора сбоев. Таким образом, предлагаемое устр ство корректирует лишь фазовые сдви ги, возникающие при правильной рабо оборудования канала связи,-определяет направление сдвига и отмечает наличие искажений, посылок принимаемого трст-сигнала даже во время фиксации фазового сдвига. Это улучшает качество контроля исправности аппаратуры, обеспечивает своевремен ный ремонт -ее или переключение на р зерв и за счет этого повышает достоверность передачи информации по цифровому каналу связи. Формула изобретения 1. Устройство контроля характеристик цифровых каналов связи, соде жащее генератор эталонной последовательности, блок сравнения, выход которого подключен к информационном входу регистра сдвига, счетчик, выход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, и элемент ИЛИ, отличающеес я тем, что, с целью повышения точности контроля, введены два сумматора по модулю два, три элемента И, два дополнительных счетчика и три элемента ИЛИ, при этом первый выход генератора эталонной последовательности через первый сумматор по модулю два подключен к первому входу первого элемента И, второй выход генератора эталонной последовательности подключен входу блока сравнения, к другому входу первого сумматора по модулю два и ко входу второго сумматора по модулю два, другой вход которого соединен с третьим выходом генератора эталонной последовательности, выход второго сумматора по модулю два подключен к первому входу второго элемента И, выход блока сравнения подключен ко вторым входам первого и второго элементов И, к другому входу блока фазирования, к первому входу третьего элемента И, к первому входу элемента ИЛИ и к установочному входу счётчика, выход первого элемента И через первый дополнительный счетчик подключен к первому входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и к третьему входу генератора эталонной последовательности, выход второго элемента И через второй дополнительный счетчик подключен ко второму входу второго элемента ИЛИ, к первому входу третьего элемента ИЛИ, вторые входы первого и третьего элементов ИЛИ соединены с выходом счетчика, со вторым входом третьего элемента И и со вторым входом элемента ИЛИ, выход первого элемента ИЛИ подключён к установочному входу второго дополнительного счетчика, выход третьего элемента ИЛИ подключен к установочному входу первого дополнительного счетчика, выход второго элемента ИЛИ подключен к установочному входу регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ. 2. Устройство по п. .1, о т л ичающеес я тем, что генератор эталонной последовательности выполнен в виде регистра сдвига, первый и второй выходы которого подключены соответственно к первому и второму входам сумматора по модулю два, выход которого подключен к первому входу регистра сдвига, третий выход регистра сдвига является вторым выходом генератора эталонной последовательности, четвертый выход регистра сдвига является первым выходом генератора эталонной последовательности, второй выход регистра сдвига является третьим выходом генератора

эталонной последовательности, все выходы регистра сдвига подключены к соответствующим входам элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого является первым входом генератора эталонной последовательности, третий вход элемента И является вторым входом генератора эталонной последовательности, выход элемента И подключен к первому входу

дополнительного элемента ИЛИ, второй вход которого является третьим входом генератора этгшонной последоваТельности, вцход дополнительного элемента ИЛИ подключен к тактовому входу регистра сдвига.

#

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-08-15—Публикация

1978-12-22—Подача