1

Изобретение относится к вычислительной технике и автоматике.

Известен шифратор, содержащий диоды, резисторы, шины нулевого и единичного потенциала, коммутационные элементы lIОднако ввиду наличия коммутационных элементов шифратор имеет низкую эксплуатационную надежность.

Наиболее близким к предлагаемому по технической сущности является шифратор, построенный на основе специальных интегральных логических микросхем-шифраторов, содержащий две группы указанных микросхем, играющих роль входных сборок, или две выходньлх микросхемы того же типа, регистр выходного кода 2.

Недостатком известного шифратора являются значительные аппаратурные затраты при кодировании больших массивов инфор мации, т.е. при наличии большого количества входных сигналов.

Цель изобретения - упрощение шифратора.

Поставленная цель достигается тем, что шифратор, содержащий регистр входного кода, содержит мультиплексоры, счетчик и генератор

тактовых импульсов, причем шины входных сигналов подключены.к информационным входам входных мультиплексоров, выход каждого из которых

5 соединен с одним из информационных входов выходного мультиплексора, выход которого соединен с входом записи регистра выходного кода, выход генератора тактовых импульсов соеди 0 нен с входом счетчика, выходы младших разрядов которого подключены к входам управления выходного мультиплексора и к входам соответствующих старших разрядов регистра выходного

15 кода, а-выходы соответствующих старших разрядов подключены к входам управления входных мультиплексоров и входам соответствующих младших разрядов регистра выходного кода.

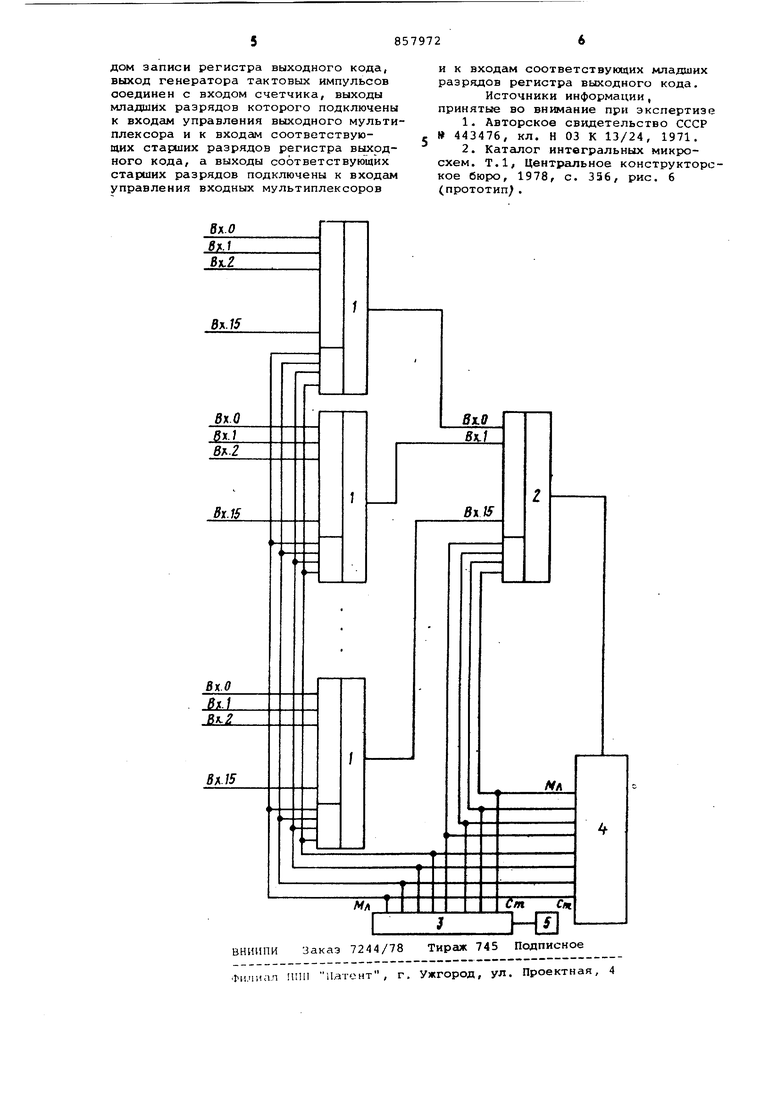

На чертеже изображена схема шифратора, кодирующего 256 входных сигналов (символов, команд, операций).

25 Устройство содержит шестнадцать входных мультиплексоров 1,один выходной мультиплексор 2, восьмиразрядный двоичный счетчик 3, восьмиразрядный регистр 4 выходного кода и генератор 5 тактовых импульсов.

шины двухсот пятидесяти шести кодиpye .ыx сигналов разбиты на шестнадцать групп (числу групп соответствует количество входных мультиплексо-ровJ по шестнадцать шин в каждой (числу шин в группе соответствует количество Информационных входов одного селектора-мультиплексора). Каждая группа шин подключена к информационньом входам одного из мультиплексоров так, что каждая шина в группе подключена только к одному из входов селектора-мультиплексора, соответствующего данной группе шин.

Восьмиразрядный код любого из кодируемых элементов определяется номером входного мультиплексора 1, к которому подключена шина данного элемента (четыре старших разряда кода) и номером входа мультиплексора, к которому подключена эта шина (четыре младших разряда кода). Выходные шины мультиплексоров 1 подключены к информационным входам селектора-мультиплексора 2 , причем номер входного мультиплексора, выход которого подключается ко входу мультиплексора 2, совпадает с номером этого входа. Выход мультиплексора 2, соединен с входом записи регистра выходного кода 4. Выходные шины четьРрех старших разрядов счетчика 3 соединены с входными информационными шинами четырех младших разрядов регистра 4, а выходные шины четырех младших разрядов счетчика 3 с входными информационными шинами четырех старших разрядов регистра 4. Одноименные входы дешифраторов мультиплексоров 1 соединены вместе и подключены к соответствующим выходным шинам четырех старших разрядов счетчика 3. Входы дешифратора мультиплексора 2 соединены с соответствующими выходными шинами четырех младших раз.рядов счетчика 3. Генератор 5 своим выходом подключен к счетному входу суётчика 3.

Шифратор работает следующим образом.

При подаче тактовых импульсов на счетный вход счетчика 3 происходит последовательное изменение кодовых , состояний на выходных шинах разрядов счетчика 3, которые подключены к соответствующим входам мультиплексоров 1 и 2. При этом происходит опрос входов селекторов-мультиплексоров 1 и 2, Поскольку выходные шины старших разрядов счетчика 3 подключены одновременно ко всем соответствующим входам дешифраторов-мультиплексоров 1-8 i-тые входы всех этих селекторов-мультиплексоров опрашиваются одновременно.

Подключение к входам дешифраторамультиплексора 2 шин четырех младш-их разрядов счетчика 3 обеспечивает опрос всех пходов мультиплексора 2

за время опроса одного i-ого входа всех селекторов-мультиплексоров 1. Пусть кодируемый сигнал 1 на входной шине,подключенной к третьему входу селектора-мультиплексора 1, выход которого подключен к второму 5 входу мультиплексора 2. Опрос третьих входов мультиплексоров 1 соответствует состоянию счетчика, при котором на шинах старших разрядов счетчика 3 появляется код ООН , а опросу

0 второго входа мультиплексора 2 соответствует состояние счетчика, при котором на шинах младших разрядов появляется код 0010.

Пока при опросе входов мультиплексоров 1, вход на котором имеется логическая 1, не опрошен, выходы всех мультиплексоров находятся в состоянии О. На выходе мультиплексора 2 также имеется логический О.

Q Когда на выходе счетчика 3 устанавливается код ООН, т.е. опрашиваются третьи входы мультиплексоров 1, на выходе мультиплексора 2 появляется логическая 1, и в этом состоянии выход остается до тех пор, пока

состояние старших разрядов не изменится. Сигнал 1 с выхода мультиплексора 1 поступает на второй вход сулектора-мультиплексора 2. При очередном цикле опроса его входов на

0 выходе его появляется 1 при появлении на шинах младших разрядов счетчика 3 кода 0010. Логическая 1 с выхода мультиплексора 2 поступает на вход записи регистра 4 выходного кода и в этот регистр записывается код данного сигнала 00100011.

Использование мультиплексоров, счетчика и генератора тактовых импульсов выгодно отличает предлагаемый

Q шифратор от известного, так как позволяет сократить количество микросхем высокой степени интеграции при кодировании большого количества входных сигналов. При кодировании 256 сигналов количество используемых микросхем сокращается на 47%. Сокращение количества многовходовых микросхем улучшает топологию печатной платы, что повышает технологичность устройства. Уменьшение связей

0 между элементами схемы повышает надежность устройства.

Формула изобретения

Шифратор, содержащий регистр входного кода,отличающийс я тем, что, с целью упрощения, он содержит мультиплексоры, счетчик и генератор тактовых импульсов,

причем шины входных сигналов подключены к информационным входам входных мультиплексоров, выход каждого из которых соединен с одним из информационных входов выходного мультиплексора, выход которого СОРДИИОН с входом записи регистра выходного кода, выход генератора тактовых импульсов соединен с входом счетчика, выходы младших разрядов которого подключены к входс1м управления выходного мультиплексора и к входс м соответствующих старших разрядов регистра выходного кода, а выходы соответствующих старших разрядов подключены к входам управления входных мультиплексоров

и к входам соответствующих младших разрядов регистра выходного кода.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 443476, кл. Н 03 К 13/24, 1971.

2.Каталог интегральных микросхем. Т.1, Центральное конструкторское бюро, 1978, с. 336, рис. 6 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

Вк.О

бх.

вл.2

вх.1$

5Д./5

ffxff

ML

Bulf

/Ул

Авторы

Даты

1981-08-23—Публикация

1979-04-17—Подача