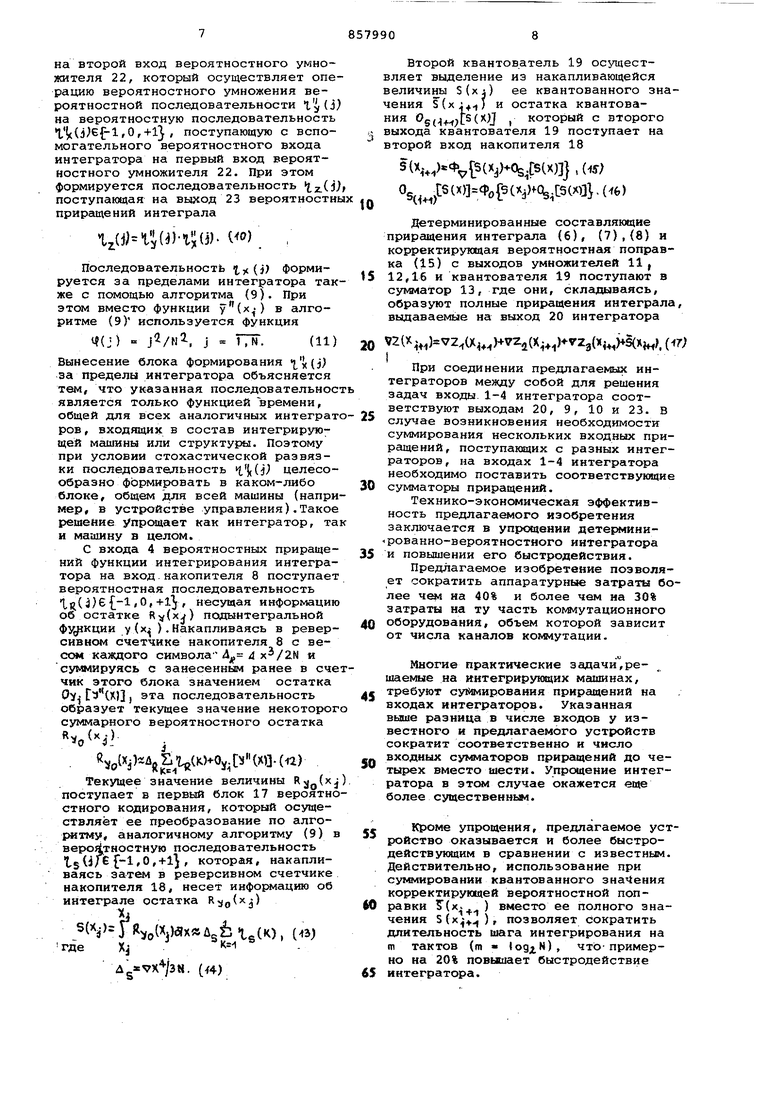

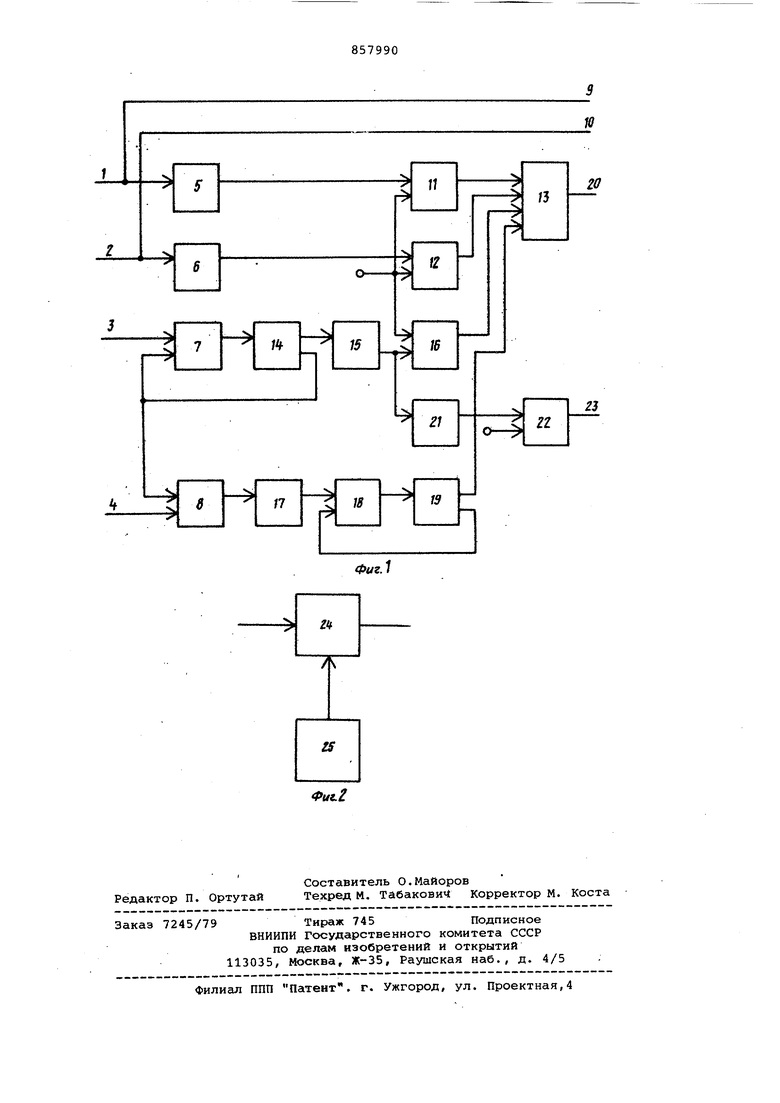

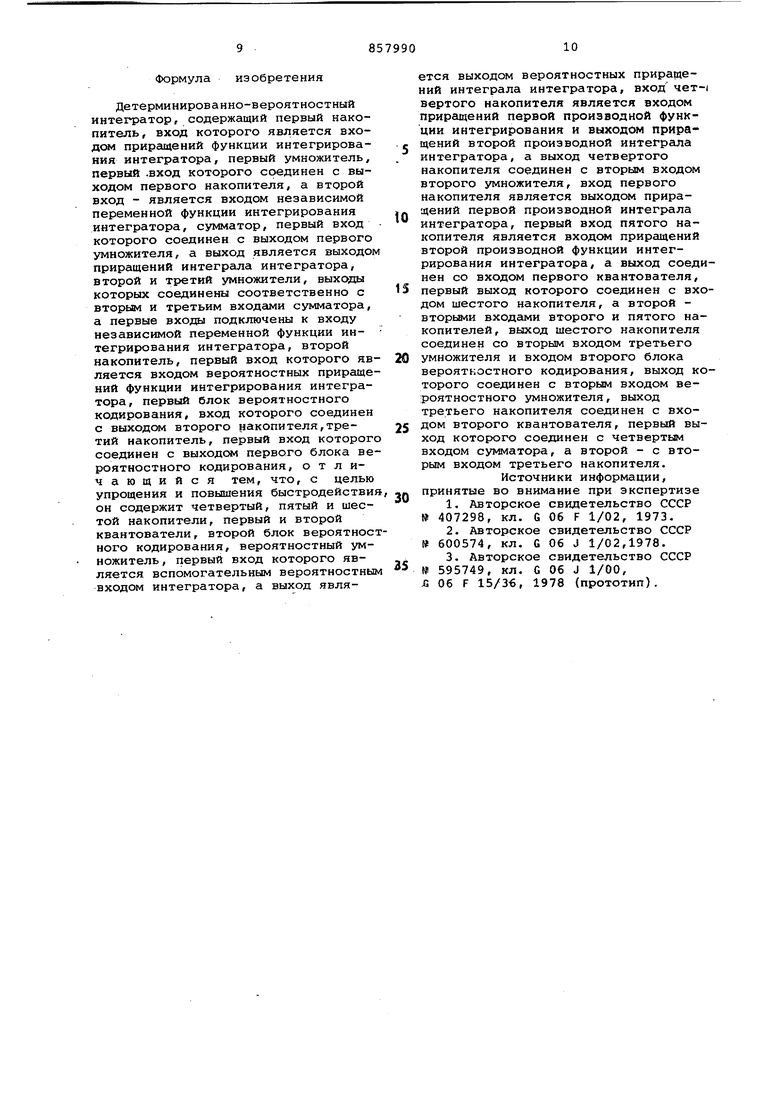

рала, вход которого является входом вероятностных приращений . Однако такое устройство требует больших аппаратурных затрат при его реализации, имеет большое число входов и выходов, что также приводит к усложнению устройства и аппаратуры коммутации. Кроме того, устройство об ладает недостаточно высоким быстродействием. Цель изобретения - упрощение и повышение быстродействия интегратоpa. Поставленная цель достигается тем что детерминированно-вероятностный интегратор, содержащий первый накопитель , вход которого является входом приращений функции интегрирования интегратора, первый умножитель, первый вход которого соединен с выходом первого накопителя, а второй вход - является входом независимой переменной функции интегрирования интегратора, сумматор, первый вход которого соединен с выходом первого умножителя , а выход является выходом приращений интеграла интегратора, второй и третий умножители, выходы которых соединены соответственно с вторым и третьим ВХОДС1МИ сумматора, а первые входы подключены к входу независимой переменной функции интегрирования интегратора, второй накопитель, первый вход которого является входом вероят ностных приращений функции интегриро вания интегратора, первый блок вероятностного кодирования, вход которог соединен с выходом второго накопител третий накопитель, первый вход которого соединен с выходом первого блока вероятностного кодирования, допол нительно содержит четвертый, пятый и шестой накопители, первьш и второй квантователи, второй блок вероятност ного кодирования, вероятностный умножитель, первый вход которого является вспомогательным вероятностным входом интегратора, а выход является выходом вероятностных приращений интеграла интегратора, вход четвертого накопителя является входом приращений первой производной функции интег рирования и выходом приращений второ производной интеграла интегратора,а выход четвертого накопителя соединен с вторым входом второго умножителя, входпервого накопителя является выходом приращений первой производной интеграла интегратора, первый вход пятого накопителя является входом приращений второй производной функции интегрирования интегратора, а выход соединен с входом первого кван тователя, первый выход которого соединен с входом шестого накопителя, а второй - с вторыми входами второго и пятого накопителей, выход шестого накопителя соединен с вторым входом третьего умножителя и входом второгр блока вероятностного кодирования, выход которого соединен с вторым входом вероятностного умножителя, выход третьего накопителя соединен с входом второго квантователя, первый выход которого соединен с четвертым входом сумматора, а второй - с вторым входом третьего накопителя. На фиг. 1 представлена блок-схема интегратора; на фиг. 2 - блок-схема блоков 17 и 21 вероятностного кодирования. Интегратор имеет вход 1 приращений функции интегрирования, вход 2 приращений первой производной функции интегрирования, вход 3 приращений второй производной функции интегрирования, вход 4 вероятностных приращений функции интегрирования, первый накопитель 5, четвертый накопитель 6, пятый накопитель 7, второй накопитель в, выход 9 приращений первой производной интеграла, выход 10 приращений второй производной интеграла, первый умножитель 11,второй умножитель 12, сумматор 13, первый квантователь 14, шестой накопитель 15,третий умножитель 16, первый блок 17 вероятностного кодирования, третий накопитель 18, второй квантователь 19, выход 20 приращений интеграла, втоЕЮй блок 21 вероятностного кодирования, вероятностный умножитель 22 и выход 23 вероятностных приращений интеграла. Вход первого накопителя 5 подключен к входу 1 приращений функции интегрирования интегратора и к выходу 9 прирсШ1ений первой производной интеграла интегратора. Выход первого накопителя 5 соединен с nepsaw входом первого умножителя 11, выход которого соединен с первым входом сумма-гора 13. Выход сукматора 13 подключен к выходу 20 приращений интеграла ннт тегратора. Вход четвертого накопителя б подключен к входу 2 приращений первой производной функции интегрирования интегратора и к выходу 10 приращений второй производной интеграла интегратора. Выход четвертого накопителя 6 соединен с вторым входом второго умножителя 12, выход которого соединен с вторым входом сумматора 13. Первый вход пятого накопителя 7 подключен к входу 3 приращений второй производной функции интегрирования интегратора, а выход соединен с входом первого квантователя 14, первый выход которого соединен с входом шестого накопителя 15, а второй выход,- с вторыми входами пятого 7 и второго 8 накопителей. Выход шестого накопителя 15 соединен с входом второго блока 21 вероятностного кодирования и вторым входом третьего умножителя 16,выход которого соединен с третьим входом сумматора 13. Первые входы второго 12 и третьего 16 умножителей и второй вход первого умножителя -11 подключены к входу независи мой переменной функции ннтегрирования интегратора. Выход второго блока 21 вероятностного кодирования соедине.н с вторым входом вероятност ного умножителя 22, первый вход которого подключен к вспомогательному верюятностному входу интегратора,а выход - к выходу 23 вероятностных приращений интеграла интегратора.Пе вый вход второго накопителя 8 подключен к входу 4 вероятностных приращений функции интегрирования интегратора, а выход соединен с вхоцом первого блока 17 вероятностного кодирования, выход которого соедине первым входом третьего накопителя 8. Выход третьего накопителя 18 соединен с входом второго кеантоаат ля 19, перШАй выход которого соедин с четвёртым входам сугвиатора 13, а второй выход - с вторым входом трет его накопителя 18. Каждый блок вероятностного кодирования состоит из блока 24 сравнения и датчика 25 случайных чисел, выход которого соединен с первьм вх дом блока 24. Второй вход блока 24 является входом блока вероятностног кодирования, а выход - выходом блок вероятностного кодирования. Устройство работает следующим образом. С входов 1, 2 и 3 интегратора в накопители 5, 6 и 7 поступают приращения подынтегральной функции Ду ( ) ее первой Ду(х) и второй ду() производных соответственно. Одновременно приращения ДУ(А) и Ду() уже в качестве приращений первой д z(x.- } и второй az(x) производных интеграла поступают на выходы 9 и 10 интегратора соответственно. В накопителях 5 и 6 приращения лу(х;|), йу{х с помощью сумматоров складываются соответственно со значениями подынтегральной функции у() и ее производной у (х«), храня1чимися в регистрах этих накопителей с предыдущего шага интегрирования.При этом образуются значения указанных функций на текущем шаге интегрирования

у (x,j) у () + йу(х ) (1)

у (х.) у (х . ) + ЬуСхЛ (2) Л 1

В накопителе 7 приращение (х.) с помощью сумматора складывается с остатком второй производной подынтегральной функции 0. (;i) образованным на предыду{цем шаге вычислений и хранящемся в регистре накопителя 7. Полученная сумма поступает в квантователь 14, который осуществляет над ней операцию квантовагде (j) равномерно распределенные случайные числа, генерируемые в моменты времени j 1 1N;

N числа статистических испытаний, проводимых на одном шаге интегрирования дх.

С выхода блока 21 вероятностная 65 последовательность iVU) поступает ния с выделением кванта ду(х,) и нового значения остатка квантования Эу (xj , поступающего с выхода остатка квантования блока 14 на второй вход накопителя 7 в его освободившийся регистр ),.i:nx)3. (3) : (x) ,0 Ov(., уЪ),{4) где Ф„ операции квантования и выделения остатка квантования соответственно. Остаток квантования Оу,()1 в качестве начального условия заносится также в накопитель 8. Полученное квантованное приращение ) поступает в накопитель 15, где оно с помощью сумматора складывается с квантованным значении второй производной подынтегральной функции (х ) образоеанньм на предыдущие шаге вычислений и хранящееся в регистре накопителя 15. При этом формируется новое значение этой функции на текущем шаге интегрирования уЧх. ) У (х) + Ду(х. ) . (5) Новые значения функции у( ) , у (х.:) и у (х,О с выходов накопителей 5, 6 и 15 поступают в умножители 11, 12 и 16, , имея на вторых входах приращения независимой переменной Д)ц , осуществляют операции умножения соответственно Дг ( ) v(x)-дх, (6) Дг,(х.) у (х,-).(Дх2/2). (7) Л2(х ) у(х. )-(AxV6). (8) Значения функции у (х,- ) г кроме того, поступают на вход второго блока 21 вероятностного кодирования, который осуществляет их преобразование в вероятностную последовательность е -1,0, в соответствии с алгоритмом 4BuwP f ibecAw(i)l5(x,-)in , . ) о , если/х(,-)|5(х.)ь HN, , на второй вход вероятностного умножителя 22, который осуществляет операцию вероятностного умножения вероятностной последовательности Ч1(л) на вероятностную последовательность .((J Cf-ljOf+lJ , поступающую с вспомогательного вероятностного входа интегратора на первый вход вероятностного умножителя 22. При этом формируется последовательность ..(Л поступающая на выход 23 вероятностны приращений интеграла tz.aMi()t;;(j)) , Последовательность 4-(j) формируется за пределами интегратора также с помощью алгоритма (9). При этом вместо функции у () в алгоритме (9) используется функция ((j) j2/Ni, j 1,N. (11) 2Q Вынесение блока формирования Lxlj) за пределы интегратора объясняется тем, что указанная последовательнос является только функцией Ъремени, общей для всех аналогичных интеграт ров, входтаоих в состав интегрирующей машины или структуры. Поэтому при условии стохастической развязки последовате(льность tj((j целесообразно формировать в каком-либо блоке, общем для всей машины (напри мер, в устройстве управления).Такое решение упрощает как интегратор, та и машину в целом. С входа 4 вероятностных приращений функции интегрирования интегратора на вход.накопителя 8 поступает вероятностная последовательность {( j)6 -1 «О,+iy, несущая информацию об остатке RN/(X.|) подынтегральной фу ркции у (х ) .Накапливаясь в реверсивном счетчике накопителя 8 с весом каждого символа- djj 4 и суммируясь с занесенным ранее в сче чик этого блока значением остатка )3 ) эта последовательность образует текущее значение некоторог суммарного вероятностного остатка (j)«ujjg 7(K)Oj.3(xa.(a) Текущее значение величины ,( поступает в первый блок 17 вероятно стного кодирования, который осуществляет ее преобразование по алгоритму, аналогичному алгоритму (9) вероятностную последовательность tsU/fef-l,0,+l} , которая, накапливаясь затем в реверсивном счетчике накопителя 18, несет информацию об интеграле остатка J iR:/o X)ax«usf31 (К), («) где Xj 1 Ag«VX /3N. (4) Второй квантователь 19 осущестляет выделение из накапливающейся еличины S(xi) ее квантованного знаения S(x;4-i) и остатка квантования Og(S(X)J , который с второго выхода квантователя 19 поступает на второй вход накопителя 18 . .(5; ,o{scV4 i:5W3i. (е) Детерминированные составляющие приращения интегреша (6), (7),(8) и корректирующая вероятностная поправка (15) с выходов умножителей 11 , 12,16 и квантователя 19 поступают в сумматор 13, где они, складываясь, образуют полные приращения интеграла, выдаваемые на выход 20 интегратора V2(X .(X)+VZ2((Xi,S(XH,. (7) При соединении предлагаемых интеграторов между собой для решения задач входы. 1-4 интегратора соответствуют выходам 20, 9, 10 и 23. В случае возникновения необходимости суммирования нескольких входных приращений, поступакйцих с разных интеграторов, на входах 1-4 интегратора необходимо поставить соответствующие сумматоры приращений. Технико-экономическая эффективность предлагаемого изобретения заключается в упрощении детерминированно-вероятностного интегратора и повышении его быстродействия. Предлагаемое изобретение позволяет сократить аппаратурные затраты более чем на 40% и более чем на 30% затраты на ту часть ко1 мутационного оборудования, объем которой зависит от числа каналов колмутации. Многие практические задачи,решаемые на интегрирующих машинах, требуют су1ймирования приращений на входах интеграторов. Указанная выше разница в числе входов у известного и предлагаемого устройств сократит соответственно и число входных сумматоров приращений до четырех вместо шести. Упрощение интегратора в этом случае окажется еще более существенным. Кроме упрощения, предлагаемое устройство оказывается и более быстродействующим в сравнении с известным. Действительно, использование при суммировании квантованного значения корректирующей вероятностной поправки 5(хк ) вместо ее полного значения S(), позволяет сократить длительность шага интегрирования на ш тактов (т ), что-примерно на 20% повышает быстродействие интегратора. Формула изобретения Детерминированно-вероятностный интегратор, содержащий первый накопитель , вход которого является вход ял приращений функции интегрирования интегратора, первый умножитель, первый .вход которого соединен с выходом первого накопителя, а второй вход - является входом независимой переменной функции интегрирования интегратора, сумматор, первый вход которого соединен с выходом первого умножителя, а выход является выходо приращений интеграла интегратора, второй и третий умножители, выходы которых соединены соответственно с вторым и третьим входами сумматора, а первые входы подключены к входу независимой переменной функции интегрирования интегратора, второй накопитель, первый вход которого яв ляется входом вероятностных прираще ний функции интегрирования интегратора, первый блок вероятностного кодирования, вход которого соединен с выходом второго накопителя,третий накопитель, первый вход которог соединен с выходом первого блока ве роятностного кодирования, отличающийся тем, что, с целью упрощения и повышения быстродействи он содержит четвертый, пятый и шестой накопители, первый и второй квантователи, второй блок вероятнос ного кодирования, вероятностный умножитель , первый вход которого является вспомогательным вероятностны входом интегратора, а выход является выходом вероятностных приращений интеграла интегратора, вход чет-i вертого накопителя является входом прираццений первой производной функции интегрирования и выходом приращений второй производной интеграла интегратора, а выход четвертого накопителя соединен с вторым входом второго умножителя, вход первого накопителя является выходом приращений первой производной интеграла интегратора, первый вход пятого накопителя является входе приращений второй производной функции интегрирования интегратора, а выход соединен со входом первого квантователя, первый выход которого соединен с входом шестого накопителя, а второй вторЬЕ и входги и второго и пятого накопителей , выход шестого накопителя соединен со вторым входом третьего умножителя и входом второго блока вероятностного кодирования, выход которого соединен с вторым входом вероятностного умножителя, выход третьего накопителя соединен с входом второго квантователя, первый выход которого соединен с четвертым входом cyMviaTopa, а второй - с вторым входом третьего накопителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 407298, кл. G 06 F 1/02, 1973. 2.Авторюкое свидетельство СССР W 600574, кл. G 06 J 1/02,1978. 3.Авторское свидетельство СССР № 595749, кл. G 06 J 1/00, 06 F 15/36, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Детерминированно-вероятностный цифровой интегратор | 1975 |

|

SU600574A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| ДЕТЕРМИНИРОВАННО-ВЕРОЯТНОСТНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU428412A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU407298A1 |

| Детерминированно-вероятностный цифровой интегратор | 1975 |

|

SU595749A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

Авторы

Даты

1981-08-23—Публикация

1979-12-05—Подача