ДЕТЕРМИНИЮВАННО-ВЕРОЯТНОСТНЫЙ ЦИФРОВОЙ

(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Детерминированно-вероятностный интегратор | 1979 |

|

SU857990A1 |

| Детерминированно-вероятностный цифровой интегратор | 1975 |

|

SU595749A1 |

| ДЕТЕРМИНИРОВАННО-ВЕРОЯТНОСТНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU428412A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU407298A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Детерминированно-вероятностный интегратор | 1976 |

|

SU667974A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1975 |

|

SU636639A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых интегрирующих машишх для цифрового моделирования и управления.

Известен цифровой интегратор, построенный g m основе принципа детерминированного-вероятностного представления и переработки информации 1 , который содержит блок формироваршя подьштегральной функции, блок формирования приращения интеграла по формуле прямоугольников, блок фор- « мирования коррекции и блок формирования полного приращения интеграла.

Точность и скорость интегрирования указанного интегратора для заддч моделирования и управления в реальном и опережающем масппабе време- jj ни недостаточно высокие.

Наиболее близок по технической сущности к изобретению цифровой интегратор 2, содержащий накопительный сумматор, вход которого является входом детерминированного пртращения инте- 20 гратора, а выход подсоединен к первому входу первого умножителя, второй вход которого служит входом независимой переменной интегратора, выход первого умножителя подсоединен к первому входу блока суммирования, выход которого явля- 25

ется выходом полного приращения интегратора, первый и второй логико-арифметические блоки, первые входы которых - это соответственно первьш и второй информационные входы интегратора, вторые входы связаны между собой и служат входом вероятностного вспомогательного приращения интегратора, а третьи входы соединены с входом независимой переменной интегратора, выход первого логико-арифметического блока является выходом вспомогательного вероятностного приращения интегратора, выход второго логико-арифметического блока подключен к второму входу блока суммирования.

В зтом интеграторе разность между нсходным оптилом и его ступенчатой аппроксимацией, вычисляемая приближенным вероятностным способом, имеет относительно больщую величину, поэтому общая точность интегрирования таким устройством в ряде случаев оказьшается недостаточной.

Цель изобретения - повьпиение точности вычисления.

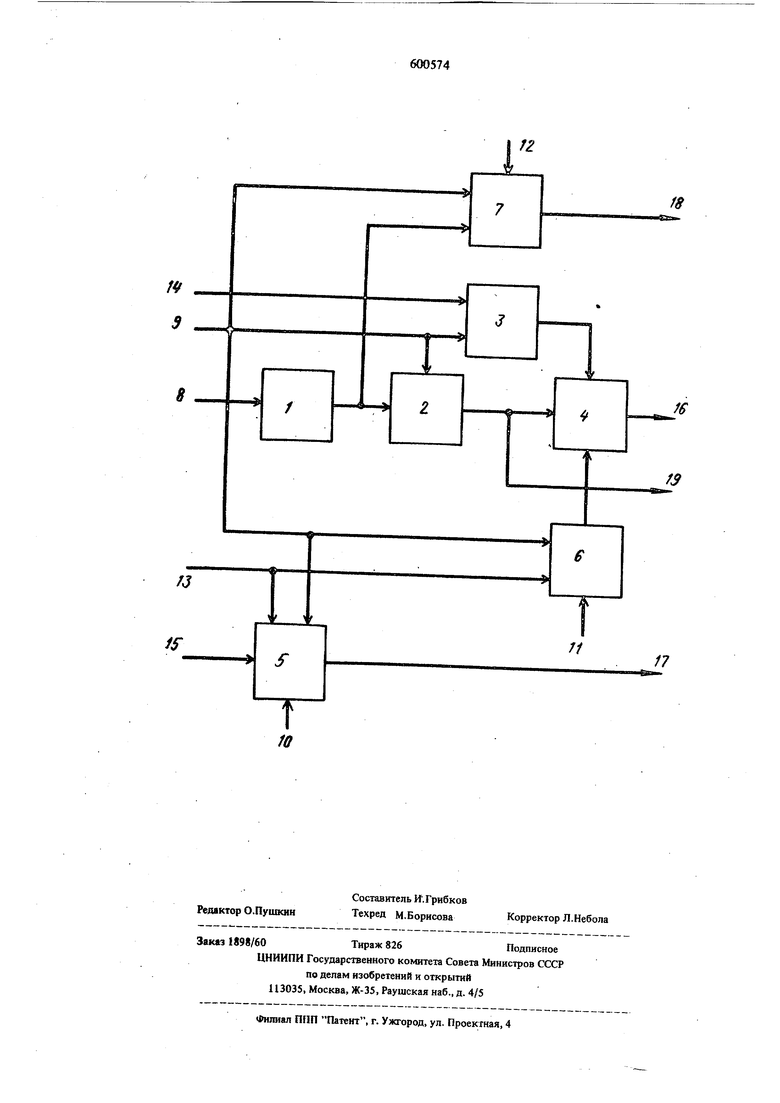

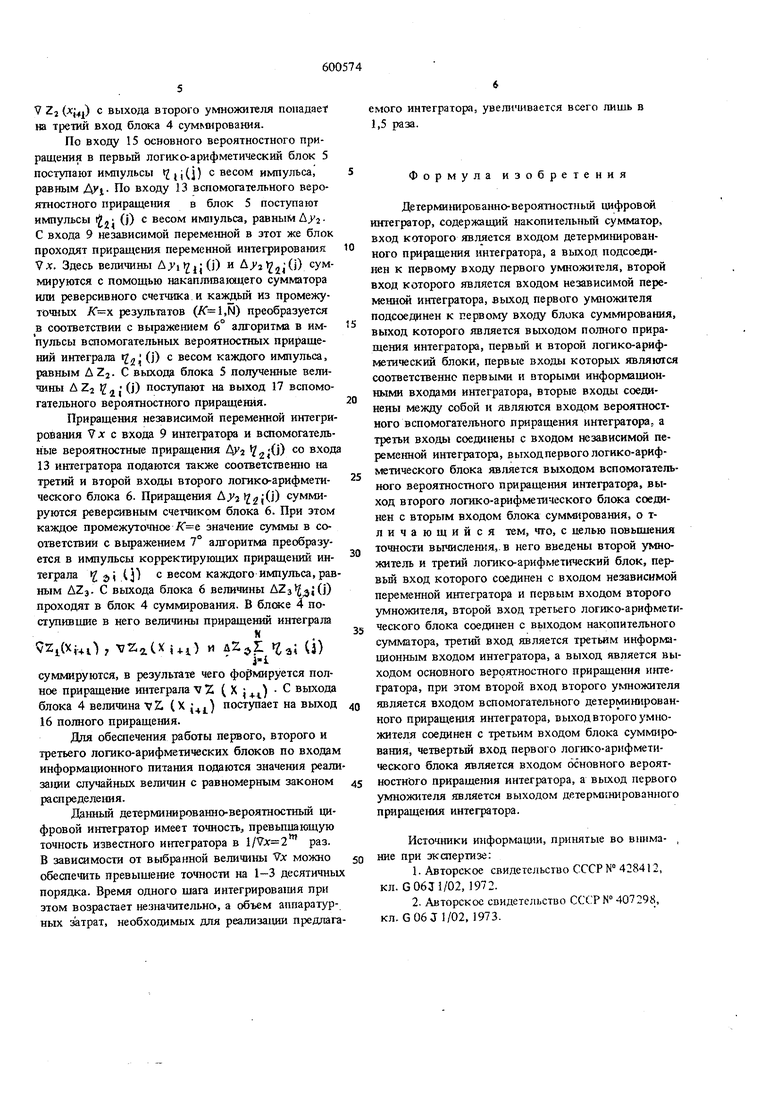

Это достигается тем, что в детерминированновероятностный цифровой интегратор введены второй умножитель и третий логико-арифметический блок, первьш вход которого соединен с входом независимой перемеиной интегратора и первым вхо дом второго умножителя второй вход третьего логико-арифметического блока - с выходом шкопительного сумматора, третий вход является третьим информационным входом иитегратора, а выход служит выходом основного вероятностного приращения интегратора. При этом второй вход второго умножителя - это вход вспомогательного детерминированного приращения интегратора, выход второ го умножителя соединен с третьим входом блока суммирования, четвертый вход первого логико-ари метического блока является входом основного вероятностного приращения интегратора, а выход первого умножителя - выходом детерминированного приращения интегратора. Повынюние точности при заданной скорости вы чиспенн я достигается путем перераспределения информации между . детерминированным и вероятностным каналами. В реэультате этого перерашределения в детерминированном канале кроме основного, детерминированного приращения интеграла вычисляется также его вшомогательное детермипирсжанное приращение, на величину которого соответственно уменьшается та часть информации, которая обрабатьтается в вероятностном канале интег{йтора. Интегратор работает в соответствии с алгорит1° у(х) y() +7у(х); 2° 7Zi(x,.,j) у(х-) 7х; 3° V2, (x,) 1 7у, (x;J 4° V Z (Xj,,) V Z, (x.,) + V Za (j,,) + 4.i(J) fbmv(Kj),ecnu/Ui(jb)y(xj)|-, (H 0,ecnu/Uj(j)(Xi)U Oi|U(j)imaxY; &iu«l Y44 ii(,i22i СЮ, 642i(i)(i)Vi,|iZii(«Hiy4Z,iU)h p,ec«ii /«i(i)H ViiA-.i)iVaf. C) I r (i)Htax AViJj..i,(i)(3)I; (,w 7V.J « / Jii HAY2gi2.iWI; 0.i|U i} HfaxtAy,.)I здесь V V -X- ; : 1, W j K 1,Й }tiaxy vX «xlAyif.Z,;(j) tt(0(XVKlvx AZ .) 3jHa чертеже представлена структурная схема детерминированно-вероятностного цифрового интегратора, вьшолняющего сшерацию интегрирования по независимой переменной в соответствии с приведенным алгоритмом. Она состоит из накопительного сумматора 1, умножителей 2, 3, блока 4 суммирования, логикоарифметических блоков 5-7, входа 8 детерминированного приращения, входа 9 независимой переменной, информационных входов 10-12, входа 13 вспомогательного вероятностного приращения,-входа 14 вспомогательного детерми1ШроБанного приращения, входа 15 основного вероятностного приращения, выхода 16 полного приращения, выхода 17 вспомогательного вероятностного приращения, выхода 18 основного вероятностного приращения, выхода 19 детерминированного прираще1шя. По входу 8 детерминированного приращения в ткопите;п ньш сумматор 1 поступает приращение подьштеграяьной функции V у (х ). Здесь оно суммируется с предьщущим значением подынтегральной функции у (i-i), хранящимся в регистре сумматора, в результате чего образуется значение подынтегральной функции в i-й точке интегрирования. Образовавшаяся величина у(х ) с выхода накопительного сумматора 1 прохбдит m первый вход первого умножителя 2 и на второй вход третьего логико-арифметического блока 7. На первый вход блока 7 и второй вход умножителя 2 подается приращение нереленной интегрирования Vx. В умножителе 2 величины у(х) viV х перемножаются, в результате чего получается основное детерминированное приращение интеграла V Zi (,Vj), которое далее поступает на первый вход блока 4 суммирования и на выход 19 детерминированного приращения. В третьем логико-арифметическом блоке 7 в соответств1ш с выраже}шем 5 алгоритма осуществляется преобразование величины у (л:,; ) в вероятностньш импульсньш поток t, j (j) е + Ij с весом каждого импульса, равным Д Zj. С выхода блока 7 величины AZj (} поступают на выход 18 основного вероятностного приращения. По входу 14 вспомогательного детерминированного приращения на вход второго умножителя 3 поступает приращегше у {x. Здесь, в соответствии с выражвш1ем 3 алгоритма, величина У ) ум11ожается на коэффициент, равный Vx/2. Получе1шое в результате этого умножения вшомогателыloe детерминирова1шое приращевме V Zj (XJ4|) с выхода второго умножителя попадает на третий вход блока 4 cyм oфoвaния. По входу 15 основного вероятностного приращения в первый логико-арифметический блок 5 поступают импульсы ZjiCJ) свесом импульса, равным ЛХл- По входу 13 вспомогательного вероятностного прираще1шя в блок 5 поступают импульсы . 0) с весом импульса, равным входа 9 независимой пер еме1шой в этот же блок проходят приращения перемеиной интегрирования Vx. Здесь велишны () и ) суммируются с помощью накапшшакщего сумматора или реверсивного счетчика и каждый из промежуточных К результатов (,N) преобразуется в соответствии с выражением 6° алгоритма в импульсы вспомогательных вероятностных приращений интеграла (j) с весом каждого импульса, равным Д Zj. С выхода блока 5 полученные величины Л Za (j) поступают на выход 17 вспомогательного вероятностного приращения. Приращения не:ивисимой переменной интегрирования Vjc с входа 9 интегратора и вспомогательные вероятностные приращения Avj -(j) со вход 13 интегратора подаются также соответственно на третий и второй входы второго логико-арифметического блока 6. Приращения суммируются реверсивным счетчиком блока 6. При этом каждое промежуточное значение суммы в соответствии с выражением 7° алгоритма преобразуется в импульсы корректирующих прираще1пш интеграла « Л с весом каждого импульса,рав ным AZs- С выхода блока 6 величины (j) проходят в блок 4 суммирования. В блеже 4 поступивщие в него величины приращений интеграла Н ) VZi(Xui) И «га; (j) суммируются, в результате чего формируется полное приращение интеграла VZ ( X : ,) С выхода блока 4 величина v2. (X ( поступает на выход 16 полного приращения. Для обеспечения работы первого, второго и третьего логико-арифметических блоков по входам информационного питания подаются значения реали зации случайных величин с равномерным законом распределения. Данный детерминированно-вероятностньш цифровой интегратор имеет точность, превьпшющую точность известного интегратора в раз. В зависимости от выбранной величины Vx можно обеспечить превышение точности на 1-3 десятичны порядка. Время одного шага интегрирова1шя при этом возрастает иезначительно, а объем аппаратурных затрат, необходимых для реализации предлага емого интегратора, увелишвается всего лишь в 1,5 раза. Формула изобретения ДетерминироБанно-вероятностньш цифровой интегратор, содержащий накопительньп сумматор, вход которого является входом детерминированного приращения интегратора, а выход подсоединен к первому входу первого умножителя, вторюй вход которого является входом независимой переменной интегратора, выход первого умножителя подсоединен к первому входу блока суммирования, выход которого является выходом полного приращения интегратора, первьш и второй логико-арифметический блоки, первые входы которых являются соответственно первыми и вторыми информационными входами интегратора, вторые входы соединены между собой и являются входом вероятностного вспомогательного приращения интегратора, а третьи входы соединены с входом независимой переме1шой интегратора, выход первого логико-арифметического блока является выходом вспомогательного вероятностного приращения интегратора, выход второго логико-арифметического блока соединен с вторым входом блока суммирования, о тличающийся тем, что, с целью повышения точности вычисления,, в него введены второй умножите.11ь и третий логико-арифметический блок, первый вход которого соединен с входом независимой переменной интегратора и первым входом второго умножителя, второй вход третьего логико-арифметического блока соединен с выходом накопительного сумматора, третий вход является третьим информационным входом интегратора, а выход является выходом основного вероятностного приращения ирггегратора, при этом второй вход второго умножителя является входом вспомогательного детерминированного приращения интегратора, вььход второго умножите.11я соединен с третьим входом блока суммирования, четвертьш вход первого логико-арифметического блока является входом основного вероятHocTHbro прирарления интегратора, а выход первого умножителя является выходом детерминированного приращения интегратора. Источники информации, принятые во внима- , ние при экспертизе: 1.Авторское свидетельство СССР № 428412, кл. G06ji/02, 1972. 2./ BTOpCKoe свидетельство СССР№407298, кл. G06 J1/02, 1973.

Авторы

Даты

1978-03-30—Публикация

1975-10-20—Подача