Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных ЭВМ и управляющих систем Известно микропрограммное устройство управления, содержащее блок памяти микропрограмм, блок проверки условий, регистры адреса, элемент И и триггер Lll Недостатком известного устройства являются ограниченные функциональные возможности, обусловленные невозможностью полезной реализации времени ожидания при выполнении основной микропрограммы работы. Наиболее близким ,по технической сущности к предлагаемому изобретению является микропрограммное устройство управления, содержащее блок памяти микропрограмм, блок проверки условий триггер управления, элемент И, два регистра адреса 2 . Недостатком известного устройства являются ограниченные функциональные возможности, которые обусловлены невозможностью реализации управления упорядоченными по времени использова ния результатов микропрограммами. Эт приводит к сужению области применения устройства. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности реализации как неупорядоченных, так и упорядоченных по времени использования результатов микропрограмм. Эта цель достигается тем, что в микропрограммное устройство управления, содержащее два регистра адреса, выходы которых соединены с соответствующими входами блока памяти микропрограм 1, первый информационный выход которого является выходом устройства, адресный выход блока памяти микропрограмм соединен с первым входом блока проверки условий, первый управляющий выход которого соединен с единичным входом триггера-управления, нулевой вход которого является первым входом устройства, единичный выход триггера управления соединен с первым входом первого элемента И, выход которого соединен с первым управляющим входом второго регистра адреса, введены третий регистр адреса, регистр логических условий, шифратор, схема сравнения, элементы И, ИЛИ, причем первый вход :;хемы сравнения соединен с выходом третьего регистра адреса и с первым

входом второго элемента И, выход ко торого соединен с информационным входом второго регистра адреса, второй вход схемы сравнения соединен с выходом первого регистра адреса, выход схемы сравнения соединен с первым входом третьего элемента И и с первым входом первого элемента ИЛИ, второй вход третьехо элемента И соединен с выходом второго регистра адреса,второй вход первого элемента ИЛИ соединен с вторым управляющим выходом блока проверки условий, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого является вторым входом устройства, второй вход второго элемент ИЛИ через шифратор и регистр логических условий соединен с вторым информационным выходом блока памяти микропрограмм, информационный выход блока проверки условий соединен с вторым входом первого элемента И и первым входом четвертого элемента И, второй вход которого соединен с нулевым выходом триггера управления и с первым управляющим входом первого регистра адреса, выход четвертого элемента И соединен с вторым управляющим входом первого регистра адреса, выход первого элемента ИЛИ соединен с вторым входом второго элемента И и с первым входом пятого элемента И, второй вхо которого является третьим входом устройства, единичный выход триггера управления соединен с вторым управляющим входом второго регистра адреса, выход третьего элемента И соединен с информационным входом первого регистра адреса, выход пятого элемента И соединен с входом третьег регистра адреса.

Введение новых элементов и связей позволяет при реализации произвольных параллельных микропрограмм реализовать дисциплину функционирования с учетом всех возможных вариантов взаимного состояния основной и параллельной микропрограмм, которые возникают в процессе их взаимодействия, и особенно, к моменту возникновения необходимости использования в основной микропрограмме результатов работы микроподпрограммы.

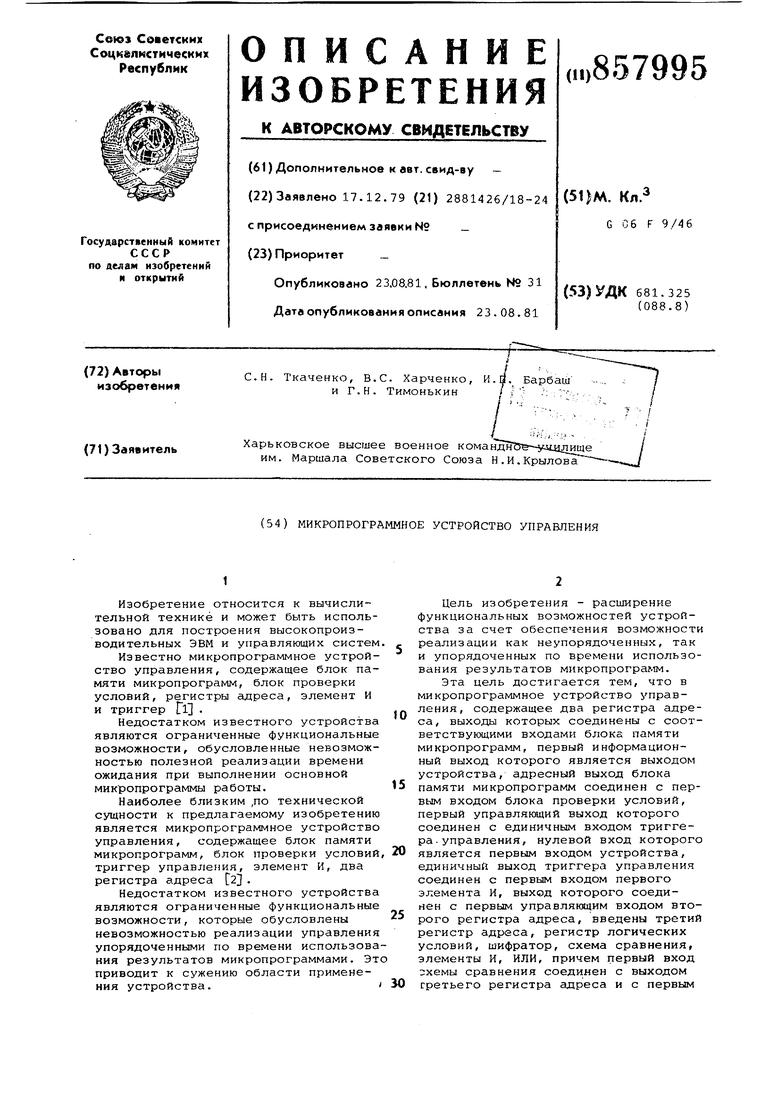

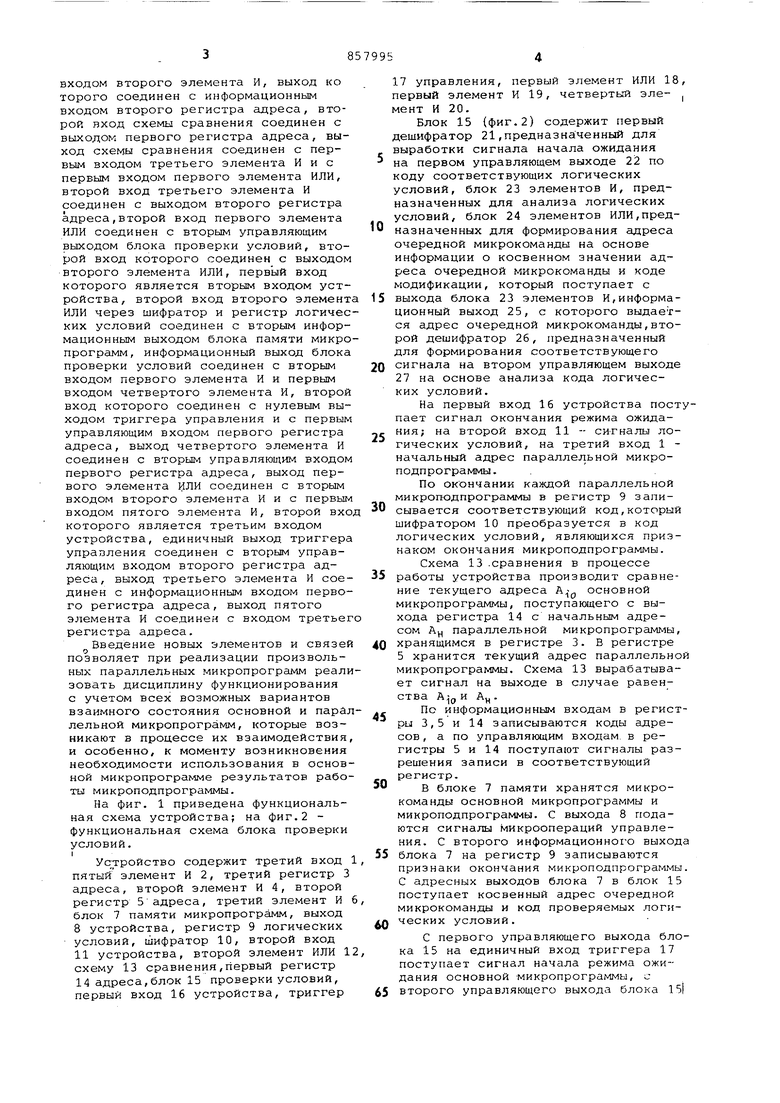

На фиг. 1 приведена функциональная схема устройства; на фиг.2 функциональная схема блока проверки условий.

Устройство содержит третий вход 1 пятый элемент И 2, третий регистр 3 адреса, второй элемент И 4, второй регистр 5адреса, третий элемент И 6 блок 7 памяти микропрограмм, выход 8 устройства, регистр 9 логических условий, шифратор 10, второй вход 11 устройства, второй элемент ИЛИ 12 схему 13 сравнения,первый регистр 14 адреса,блок 15 проверки условий, первый вход 16 устройства, триггер

17 управления, первый элемент ИЛИ 18 первый элемент И 19, четвертый элемент И 20.

Блок 15 {фиг.2) содержит первый дешифратор 21 ,предназначенный для выработки сигнала начала ожидания на первом управляющем выходе 22 по коду соответствующих логических условий, блок 23 элементов И, предназначенных для анализа логических условий, блок 24 элементов ИЛИ,предназначенных для формирования адреса очередной микрокоманды на основе информации о косвенном значении адреса очередной микрокоманды и коде модификации, который поступает с выхода блока 23 элементов И,информационный выход 25, с которого выдается адрес очередной микрокоманды,второй дешифратор 26, предназначенный для формирования соответствующего сигнала на втором управляющем выходе 27 на основе анализа кода логических условий.

На первый вход 16 устройства постпает сигнал окончания режима ожидания; на второй вход 11 - сигналы логических условий, на третий вход 1 начальный адрес параллельной микроподпрограммы.

По окончании каждой параллельной микроподпрограммы в регистр 9 записывается соответствующий код,который шифратором 10 преобразуется в код логических условий, являющихся признаком окончания микроподпрограммы.

Схема 13 .сравнения в процессе работы устройства производит сравнение текущего адреса основной микропрограммы, поступающего с выхода регистра 14 с начальным адресом Ац параллельной микропрограммы, хранящимся в регистре 3. В регистре 5 хранится текущий адрес параллельно микропрограммы. Схема 13 вырабатывает сигнал на выходе в случае равенства А(,и А„.

По информационным входам в регистры 3,5 и 14 записываются коды адресов , а по управляющим входам в регистры 5 и 14 поступают сигналы разрешения записи в соответствующий регистр.

В блоке 7 памяти хранятся микрокоманды основной микропрограммы и микроподпрограммы. С выхода 8 подаются сигналы Микроопераций управления. С второго информационного выход блока 7 на регистр 9 записываются признаки окончания микроподпрограммы С адресных выходов блока 7 в блок 15 поступает косвенный адрес очередной микрокоманды и код проверяемых логических условий.

С первого управляющего выхода блока 15 на единичный вход триггера 17 поступает сигнал начала режима ожидания основной микропрограммы, с второго управляющего выхода блока 15

на вход первого элемента ИЛИ 18 поступает признак окончания реализации параллельной микроподпрограммы.

Триггер 17 предназначен для управления режимами работы устройства. На нулевой вход 16 триггера 17 поступает сигнал окончания режима ожидания. Нулевое состояние триггера 17 соответствует режиму функционирования по основной микропрограмме, а в единичном состоянии триггера реализуется режим ожидания основной микропрограммы, в котором работает одна из параллельных микроподпрограмм.

Рассмотрим работу устройства. Все микропрограммы, реализуемые устройством, состоят из микроподпрограм1 1, которые могут в принципе выполняться в процессе выполнения основной микропрограммы. Однако в целя повышения производительности и быстр действия системы, которой управляет устройство, предусмотрено выполнение параллельных микроподпрограмм в режимах ожидания основной микропрограммы. При этом параллельно микроподпрограммы могут быть как упорядоченными во времени использования результатов, так и неупорядоченными. Рассмотрим функционирование устройства при реализации упорядоченных по времени использования результатов основной и параллельной микроподпрограмм, поскольку функциональная реализация неупорядоченных микропрограмм является частным случаем реализации неупорядоченных микропрограм

Основным режимом функционирования устройства является реализация основной микропрограммы. При этом триггер 17 находится в нулевом состоянии. В регистрах 3 и 5 хранятся начальный адрес очередной микропод про грс1ммы , которая реализуется параллельно с основной микропрограммой. При реализации основной микропрограммы адрес очередной микрокоманды записывается в регистр 14, который поступает в блок 7 памяти. С выхода 8 считываются сигналы микроопераций, с адресных выходов на блок .15 поступает косвенный адрес очередной микрокоманды, который через открытый элемент И 20 поступает на вхо регистра 14. При ветвлениях основной микропрограммы кОд проверяемых логических условий с блока 7 поступает на вход блока 15, на второй вхо которого со входа 11 устройства через элемент ИЛИ 12 поступают сигналы проверяемых логических условий, которые формируют адрес очередной микрокоманды основной микропрограммы

При необходимости перехода в режим ожидания по соответствующим логическим условиям блоком 15 вырабатывается сигнал,который устанавливает триггер 17 в нулевое состояние.Триггер 17 сигналом с единичного выхода

открывает элемент И 19 и разрешает работу регистра 5 и запрещает реализацию основной микропрограммы, текущий адрес которой запоминается в регистре 14. При этом регистр 5 считывает с блока 7 памяти микрокоманду Далее устройство функционирует аналогично режиму основной микропрограммы.

Если в режиме ожидания микроподпрограмма выполнится полностью, то она в последней своей микрокоманде вырабатывает признак окончания,который записывается в регистр 9 и хранится в нем.

Одновременно с второго управляющего блока 15 выдается сигнал окончания параллельной микроподпрограммы который через элемент ИЛИ 18 открывает элемент И 2, И 4. При этом начальный адрес очередной параллельной микроподпрограммы со входа 1 устройства через элемент И 2 записывается в регистр 3, а с него через элемент И 4 в регистр 5 и далее. Если режим ожидания не закончился, продолжается реализация параллельной микроподпрограммы с введенного нового начального адреса.

Если в процессе выполнения параллельной микроподпрограммы с входа 16 устройства поступает сигнал окончания режима ожидания, то триггер 17 устанавливается в нулевое состояние, задающее режим функционирования по основной микропрограмме, начиная с сщреса, хранящегося в регистре 14. Одновременно в регистре 5 запоминается адрес очередной микрокоманды параллельной микроподпрограммы, с которой следует начать работу в очередном режиме ожидания основной микропрограммы.

Если в процессе реализации основной микропрограммы по логике реализуемого процесса управления возникает необходимость в использовании результатов работы (реализации) параллельной микроподпрограммы, начиная с микрокоманды основной микропрограммы, то в (А.,2)-ой микрокоманде основной микропрограммы вырабатывается сигнал логических условий проверки окончания соответствующей микроподпрограммы. По этому сигналу производится блоком 15 проверка логических условий окончания микроподпрограмм, поступающих с выходов шифратора 10 через элемент ИЛИ 12. Если соответствующая микроподпрограмма реализована, то в (Л,-,5.)о микрокоманде блоком 15 организуется переход к микрокоманде основной микропрограммы, следующей за данной параллель ной микроподпрограммой.Если же данная параллельная микроподпрограмма не реализована полностью, то в (Af, )-ой микрокоманде срабатывает схема 13 сравнения. По сигналу схемы 13 открывается элемент И 6, через который в регистр 14 с регистра 5 переписывается адрес микрокоманды, на которой было прервано выполнение параллельной микроподпрограммы. Одновременно по сигналу схемы 13 через элемент ИЛИ 18 разрешается запись начального адреса очередной параллельной микроподпрограммы, как было описано. После этого устройство продолжает реализаг цию параллельной микроподпрограммы в режиме основной микропрограммы с адреса, записанного в регистр 14. После окончания реализации данной микроподпрограммы устройство продолжает функционирование по основной микропрограмме. При реализации устройством неупорядоченных по времени использования результатов микропрограмм основная микропрограмма реализуется независимо от параллельных микроподпрограмм Поэтому не возникает необходимости в выработке и проверке логических условий окончания параллельных микро подпрограмм и использования результатов, а также продолжения микроподпрограммы в режиме основной микропрограммы. Схема 13 сравнения в таком режиме не срабатывает, так как начальные адреса всех параллельных микроподпрограмм в этом случае превосходят адрес конечной микрокоманды основной микропрограммы. Таким образом, введение указанных новых элементов и связей позволяет реализовать в предлагаемом устройст параллельные процессы с произвольным отношением упорядочения по времени использования результатов. Формула изобретения Микропрограммное устройство упра ления, содержащее два регистра адреса, выходы которых соединены с соответствующими входами блока памя микропрограмм, первый информационны выход которого является выходом уст ройства, адресный выход блока памят микропрограмм соединен с первым вхо дом блока проверки условий, первый управляющий выход которого соединен с единичным входом триггера управле ния, нулевой вход которого является первым входом устройства, единичный выход триггера управления соединен первым входом первого элемента И, в ход которого соединен с первым упра ляющим входом второго регистра адре са, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности реализации как неупорядо-. ченных, так и упорядоченных по времени использования результатов микропрограмм, в него введены третий регистр адреса, регистр логических условий, шифратор, схема сравнения, элементы И, ИЛИ, причем первый вход схемы сравнения соединен с выходом третьего регистра адреса и с первым входом второго элемента И, выход которого соединен с информационным входом второго регистра адреса, второй вход схемы сравнения соединен с выходом первого регистра адреса, выход схемы сравнения соединен с первым входом третьего элемента И и с первым входом первого элемента ИЛИ, второй вход третьего элемента И соединен с выходом второго регистра адреса, второй вход первого элемента ИЛИ соединен с вторым управляющим выходом блока проверки условий, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого является вторым входом устройства, второй вход второго элемента ИЛИ через шифратор и регистр логических условий соединен с вто- рым информационным выходом блока памяти микропрограмм, информационный выход блока проверки условий соединен с вторым входом первого элемента И и первым входом четвертого элемента И, второй вход которого соединен с нулевым выходом триггера управления и с первым управляющим входом первого регистра адреса, выход четвертого элемента И соединен с вторым управляющим входом первого регистра адреса, выход первого элемента ИЛИ соединен с вторым входом второго элемента И и с первым входом пятого элемента И, второй вход которого является третьим входом устройства, единичный выход триггера управления соединен с вторым управлякхцим входом второго регистра адреса, выход третьего элемента И соединен с информационным входом первого регистра адреса, выход пятого элемента И соединен с входом третьего регистра адреса. I Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 437072, кл. G Об F 9/12, 1972. 2.Авторское свидетельство СССР № 643874, кл. G 06 F 9/16, 1979 (прототип).

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления | 1976 |

|

SU643874A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

25

24

27

26

Авторы

Даты

1981-08-23—Публикация

1979-12-17—Подача