,причем первый выход дешифратора управления подключен к нулевому входу триггера пуска и через первый элемент задержки к нулевому входу вторЛго триггера регистра внутренних логических условий, единичные и нулевые выходы второго и третьего 1ц иггеров регистра внутренних логичес -.

ких условий соединены соответственно с первым, вторым, третьим и четвертым входами дешифратора управления, второй выход которого подключен к выходу устройства, первому входу третьего элемента ИЛИ, третьему входу второго блока элементов И, первому входу четвертого элемента ИЛИ и второму входу третьего блока элементов И, третий выход дешифратора управления подключен к второму входу первого элемента И, выход которого через последовательно соединенные одновибратор, второй и третий элементы задержки соединен с управляющим входом первого регистра, выход одновибратора соединен с управляющим входом второго регистра, информационный выход которого подключен к первому управляющему входу устройства, выход второго регистра подключен к информационному входу первого регистра, выход которого соединен с первым входом седьмого

блока элементов И, выход второго элемента задержки соединен с вторым входом седьмого блока элементов И, выход которого подключен к выходу устройства, четвертый выход дешифратора управления сдединен через четвертый элемент задержки с первьп входом первого элемента ИЛИ, второй вход которого соединен с единичным входом триггера пуска и вторим входом шестогр блока элементов И, четвертый выход дешифратора управления соединен также с выходом устройства, выход четвертого элемента задержки соединен с вторым входом второго элемента ИЛИ, выход которого соединей с Нулевым входом третьего триггера регистра внутренних логических условий, единичный выход триггера управления соединен с вторым входом третьего элемента ИЛИ, выход которого подключен к второму входу пятого . блока элементов И, второму входу первого блока элементов И и четверт у входу блока проверки логических условий второй и третий управлякяцие выходы которого соединены соответственно с первым входом третьего элемента И и третьим входом пятого (блока элементов И, нулевой выход первого триггера регистра внутренних логических условий соединен с вторым входом третьего элемента И, выход которого соединен с нулевым входом триггера управления и вторым входом четвертого элемента ИЛИ, третий вход которого подключен к единичному входу триггера управления, выход четвертого элемента ИЛИ соединен со вторым входом второго элемента И, нулевой выход триггер а управления соединен с третьим входом третьего блока элементов и.

.2. Устройство управления по п. 1 о т л и ч а ю щ е е с я тем, что блок проверки логических условий срдержит дешифратор, два регистра, три блока элементов И, блок элементов Сумма по модулю два, два элемента И и элемент ИЛИ, причем первый выход депгафратора соед11нен с первыми входами первого и второго блока элементов И, второй выход дешифратора соединен с первым входом третьего блока элементов и, выход которого соединен с первым входом блока элементов сумма по модулю два, второй вход блока элементов сумма по модулю два подключен к втсгрому входу блока проверки логических условий, а выход - к адресному выходу проверки логических условий, первый вх;од блока проверки логических условий соединен с входом дешифратора, третий вход блока проверки логических условий соединен с вторым входом третьего блока элементов И и первыми группами входов первого и второго регистров, вторые группы входов.КОТО1ИЛХ соединены соответственно с выходами первого и второго блоков элементов И, первый выход первого регистра соединен с входом элемента и, выход которого является персам управляющим выходом блока проверки логических условий, второй управляющий выход которого соединен с выходом первого элемента И, второй выход первого регистра соединен с входами второго элемента И, выход которого является третьим управляющим выходом блока проверки логических условий, четвертый выход которого соединен с вторыми выходами первого и второго блоков элементов И.

Изобретение относится к вычислите ьнЪй технике и может быть использовано для построения высокопроизводительных вычислительных систем ; с микропрограммным управлением.

. ..Известномикропрограммное устройство Управления, содержащее блок памяти микропрограмм, блок проверки условий, триггер управления, элемент И, два регистра адреса .l .

Недостатками указанного устройства являются низкое быстродействие и узкая область применения, которые обусловлены неполным учетом множества взаимных состояний реализуемых в режиме мультипрограммирования мик ропрограмм (режим мультипрограммирования) ,: .

Наиболее близким к изобретению , по технической сущности и достига- ; емому эффекту является устройство / управления с параллельным выполнением микропрограмм, содержащее шесть блоков элементов И, элемент ИЛИ, Три блока элементов ИЛИ, элементИ, два регистра адреса, блок памяти микропрограмм, блок проверки логических условий, триггер пуска, генератор тактовых импульсов, триггер управления, регистр внутренних логических условий и дешифратор внутренних логйческих условий 2.

Недостатками известного устройства являются узкая область применения и низкое быстродействие, что обусловлено следующими причинами, В ука- ванном устройстве реализовано круговое-циклическое планирование для двух микропрограмм (основной и параллелльной), обладающих разным приоритетом. Вторая (параллельная) микропрограмма реализуется в режимах ожидания первой (основной) микропрограммы. По окончании ожидания первая микропрограмма прерывает выполнение второй и возобновляет свою работу с микрокоманды, следующей за микрокомандой ожидания. Таким образом, в целом дисциплина функционирования усТрЪйства является композицией двух дисциплин обслуживания микропрограмм: первая (основная) микропрограмма обслуживается по алгоритму; Первый пришел - первый обслужен, вторая (параллельная) микропрограмма обслуживается с абсолютным приоритетом, дообслуживанием и величиной очередного кванта обслуживания, зависящей от состояния (длительности режима ожидания) первой микропрограммы. Причем величина времени до обслуживания зависит от того про- . изошло ли прерывание параллельной микропрограммы в критическом участке или вне его - если прерывание произошло в критическом участке, то результаты предыдущей работы паргшлельной микропрограммы теряются и/

следовательно, время дообслуживания параллельной микропрограммы вновь становится равным потребному времени ее выполнения. Последнее.обстоятельство в устройстве-прототипе не учитывается и с использованием рассматриваемой структуры может быть реализовано путем программного анализа ситуации и организации в последующем повторной инициализации параллельной микропрограммы, на что потребуются значительные затраты времени. Композиция описанных дисциплин обслуживания при условии реализации в устройстве-прототипе накладывает следующие ограничения на реализуемые Микропрограммы и объект управления: вторая (параллельная) микропрограмма не должна иметь непрерываемых (Критических) участков, поскольку она может быть перервана основной микропрограммой по окончанию ожидания в произвольный- момент времени, вторая микропрограмма не может Иметь микрокоманд ожидания, обе лмикропрограммы должны осуществлять управление разными функциональными блоками (узлами, подсистемами) Объекта управления, т.е. в устройств отсутствуют специальные средства для сохранения информации о состоянии рбъекта управления, определяемой значением внешних логических условий в момент прерялвания выполнения одной микропрограмма и перехода к выполнению другой.

Условие отсутствия критических участков в параллельной микропрограмме приводит к тому, что в микропрограмме не должно быть неделимых операций, т,е. никакая последовательность микрокоманд не может задавать выполнение неделимых операций с ре- Iсурсами системы. При этом под ресурсом понимается любая компонента (аппаратная или программная) системы, которая может быть представлена процессу, реализующему микропрограмму. Указанные обстоятельства существенно сужают на практике область применения устройства-прототипа и, кроме того, уменьшают быстродействие устройства за счет потери информации при прерывании параллель ной микропрограммы основной.

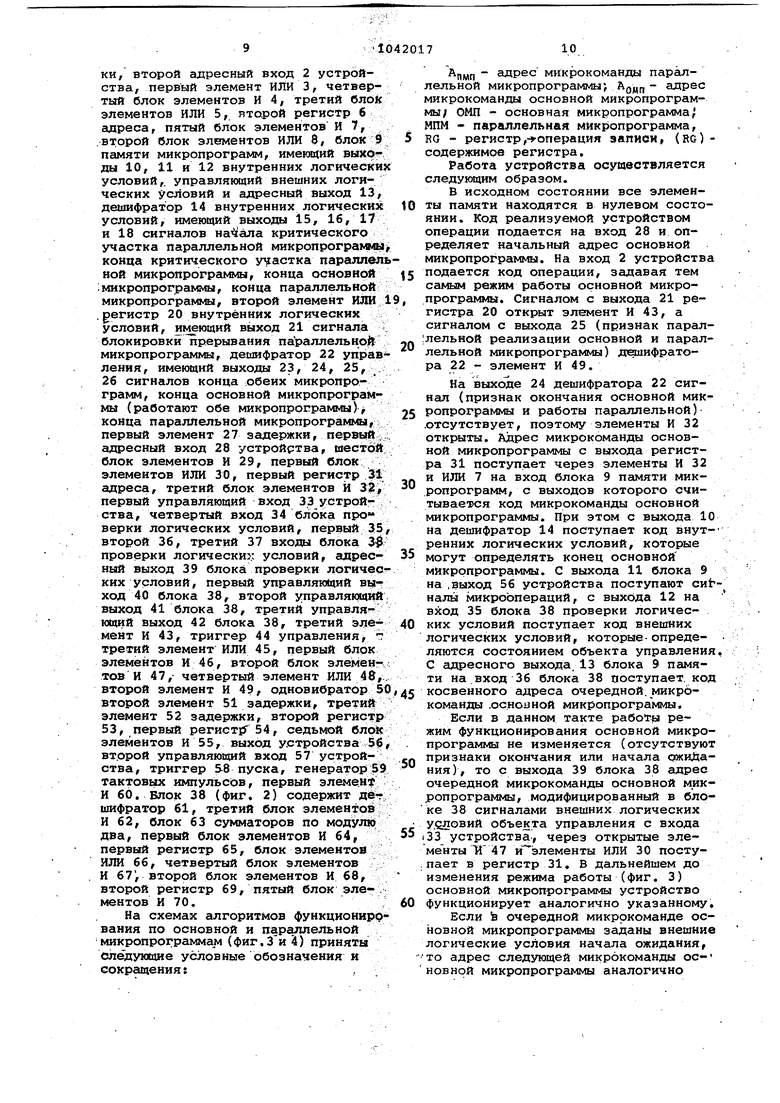

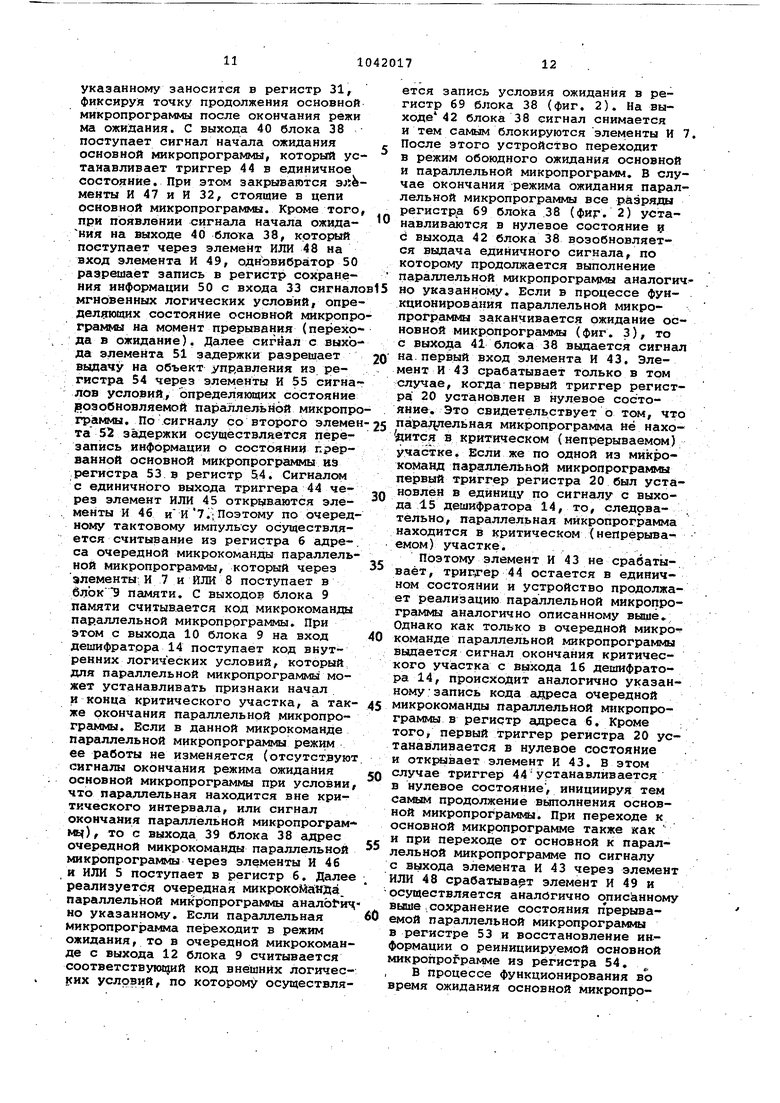

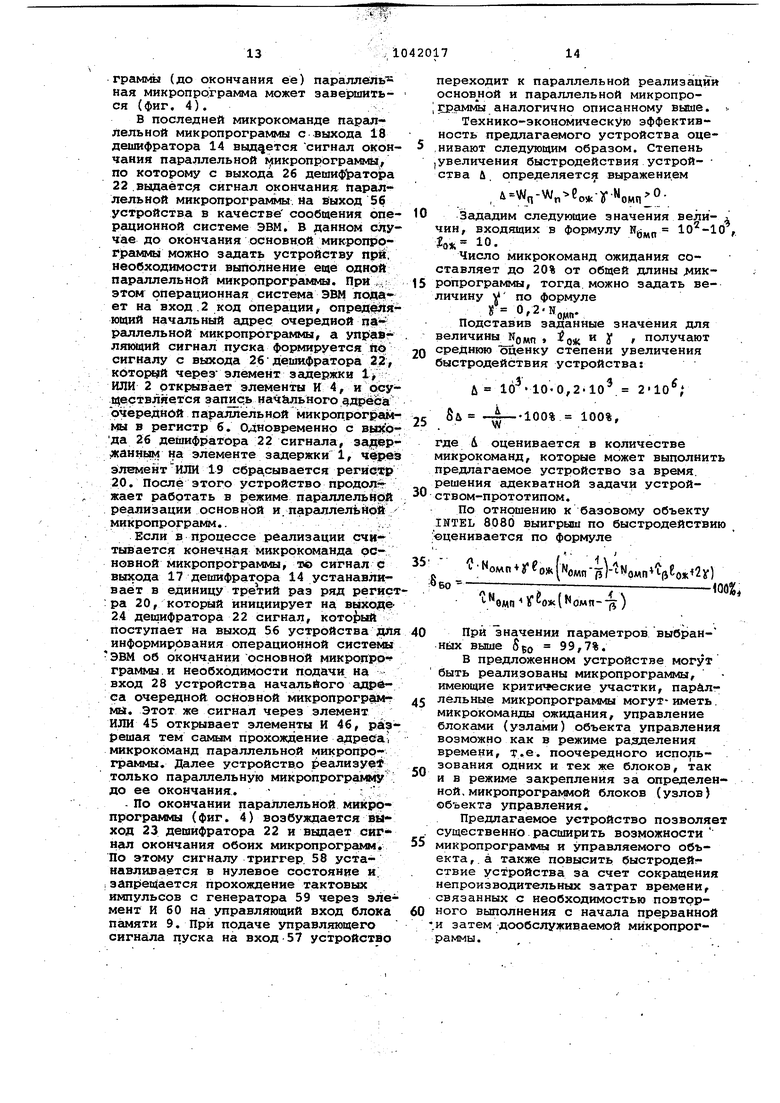

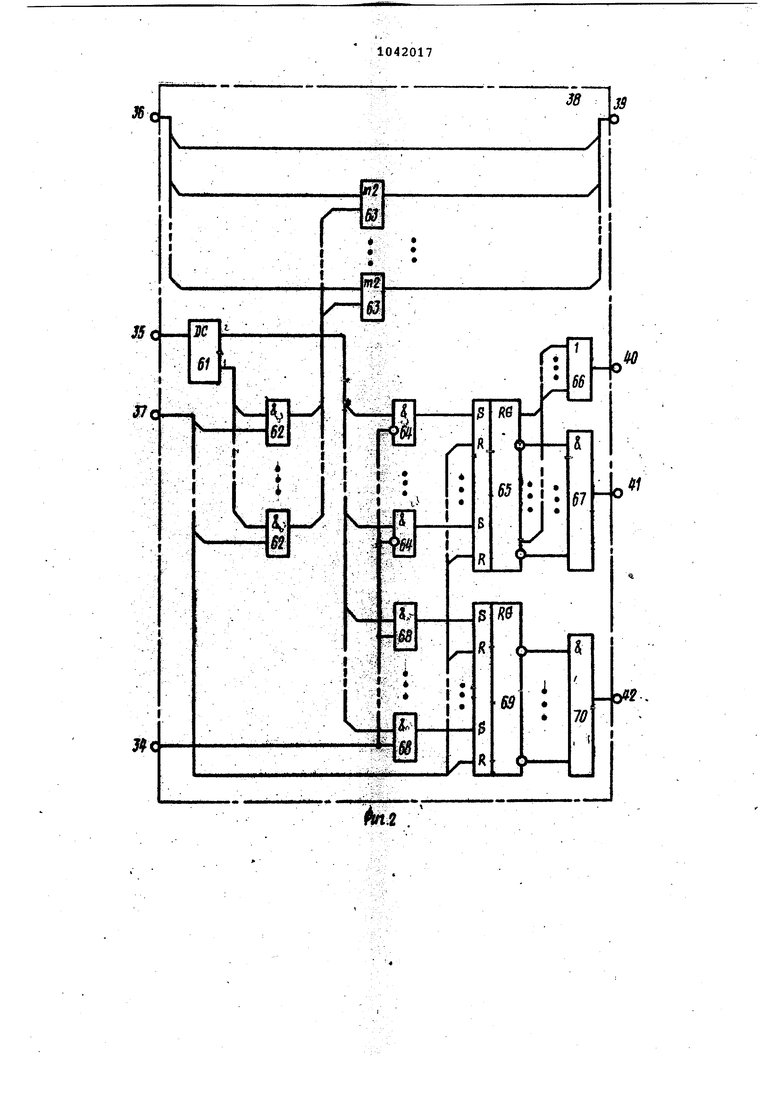

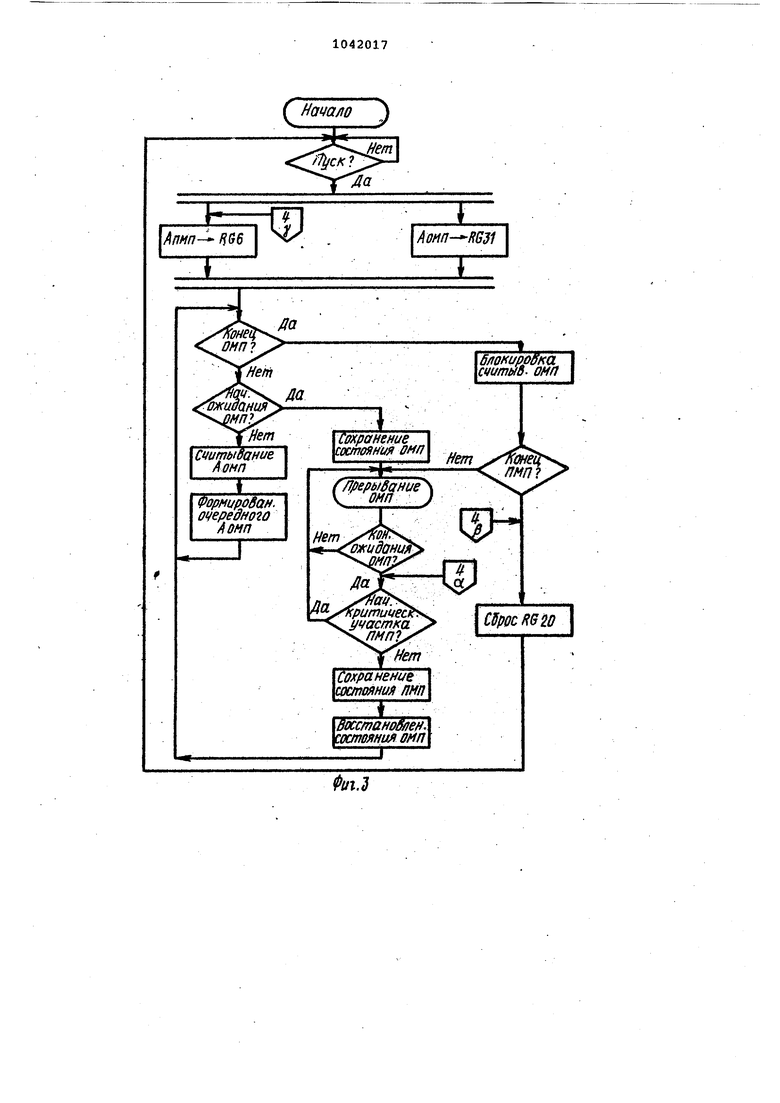

Вторая (параллельная) микропро- грамма не может иметь микрокоманд ожидания ввиду того, что в устройстве по замыслу должен фиксироваться режим ожидания только основной микропрограммы. Однако одни и те же микропрограммы могут выступать в процессе реализации разных операций в системе в роли как основной, так и параллельных микропрограмм. В связи с этим код начала ожидания дол. жен быть унифицированным в системе. Следовательно, при переходе в ожидание параллельной микропрограммы выработан сигнал Начало ожидания, |п15едусмотренный только для основной /микропрограммы, и устройство будет функционировать неверно. Указанный недостаток ограничивает область при менения и снижает надежность ствр., Кроме того,, в прототипе может быт рег(лизован только принцип закрепления функциональных узлов и элементо (или их совокупностей) за конкретной микропрограк1мой (основной или паргшлельной). Данноеопределение соответствует принципу построения вычислительной системьа с закрепленными устройствами. Это обусловлено тем, что состояние системы, содержа щей объект управления и данное устройство управления при переходе от основной микрограммы (параллельно , |1Гпараллельной (основной) сохраняется только частично - запоминается .адрес очередной микрокоманды прерываемой программы. Состояние же объекта управ ления, определяемое значениямилогических условий, не запоминается. По- . этому для. того, чтобы привозобновле. НИИ выполнения прерванной микропрограммы можно было идентифицировать нужное Для ее работы состояние системы требуется, чтобы-прерываемая микропро грамма (которая работала перед возобновляемой) не изм:енила логические условия, определяющие ход выполнения во зобновляемой микропрограммы. Указанное ограничение приводит На практике к резкому увеличению объема оборудования системы либо требует существен ного снижения функциональных возможностей микропрограмм. Низкое быстродействие прототипа также обусловлено тем, что параллельная микрбпрограмма не может иметь микрокоманд ожидания. Вследствие этого исходная микропрограмма должна разбиваться на параллельные микропрограммы меньшего размера, не содержащие микрокоманд ожидания. Цель изобретения - расширение области применения и повышение быстродействия устройства Поставленная цель достигается тем что в мультимикропрограммное устройство управления, содержащее шесть « локов элементов И, элемент ИЛИ, три блока элементов ИЛИ, элемент И, два регистра адреса, блок памяти микропрограмм, блок проверки логических условий, триггер пуска, генератор тактовых импульсов, триггер управления, регистр внутренних логических условий и дешифратор внутренних .логических условий, первый и второй выходы которого подключены соответственно к единичному и нулевому входам первого триггера регистра внутренних логических условий. третий и четвёртый выходы дешифратора внутренних логических условий подч ключены соответственно к единичным входам второго и третьего триггеров . регистра внутренних логических условий, выход внутренних логических ус .ловий блока памяти микропрограмм соединен с входом дешифратора внутрен них логических условий, управляющий вйход блока памяти микропрограмм соединен с выходом устройства, выход внешних логических условий и ;адресныйвыход блока памяти микропрограмм подключены соответственно к- первому и второму входам блока проверки логических условий, третий вход которого соединен с первым управляющим входом устройства, адресный выход блока проверки логических условий соединен с первыми входами первого и .второго блоков элементов И, первый управляющий выход блока проверки логических условий соединен с единичным входом триггера управления, выход которого подключен к второму вxoдV второго блока элементов И, выход которого соединен с нулевым-входом первого блока элементов ИЛИ, выход первого блока элементов ИЛИ подключен к входу первого регистра адреса, выход которого подключен к .первому входу третьего блока элементов И, выход третьего блока элемен тов И соединен с первым входом второго блока элементов ИЛИ, выход которого подключен к адресному входу блока памяти микропрограмм, выход первого элемента ИЛИ соединен с первым входом четвертого блока элементов И, выход которого соединен с первым входом третьего блока элеиен±ов ИЛИ, выход третьего блока элементов ИЛИ подключен к входу второго регистра адреса, выход второго регистра адреса соединен с первым входом пятого блока .элементов И, выход которого соединен с вторым входом второго блока элементов ИЛИ, выход первого блока элемен-грв И со- .( единен с вторым входом третьего элементов ИЛИ, первый адресный вход устройства соединен с первым входом шестого блока элементов И, выход которого подключен к второму первого блока элементов ИЛИ, второй адресный вход устройства подключен к второму входу .четвертого блока элементов И, выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого подключен к управляющему входу блока памяти микропрограмм, второй управляющий вход.устройства соединен с единичным входом TpiHrrepa пуска, единичный выход которого соединен со вторым входом первого элемента И, дополнительно введены седьмой блок элемейтов И, второй, третий и четвертый элементы ИЛИ, два элемента И, четыре элемента задержки, одновнбратор, деиифра.;Тор управления, первый и второй регистры, причем первьлй выход дешифратора управления подключен к нулевому входу триггера пуска и через первый элемент задержки к нулевому входу второго триггера регистра внутренних- логических условий, единичные и нулевые выходы второго-и трётьегЬ триггеров регистра внутренних логических условий соединены со ответственно с первым, вторым, ретъ им и четвертым входами дешифратора управления, .второй выход которого подключен к выходу устройства, первому входу третьего элемента ИЛИ, третьему входу i второго блока элементов И первому входу четвертого элемента ИЛИ и второму входу третьегЪ влрка элементов И, третий выход дешифратора управления подключен к пер вому входу второго элемента И/ вход которого через последовательно соединенные одновибратор, второй и третий элементы задержки соединен с управляющим входом первого регистра, выход одновибратора соединен е управляющим входом второго регистра информационный вход которого подклю чен к первому управляющему входу уст ройства, выход второго регистра подключен к информационному входу первого регистра, выход которого соединен с первым входом седьмого блока элементов И, выход второго элемента задержки, соединен с вторым входом седьмого блока элементов И, выход которого подключен к выходу устр й1ства, четвертый выход дешифратсра управления соединен через четвертой элемент задержки с первым входом первого элемента ИЛИ, второй вход которого соединен с единичным входом триггера пуска и вторым входом шестого блока элементов И, четвертый выход дешифратора управления соедй ней также с выходом устройства, адход четвертого элемента .задержки соединен с вторым входом второго элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера регистра внутренних логических условий, единичный выход триггера упрайления соединен с вторым входом треть его элемента ИЛИ, выход которого под ключен к второму входу пятого блока элементов И, второму входу первого блока элементов И и четвертому входу блока проверки логических уело- ;Вий, второй и третий управляющие входы которого соединены соответственно с первым входом третьего эле «ента И и третьим входом пятого блока элементов И, нулевой выход первого триггера регистра внутренних лот гических условий соединен с вторым. входом третьего элемента И, выход которого соединен с нулевым входом триггера управления и вторлм входом четвертого элемента ИЛИ, третий вход которого подключен к единичному входу триггера управления, выход четвертого элемента ИЛИ соединен с вторым входом второго элемента И, нулевой выход триггера управления соединен b третьим входом третьего блока элементов И. Блок проверки логических условий содержит дешифратор, два регистра, три блока элементов И, €5лок элементов сумма по модулю два, два элемента И и элемент ИЛИ, причем первый выход дешифратора соединен с первыми входами первого и второго блока элементов И, второй вход дешифратора соединен с первым входом треть его блока элементов И, выход которого соединен с первым входом блока элементов сумма по модулю двд, вто рой вход блока элементов сумма по модулю два подключен к второму входу блока проверки логических условий, . а выход - к адресному выходу блока 1рове{}ки логических условий, первый вход блока проверки логических условий соединен с входом дешифратора, третий вход блока проверки логических условий соединен с вторым входом третьего блока элементов И и первыми группами входов первого и второго регистров, вторые группы входов ко- . торых соединены соответственно с выходами первого и второго блоков элементов и, первый выход первого регистра соединен с вхЬдом элемента И, выход которого является первым управ-ляющим выходом блока проверки логических условий, второй управляющий выход которого соединен с выходом первого элемента И, второй выход первого регистра соединен с входами первого элемента И, выход второго регистра соединен с входами вторб1о элемента И, выход которого является третьим управляющим выходом-блока проверки логических условий, чётвертый вход которого соединен с вторялми входами первого и второго блоков элементов И. Сущность изобретения состоит в {Расширении области применения и повышении быстродействия устройства . путем реализации кругового циклического алгоритма для двух микропрограмм. При одна из микропрограмм (основная) имеет приоритет выше, чем у другой (параллельная) и поэтому может прерывать ее выполнение. Устройство предназначено для реализации микропрограмм представляемых в. последовательно-параллельной форме. При этом каждая исходная микропрограмма разбивается на подмножбства основных и параллельных микропрограмм. Устройство функционирует следу кпцим образом. В исходной состоянии все элементы памяти находятся в нулевом состо янии. Код реализуемой операции зап сывается в регистр адреса основной микропрограммы и определяет начальный адрес соотве тствую1цей микропрогреалма. В регистр параллельной микропрограммы заносится начальный ад рес первой параллельной микропрог рг1ммы, которая реализуется в режима Ожидания основной микропрограммы. После этого устройство переходит в режим реализации основной микропрограммы. Направление цепи передачи информации (формирование адреска оче редной ми1 рок6гаанды) определяется состоянием триггера управления, который в режиме реализации основной микропрограммы устанавливается в ну левое состояние. Если основная микропрограмма переходит в режим ожида ния/ то по соответствующему сигналу блока проверки логических условий триггер управления переключается в единичное состояние, тем самым прерывая выполнение основной микропрограммы и разрешая реализацию параллельной .микропрограммы. Кроме того, при прерывании основной микро программы И и аналогично параллельной микропрограммы во втором регист ре сохранения информации запомина-. етсд. состояние логических условий н момент прерывания основной (параллельной) микропрограммы, а из первого регистра сохранения информации восстанавливается состояние логичес ких условий для продолжения реиници миЛ1 опрЬграммы. Ъ процессе выполнения параллельной микропрограммы также может возникнуть режим ожидания (вложение ожиданий). В этом случае соответствующим сигналом блока проверки логи ческих условий блокируется считывание из регистра адреса параллельной микропрограммы до свершения одного из двух событий: окончание режима ожидания параллельной микропрограмМа до завершения ожидания основной микропрограммы, окончание режима ожидания основной микропрограммы. В первом случае разблокируется цепь считывания с регистра параллел ной микропрограммы, и устройство функционирует в режиме выполнения Параллельной микропрограммы аналогично указанйому. Во втором случае происходит запоминание логических условий на момент прерывания параллельной микропрогр 1ммы,- восстанавливаются логи,ческие условия для основной микропрограммы, и устройство переходит в режим выполнения основной микропрограммы. Однако свершение второго собы,тия возможно только в том случае, если параллельная микропрограмма .не воздействует на функциональные элементы и узлы объекта управления, которые она использует в режиме разделения времени-с основной микропрограг дй и операции с которыми должны быть логически завершены, т.е. являются неделимыми или, другими словами, критическими участками параллельной микропрограммы. Для защиты таких критических участков в устройстве блокируется прохождение сигнала окончания ожидания основной микропрограммы до окончания критического участка параллельной микропрограммы. Это позволяет существенно расширить область применения устройства за счет отказа от режима монопольного закрепления функциональных УЗЛОВ и элементов объекта управления за микропрограммой. Если до окончания выполнения основной микропрограммы заканчивается данная параллельная микропрограмма, то соответствующий сигнал выдается операционной системе ЭВМ, которая может занести в регистр параллельной микропрограммы начальный ацрес другой параллельной микропрограммы. Параллельная микропрограмма может выполняться параллельно с данной основной микропрограммой. В противном случае устройство продолжает реализацию текущей основной микропрограммы до ее завершения. Если до окончания выполнения параллельной микропрограммы заканчивается основная микропрограмма, то адрес очередной микропрограммы основной микропрограммы (первой микрокоманды в новой параллельно-последовательной комбинации микропрограмм) записывается в регистр основной микропрограммы и происходит блокирование считывания из регистра основной микропрограммы. По окончании обеих микропрограмм осуществляется запись в регистр параллельной микропрограммы начального адреса очередной параллельной микропрограммы и устройство переходит в режим реализации новой параллельно-последовательной комбинации микропрограмм в соответствии с ука:занным порядком. На фиг. 1 представлена функциональная схема предлагаемого устройства, на фиг. 2 - функциональная схема блока проверки логических условий/ на фиг. 3 - схема алгоритма реализации основной микропрограммы, на фиг. 4 - схема алгоритма реализации параллельной микропрограммы. Предлагаемое устройство (фиг. 1) содержит четвертый элемент 1 задержки, второй адресный вход 2 устройства, первый элемент ИЛИ 3, четвертый блок элементов И 4, третий блок элементов ИЛИ 5, второй регистр 6 адреса, пятый блок элементов И 7, .второй блок элементов ИЛИ 8, блок 9 памяти микропрограмм, имеющий выходы 10, 11 и 12 внутренних логически условий,. управляющий внешних логических условий и адресный выход 13, дешифратор 14 внутренних логических условий, имеющий выходы 15, 16, 17 и 18 сигналов критического участка параллельной микропрограммы конца критического участка параллел ной микропрограммы, конца основной микропрогра1ъо4ы, конца параллельной микропрограммы, второй элемент ИЛИ .регистр 20 внутренних логических условий, имеющий выход 21 сигнала блокировки прерывания параллельнрй микропрограммы, дешифратор 22 управ ления, имеющий выходы 23, 24, 25, 26 сигналов конца обеих микропрограмм, конца основной микропрограммы (работают обе микропрограммы), конца параллельной микропрограммы, первый элемент 27 эадержки, первый, адресный вход 28 устройртва, шестой блок элементов И 29, первый блок элементов ИЛИ 30, первый регистр 31 адреса, третий блок элементов И 32, первый управляющий вход 33 устройства, четвертый вход 34 блока про верки логических условий, первый 35 второй 36, третий 37 входы блока ЗЭ проверки логически.: условий, адресный выход 39 блока проверки логичес ких условий, первый управляющий выход 40 блока 38, второй управляющий выход 41 блока 38, третий управляющий выход 42 блока 38, третий элемент И 43, триггер 44 управления, третий элемент ИЛИ 45, первый блок элементов И 46, второй блок элементов И 47, четвертый элемент ИЛИ 48, второй элемент И 49, одиовибратор 5 второй элемент 51 эадержки, третий элемент 52 задержки, второй регистр 53, первый регистру 54, седьмой блок элементов И 55, выход устройства 56 вт.орой управляющий вход 57 устройства, триггер 58 пуска, генера:тор 59 тактовЕ импульсов, первый элеменф И 60. Блок 38 (фиг, 2) содержит дешифратор 61, третий блок элементов И 62, блок 63 сумматоров по модулю два, первый блок элементов И 64, первый регистр 65, блок элементов ИЛИ 66, четвертый блок элементов И 67, второй блок элементов И 68, второй регистр 69, пятый блок элементов И 70. На схемах алгоритмов функциониро вания по основной и параллельной микропрограммам (фиг.Зи i) приняты «шёдующие условные обозначения и сокращения: пмп адрес микрокоманды параллельной микропрограммы , Аддг адрес микрокоманды основной микропрограммы/ ОМП - основная микропрограмма/ МПМ - параллельная микропрограмма, RG - регистр,- Операция записи, (RG)содержимое регистра. Работа устройства осуществляется следукяцим образом. В исходном состоянии все элементы памяти находятся в нулевом состоянии. Код реализуемой устройством операции подается на вход 28 и определяет начальный адрес основной микропрограммы. На вход 2 устройства подается код операции, задавая тем самым режим работы основной микропрограммы. Сигналом с выхода 21 регистра 20 открыт элемент И 43, а сигналом с выхода 25 (признак парал:лельной реализации основной и параллельной микропрограммы) дешифратора 22 - элемент И 49. На выходе 24 дешифратора 22 сигнал (признак окончания основной микропрограммы и работы параллельной) .отсутствует, поэтому элементы И 32 открыты. Адрес микрокоманды основной микропрограммы с выхода регистра 31 поступает через элементы И 32 и ИЛИ 7 на вход блока 9 памяти микропрограмм, с выходов которого считывается код микрокоманды основной микропрограммы. При этом с выхода 10 на дешифратор 14 поступает код внутренних логических условий, которые могут определять конец основной микропрограммы. С выхода 11 блока 9 на .выход 56 устройства поступают сиЬналы микроопераций, с выхода 12 на вход 35 блока 38 проверки логических условий поступает код внешних логических условий, которыеопреде- ляются состоянием объекта управления, С сшресного выхода 13 блока 9 памяти на вход 36 блока 38 поступает, код косвенного адреса очередной, микрокоманды .основной микропрограммы. Если в данном такте работы режим функционирования основной микропрограммы не изменяется (отсутствуют признаки окончания или начала ожийания), то с выхода 39 блока 38 адрес очередной микрокоманды основной микропрограммы, модифицированный в блоке 38 сигналами внешних логических УСЛОВИЙ объекта управления с входа 33 устройства, через открытые эле менты И47 и элементы ИЛИ 30 поступает в регистр 31. В дальнейшем до изменения режима работы (фиг. 3) основной микропрограммы устройство функционирует аналогично указанному. Если 5в очередной микрокоманде основной микропрограммы заданы внешние логические условия начала ожидания, то адрес следующей микрокоманды основной микропрограммы аналогично

указанному заносится в регистр 31, фиксируй точку продолжения основной микропрограммы после окончания режи ма ожидания. С выхода 40 блока 38 поступает сигнал начала ожидания основной микропрограммы, который устанавливает триггер 44 в единичное состояние. При этом закрываются э;5вменты И 47 и И 32, стоящие в цепи основной микропрограммы. Кроме того, при появлении сигнала начала ожидания на выходе 40 блока 38, который поступает через элемент ИЛИ 48 на вход элемента И 49, однЪвибратор 50 разрешает запись в регистр сохранения информации 50 с входа 33 сигнало мгновенных логических условий, опреяел1Я101цих состояиие основной микропрогранф ы на момент прерывания (перехода в ожидание). Далее сигнал с выхода элемента 51 задержки разрешает выдачу на объект управления из регистра 54 через элементы И 55 сигналов условий, определяющих состояние возобновляемой параллельной микропрограммы. По сигналу со второго элемен та 52 задержки осуществляется перезапись информации о состоянии прерванной основной микропрограммы из регистра 53 регистр 54. Сигналом с единичного выхода триггера 44 через элемент ИЛИ 45 открываются элементы И 46 и И 7.; Поэтому по очередному тактовому импульсу осуществляется считывание из регистра 6 адре-. са очередной микрокоманды параллельной микропрограммы, который через элементы, И 7 и ИЛИ 8 поступает в памяти. С выходов блока 9 памяти считывается код микрокоманды параллельной микропрограммы. При этом с выхода 10 блока 9 на вход дешифратора 14 поступает код внутренних логических условий, который для параллельной микропрограммы может устанавливать признаки начал и конца критического участка, а также окончания параллельной микропрограммы. Если в данной микрокоманде параллельной микропрограммы режим ее работы не изменяется (отсутствуют сигналы окончания режима ожидания основной микропрограммы при условии, что параллельная находится вне критического интервала, или сигнал окончания параллельной микропрограмму), то с выхода 39 блока 38 адрес очередной микрокоманды параллельной микропрограммы через элементы И 46 и ИЛИ 5 поступает в регистр 6. Далее реализуется очередная микрокоманда, параллельной микропрограммы анало и но указанному. Если параллельная микропрограмма переходит в режим ожидания, то в очередной микрокоманде с выхода 12 блока 9 считывается соответствую1дий код внешних логических условий, по которому осуществляется запись условия ожидания в регистр 69 блока 38 (фиг, 2), На выходе 42 блока 38 сигнал снимается и тем самым блокируются элементы И 7 После этого устройство переходит в режим обоюдного ожидания основной и параллельной микропрограмм, В случае окончания режима ожидания параллельной микропрограммы все разряды регистра 69 блока 38 (фиг. 2) устанавливаются в нулевое состояние tf d выхода 42 блока 38 возобновляется выдача единичного сигнала, по которому продолжается выполнение параллельной микропрограммы аналогично указанному. Если в процессе функционирования параллельной микропрограммы заканчивается ожидание основной микропрограммы (фиг, 3), то с выхода 41 блока 38 выдается сигнгш на.первый вход элемента И 43. Элемент И 43 срабатывает только в том случае, когда первый триггер регистра 20 установлен в нулевое состояние. Это свидетельствует о том, что пара.:г ельная микропрограмма не нахояитс S критическом (непрерываемом) участке. Если же по одной из микрокоманд параллельной микропрограммы первый триггер регистра 20 был установлен в единицу по сигналу с выхода 15 дешифратора 14, то, следовательно, параллельная микропрограмма находится в критическом (непрерываемом) участке.

Поэтому элемент И 43 не срабатывает, триггер 44 остается в единичном состоянии и устройство продолжает реализацию параллельной микропрограммы аналогично описанному выше,. Однако как только в очередной микрокоманде параллельной микропрограммы выдается сигнал окончания критического участка с выхода 16 дешифратора 14, происходит аналогично указанному запись кода адреса очередной микрокоманды параллельной микропрограммы в регистр адреса 6, Кроме того/ первый триггер регистра 20 устанавливается в нулевое состояние и открялвает элемент И 43. В этом случае триггер 44устанавливается в нулевое состояние , инициируя тем Самым продолжение выполнения основной микропрограммы. При переходе к основной микропрограмме также как и при переходе от основной к параллельной микропрограмме по сигналу с выхода элемента И 43 через элемент ИЛИ 48 срабатывает элемент И 49 и осуществляется аналогично опис анному выше «сохранение состояния прерываемой параллельной микропрограммы в регистре 53 и восстановление информации о реинициируемой основной микропрограмме из регистра 54,

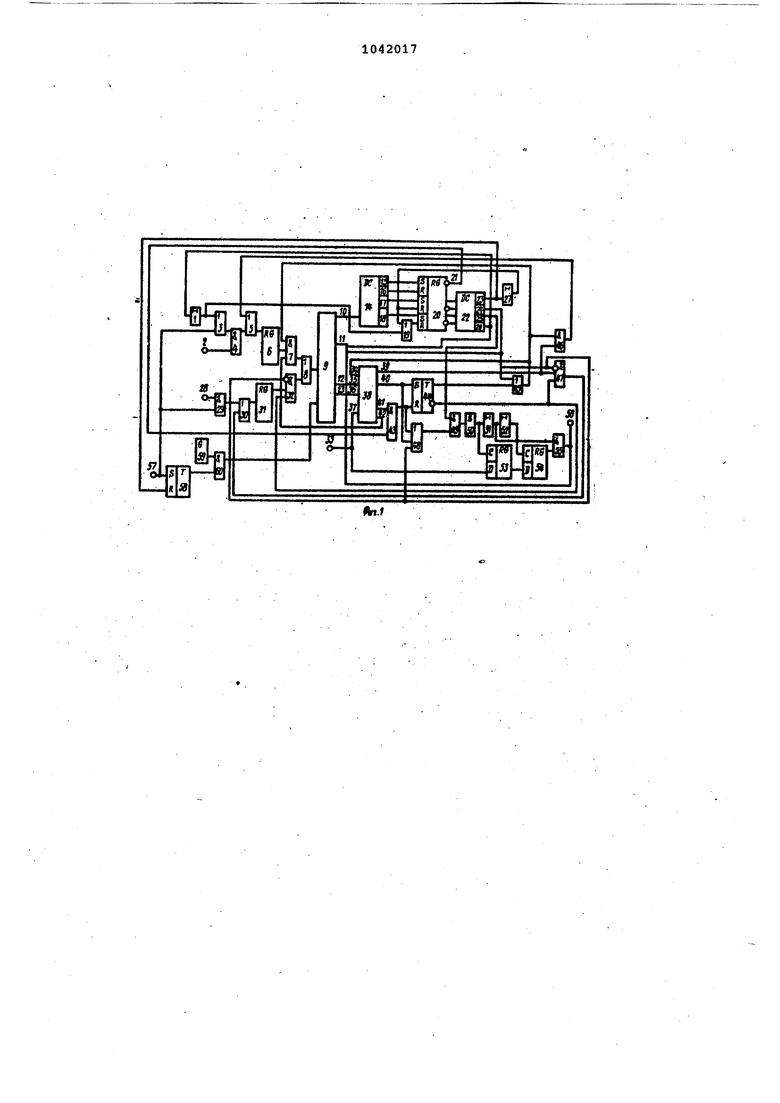

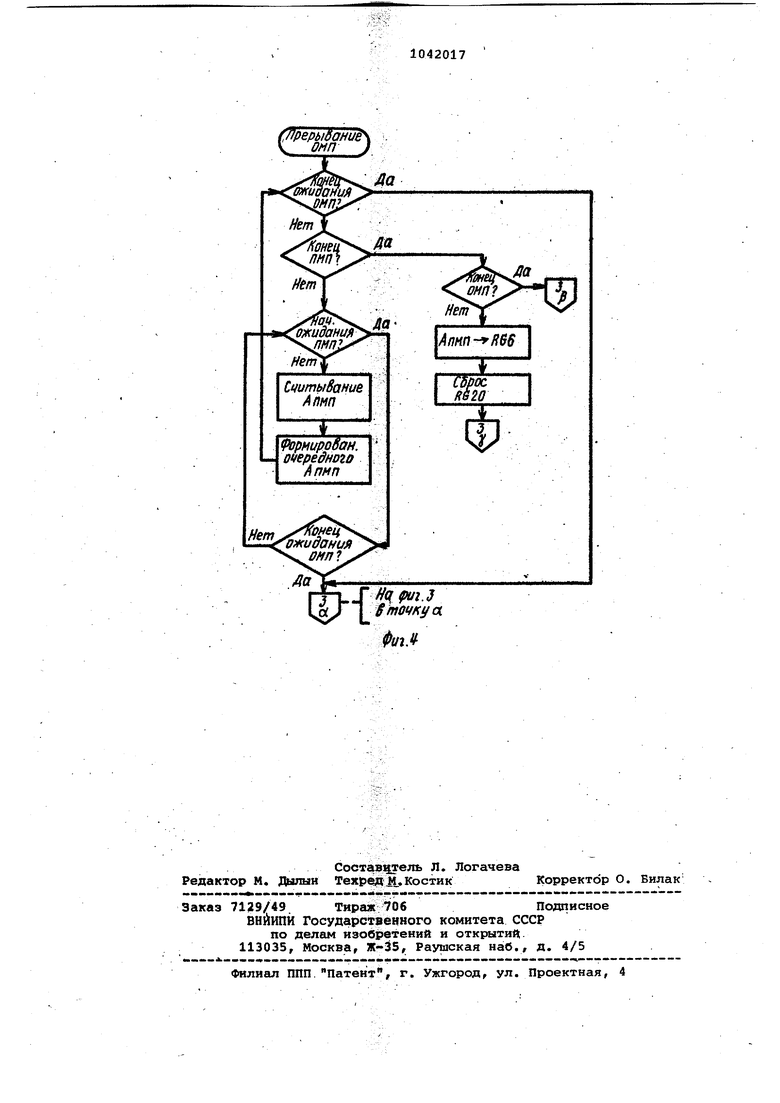

В процессе функционирования во время ожидания основной микропрограммы (до окончания ее) параллель ная микропрограмма может завершиться (фиг. 4)..

В последней микрокоманде параллельной микропрограммы с выхода 18 дешифратора 14 выдается сигнал окончания параллельной Микропрограммы, по которому с выхода 26 дешиф ато ра 22 .выдаётся сигнал окончания параллельной микропрограммы.Ма ёыход 56 устройства в качестве сообщения операционной системе ЭВМ. В данном случае до окончания основной микропрограммы можно задать устройству при, необходимости выполнение еще одной параллельной микропрогрг1ммы. При,.: этом операционная система ЭВМ подает на вход.2 код операции, опреД|ф31я:ющий начсшьный адрес очередной паЦ раллельной микропрограммы, а лякхций сигнал пуска формируется сигналу с выхода 26 д ешифратора 22, кбторь й черезэлемент згшержки t ИЛИ 2 открывает элементы И 4, и осуи ествляется начального адреса очередной параллельной микроп.рограммы в регистр б. Одновременно с вшсода 26 де аифратора 22 сигнсша, за,| ер {аннв1м на элементе задержки 1, элемент ИЛИ 19 с6ра,сывается регистр 20. После этого устройство продолг-г жает работать в режиме паргшлельнрй реализации основной и.параллельйойх микропрограмм..

Если в процессе реализации счи тывается конечная Микрокоманда основной микропрограммы, те сигнал с выхода 17 дешифратора 14 устанавливает в единицу третий раз ряд регист:ра 20, который инициирует на выходе24 дешифратора 22 сигнал, который поступает на выход 56 устройства дйя информирования операционной системы ЭВМ об окончании основной микропро граммы.и необходимости подачи, на вход 28 устройства начальйого адреса очередной основной микропрогрдмг мы. Этот же сигнал через элемент ИЛИ 45 открывает элементы И 46, рдэ решая тем самым прохождение адреса: микрокоманд параллельной микропрограммы. Далее устройство )еализуе только параллельную микропрограмму . до ее окончания. . : ,

. По окончании параллельиой микропрограммы (фиг. 4) возбуждается 23 дешифратора 22 и выдает сиг нал окончания обоих микропрограмм. По этому сигналу триггер. 58 устанавливается в нулевое состояние и. ;запрещается прохождение тактовых импульсов с генератора 59 через элемент И 60 на управляющий вход блока памяти 9. При подаче управляющего сигнала пуска на вход 57 устройство

переходит к параллельной реализации основ ной и параллельной микропрограмглл аналогично описанному выше, v

Технико-экономическую эффективность предлагаемого устройства оце.нивают следующим образом. Степень ,увеличения быстродействия устрой- ства Л определяется выражени.ем

л м„- м„ ео -уЛип °Зададим следующие значения вели- д чин, входящих в формулу 10-10 ,

o 10.

Число микрокоманд ожидания составляет до 20% от общей длины 1икропрограммы, тогда можно задать величину по формуле

0.2..

Подставив заданные значения для величины Nflinf, , f Q и у , получают среднюю оценку степени увеличения быстродействия устройства:

U 1б 100,2.10. 100% 100%,

25

где Л оценивается в количестве микрокоманд, которые может выполнить предлагаемое устройство за время, решения адекватной задачи устрой30ством-прототипом.

По отношению к базовому объекту INTEL 8080 выигрыш по быстродействию оценивается по формуле

5 - NoMn + jrea(NoMn-y-fNo«n 3 2y)

;обо-----100

г%пЧ ок(Иомп-)

40 При значении параметров выбранНих выше 5бо 99,7%.

В предложенном устройстве могут быть регшизованы микропрограммы, имеющие критические участки, парАлг

45 лельные микропрограммы могут- иметь. микрокоманды ожидания, управление блоками (узлами) объекта управления возможно как в режиме радделения времени, т.е. поочередного испо ьзования одних и тех же блоков, так

50

и в режиме закрепления за определенной, микропрогргиимой блоков (узлов) объекта управления.

Предлагаемое устройство позволяет . существенно расширить возможности 55 MHKponporpaMNHj и управляемого объекта ,. а также повысить быстродей;ствие устройства за счет сокращения непроизводительных затрат времени, связанных с необходимостью повторного выполнения с начала прерванной .и затем дообслуживаемой микропрограммы. , .

(Начало

ffipepbi6OHUe L омп j

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1979 |

|

SU857995A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1043651A1 |

| Мультимикропрограммное устройство управления | 1981 |

|

SU959079A1 |

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ | 1979 |

|

SU842813A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1976 |

|

SU643874A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-15—Публикация

1982-04-09—Подача