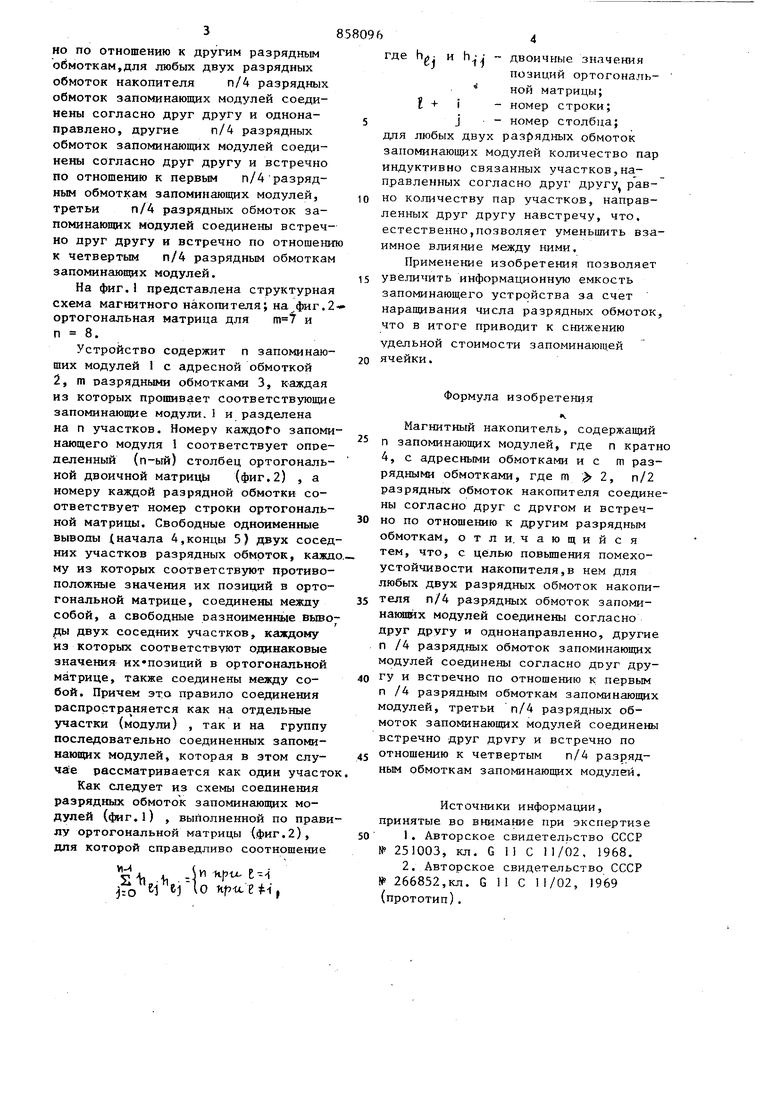

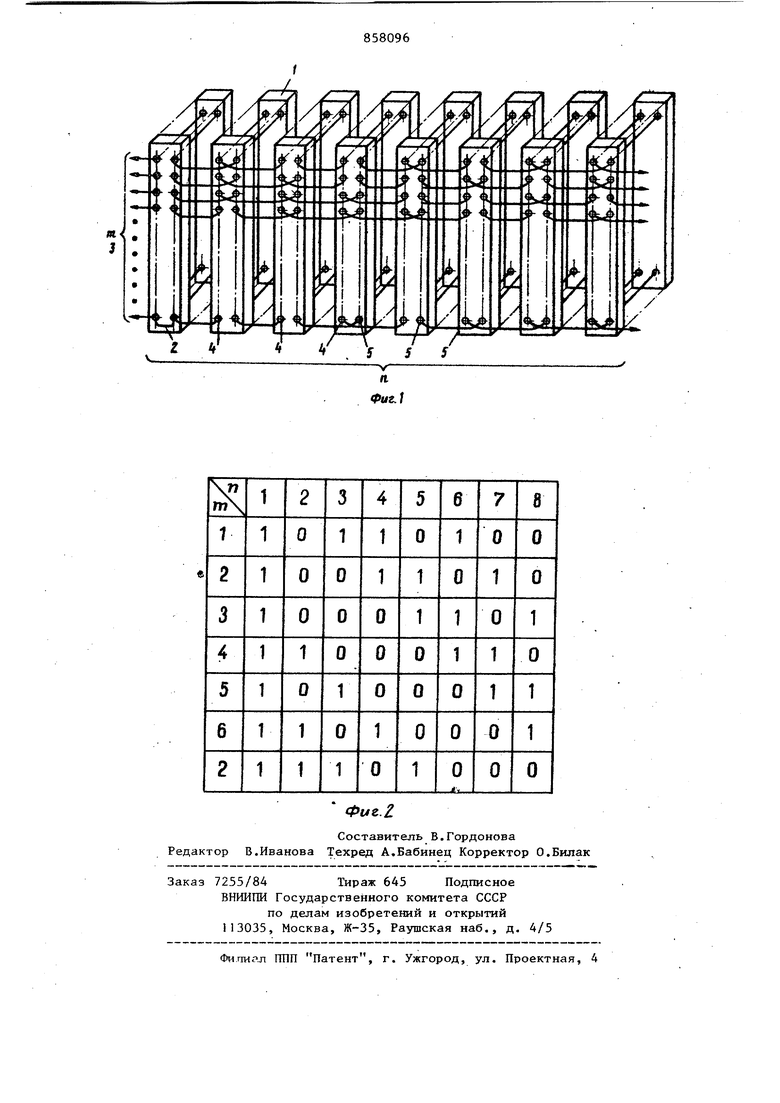

Изобретение относится к вычислительной технике, в частности к устрой ствам хранения дискретной информации и может быть использовано при проек тировании магнитных оперативных запомингиощих устройств на интегральных магнмт1о гх носителях информации. Известны магнитные накопитегш,выполненш 1е на многоотверстных ферритовых пластинах, состоящие из кассет, образующих модули, в середине каждой из которых размещена коммутационная плата, к выводам которой присоединены концы разрядных обмоток П 1. Однако данное устройство уменьшае взаимное влияние только двух рядом расположенных обмоток, но не обеспечивает устранения взаимного В1гаяния обмоток, расположенных в различных Группах, т.е. не обладает высокой помехоустойчивостью. Наиболее близким к предлагаемому является мягнитный накопитель, содержащий И- модулей магнитных запоми- нающих элементов с адресными обмотками и с группами последовательно соединенных разрядных обмоток, в каждой из которых п/2 разрядных обмоток соединены согласно друг с другом и встречно по отношению к другим п/2 разрядньи обмоткамt2J. Данное техническое решение позволяет уменьшить взаимное влияние четырех разрядных обмоток, принадлежащих к одной группе, но не устраняете взаимного влияния разрядных обмоток, принадлежащих к различным группам, что снижает помехоустойчивость устройства. Цель изобретения - повышение помехоустойчивости магнитного накопителя. Поставленная цель достиается тем, что в магнитном накопителе, содержащем И запоминающих модулей,где и кратно 4, с адресными обмотками и с И1 разрядными обмотками, где , И/2 разрядных обмоток накопителя соединены согласно друг с другом и встречНО ПО отношению к другим разрядным обмоткам,для любых двух разрядных обмоток накопителя п/4 разрядных обмоток запоминающих модулей соединены согласно друг другу и однонаправлено, другие п/4 разрядных обмоток запоминающих модулей соединены согласно друг другу и встречно по отношению к первым п/4 разрядным обмоткам запоминающих модулей, третьи п/4 разрядных обмоток запоминающих модулей соединены встречно друг другу и встречно по отношени к четвертьм п/4 разрядным обмоткам запоминающих модулей. На фиг.} представлена структурная схема магнитного накопителя; .2 ортогональная матрица для и п 8. Устройство содержит п запоминающих модулей I с адресной обмоткой 2, m разрядными обмотками 3, каждая из которых прошивает соответствующи запоминающие модули. 1 и разделена на п участков. Номеру каждого запоми нающего модуля 1 соответствует опре деленный (п-ый) столбец ортогональ ной двоичной матрицы (фиг,2) , а номеру каждой разрядной обмотки соответствует номер строки ортогональ ной матрицы. Свободные одноименные выводы tначала 4,концы 5) двух сосе них участков разрядных обмоток, каик му из которых соответствуют противо положные значения их позиций в орто гональной матрице, соединены между собой, а свободные разноименшле выв ды двух соседних участков, кахр,ому из которых соответствуют одинаковые значения ихпозиций в ортогональной матрице, также соединены между собой. Причем это правило соединения распростра няется как на отдельные участки (модули) , так и на группу последовательно соединенных запоминающих модулей, которая в этом случае рассматривается как один участ Как следует из схемы соединения разрядных обмоток запоминающих модулей (фяг.1) , выполненной по прав лу ортогональной матрицы (фиг.2), для которой справедливо соотношение Y лсри- E-i Sll 1i, 1 lo Hf7-tce i, jrO J J двоичные значения позиций ортогональ- ной матрицы; Е + i - номер строки; j - номер столбца; для любых двух разрядных обмоток запоминающих модулей количество пар индуктивно связанных участков,направленных согласно друг другу, равно количеству пар участков, направленных друг другу навстречу, что, естественно,позволяет уменьшить взаимное влияние между ними. Применение изобретения позволяет уве.пичить информационную емкость запоминающего устройства за счет наращивания числа разрядных обмоток, что в итоге приводит к снижению удельной стоимости запоминающей ячейки. Формула изобретения Магнитный накопитель, содержащий п запоминающих модулей, где п кратно 4, с адресными обмотками и с m разрядными обмотками, где m 2, п/2 разрядных обмоток накопителя соединены согласно друг с другом и встречно по отношению к другим разрядным обмоткам, отл и. чающийся тем, что, с целью повьш1ения помехоустойчивости накопителя,в нем для любых двух разрядных обмоток накопителя п/4 разрядных обмоток запоминакшщх модулей соединены согласно друг другу и однонаправленно, другие п /4 разрядных обмоток запоминающих модулей соединены согласно доуг другу и встречно по отношению к первым п /4 разрядным обмоткам запоминающих модулей, третьи п/4 разрядных обмоток запоминающих модулей соединены встречно друг другу и встречно по отнощению к четвертым п/4 разрядным обмоткам запоминающих модулей. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 251003, кл. G II С 11/02, 1968. 2.Авторское свидетепьство СССР № 266852,кл. G 11 С 11/02, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для блоков памяти на ферритовых сердечниках | 1988 |

|

SU1608744A1 |

| Запоминающий модуль | 1976 |

|

SU739648A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Устройство для контроля двухпроводных запоминающих матриц | 1978 |

|

SU752503A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Способ изготовления запоминающих матриц на цилиндрических магнитных пленках | 1983 |

|

SU1088069A1 |

| Запоминающий модуль | 1978 |

|

SU796906A1 |

| Запоминающее устройство | 1987 |

|

SU1532976A1 |

| Способ изготовления запоминающих матриц на цилиндрических магнитных пленках | 1981 |

|

SU1016831A1 |

Авторы

Даты

1981-08-23—Публикация

1977-11-21—Подача