i

Изобретение относится к области ав. тома тики и вычислительной техники, в частнос-пг к запсзминаюпшм устройствам, построеиным на базе интегральных элементов памяти.

; Известны интегральные элементы памяти, выполненные на тиристорах с питанием от трехфазной сети пера(енного напряжения с нулевой точкой .

Недостатки известных эп&лентав - потребление энергии в интервале времени между сбросом и записью и { ормашш, синхрон1Бза1Шя входного сигнала с питанием тир.нстора записи и неоднозначность состояния при первоначальном включении, что требует специального устройства для установки элемента в исходное состояние, и пр1шодит к усложнению элемента памяти.

Наиболее близким к предлагаемому $шляется интегральный элетлент памяти, содержащий тиристор записи, первый анод которого соединен через первый диод с шиной нулевого потенциала, первая база последовательно включенные второй дяод в резистор с первой шиной питания, вторая база соедвкена последовательно включенные второй резистор и первую группу диодов с шиной зашюи, а через третий резистор - с шиной нулевого потенинала, к через третий диод подключен эмиттер первого транзистора, коллектор которого соединен через четвертый резистор со второй шиной

10 питания, база пе{жого транзистора подкпк чена через пятый и шестой резисторы ко второй шине питания, тиристор сброса, анод которого подключен через седьмой резистор к третьей шине питания, через

15 четвертый диод - к первому аноду ттфистора записи и через пятый диод - к шине нулевого потенциала, катод-к шине потенциала, первая база тиризтс а сброса соединена через последовательно

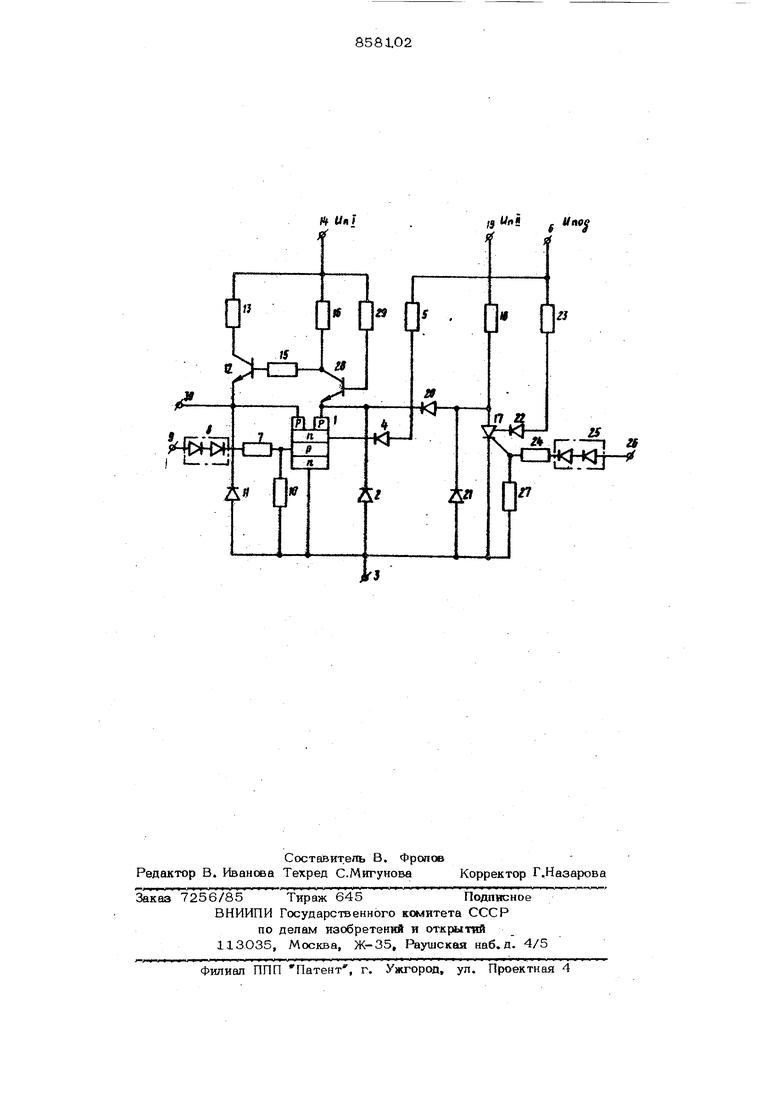

20 включенные шестой диод и восьмой резистор с первой шиной питания, вторая база соединена через последовательно включенные девятый резистор и вторую группу диоде с шиной сброса, а черео десятый резистор с шшюй нулевого потенциала 2 , Недосгагок известного {гнтвгральногс элемента памяти заключается в недостаточной устойчивости к помехам, наведенным на его выходе и в значительнся потреблении мощности. Цепь изобретения - повышение помехоустойчивости и уменьшение мощности потребляау1ой элгалентом памяти. Поставленная цепь достигается тем, что интеграпьный элемент памяти содеркжит второй транзистор и одиннадцатый резистсф, причем второй анод тиристора записи подключен к эмиттеру первого транзистора, первый анод его подключен к эмиттеру второго транзистора, коллектор которого подключен к шестс у резистору, а база - через одиннадцать1й резистор соединена со второй шиной питания На чертеже представлена принципиальная схема предложенного интегрального элемента памяти. Скема содержит тиристор 1 записи, первый анод которого через диод 2 со. единен с шиной 3 потенциала, первая база его через последовательно включенные диод 4 и первый резистор 5 соединена с первой шиной 6 питания, вторая база - через последсеательно вклк ченные второй резистор 7 и первую группу 8 диодов с шиной 9 записи, а через третий резистор 10 - с шиной 3 нулевого потенциала, к которой через диод 11 под ключен эмиттер транз1к:тора 12, коллектор которого соединен через че-гвертый резистор 13 со второй шиной 14 гштания, база транзистора 12 подключена через пятый 15 и шестой 16 резисторяы ко второй шине 14 питания, тиристор 17 сброса, анод которого подключен через седьмой 18 к третьей шине 19 питания, через диод 20 - к первсаду анод тиристора 1 записи и через диод 21 - к шине 3, первая база тиристора 17 сброса через Последовательно включенные диод 22 и восьмой резистор 23 соединен с шиной 6 питания, вторая база - через последовательно включенные девятый рези стор 24 и вторую группу 25 диодов с шиной 26 сброса и через десятый резистор 27 с шиной 3, а также содержит второй транзистор 28, база которого через одиннадцатый резистор 29 соединена с шиной 14. При включении напряжения питания и отсутствии входных сигналов тиристор 1 записи и тиристор 17 сброса включены. а транзистор 12 открыт токсы, протекащим по цепш шина 14-переход база миттер транзистора 12 - внешняя нагрузка элемента памяти. При этом обеспечивается малое выходное сопротивление элемента памяти в выключенном сосгояюш И повышается коэффициент разветвленноети памяти. Указанное подключение элемента памяти к шинам ;14 и 19 источника импульсных трапецеидальных взаимно перекрывающихся напряжений обеспечивает приложение к правому аноду тиристора 1 записи пг ложительного постоянного напряжения в течение всего периода питающего напряжения L/fi J , в то время как к аноду тиристора 17 сброса приложено только импульсное трапецеидальное напряженке , т.е. в каждом периоде напря- женил Un имеется интервал времени, когда оно было равно нулю В интервале времени, когда напряжение питания t/n-j равно нулю, а напряжение U ц II - номинальному значению и в элемент памяти не занесена информация, транзистор 28 пропятстеует протеканию тока по цепи: Ln ц - редистор 18-диод 2О-резистор 16- Un j , в результате чего в интервале времени между сбросом и записью информации элемент не потребляет мощности. Устойчивость тиристора 1 записи к самопроизвольным включениям из-за эффекта -§- в выключенном состоянии обеспеч ивается подачей на п базу этого тиристора через резистор 5 и диод 4 в проводящем направлении постоянного напряжения для предварительного заряда емкости центрального перехода, Так как защита тиристора 1 эффективна только i под . г-дсУпо амплитудное значение напряжен);ш помехи, гтоА напряжение подпора, то устой4imocTb двуханодного тиристора к этим включениям полностью обеспечивается диодами 11 и 2, которые ограничивают величины (Uf Uп( ) на уровне 7-7,5 В. что меньшз УПОД . Аналогично обеспечивается устойчивость тиристора 17 сброса. На его и - базу через резистор 23 и диод 22 в прс одящем состоянии подано постоянное напряжение подпора, а ограничение напряжения на его аноде осуществляет диод 21. При подаче постоянного или импульсного положительного напряжения на шину 9 записи (вход) элемента памяти тиристор 1 записи включается и остается в этом состоянии после снятия информационного сигнала, так как протекающий по налу ток больше тока удержания тиристора записи в течение всего периода питаюшего напр-яжения U . В интервал . времени, когда Uf, имеет положитепьнов значение, транзистор 28 открыт токам, протекающим-по цепи: Опт Р зистор 29 - переход база - эмиттер транзистора 28 - включенный тиристор 1 и находится в режиме насыщения. Выходной транзистор 12 при этсж закрыт.

Для возврата элемента памяти в предыдущее состояние подают положительное напряжение на шину 26 сброса. При положительном напряжении Uf, „ тиристор 17 сброса включается, в результате чего напряжение Un „ не подается на правый анод тиристора 1 и последний в образовавшейся паузе его напряжения питания выключается. После снятия сигнала сброса тщзистора 17 также выключав гея.

Для увеличения устойчивости к помехам, наведенным на выходе элемента памяти, которые выключают включенный тиристор I записи, между базой выходкого транзистора 12 и коллектором транзистора 28 включен резистор 15. Помеха на выходе элемента ограничивается диодом 11 до величины 0,7-О,9 В и включенный тиристор не Быключчтся8 так как Б этом случае по цепи резистор 15 -переход база-эмиттер транзистора 12 будет протекать не весь ток тиристора 1 записи, а лишь его часть, а протекакнций через него ток имеет вел чину, достаточную для его удержания во включенном состоянии.

Напряжение на выходе 30 элемента памяти под действием помехи на его выходе положительной по отношению к катоду тиристора 1 записи, увеличивается в меньшей степени, чем в известном элементе так как в элементе памяти ток помехи замыкается по цепиг выход 30 - левая половина тиристора 1 записи - шина 3 нулевого потенциала.

Уменьшение напряжения на выходе до 0,9-1,0 В позволяет уменьшить Un и Un,, и при коэффициенте разветвленности к 7/и потребляемая ;стность уменьшает ся на 15%.

Формула изобретения

Интегральный элемент памяти, содержаний тиристор записи, первый анод которого соединен через первый диод с шин нулевого потенциала, первая база - чере последовательно включенные второй диод и пер«ый резистор с первой шиной питани вторая база соединена через последовательно включенные второй резистор и первую группу диодов с шиной записи, а через третий резистор - с шиной нулевого потенциала, к которой через третий диод подключен эмиттер первого транзистора, коллектор которого соединен через четвертый резистор со второй шиной п тания, база первого транзистора подклк чена через пятый и шестой резисторы ко второй шине питания, тиристор сброса, анод которого подключен через седьмой резжтор к третьей шине питания, через четвертый диод - к первому аноду тр стора записи и через пятый диод - к шине нулевого потенциала, катод-к шине потенциала, первая база тиристо ра сброса соединена через последовательно включенные шестой диод и восьмой резистор с первой шиной питания, вторая база соединена через последовательно включенные девятый резистор к вторую группу диодов с шиной сброса, а через десятый резистор - с шиной нулазого потенциала, отличающийся тем, что, с целью аовыш,ения помехоустойчивости и уменьшения мощности, потребляемой элементом Пимятн, он содержит второй транзистор и одиннадцатый резистор, причем второй анод тиристора записи подключен к эмиттеру первого транзистора, первый анод его подключен к эмиттеру второго транзистора, коллектор которого подключен к шестому резистору, а база - через одиннадцатый резистор соединена со второй шиной питания.

Источники информахши, принятые во при экспертизе1.Металлургия, № 3, 1974, с. 169-174.

2.Авторское свидетельство СССР.

№ 4434О9, кл. Q 11 С 11/34, 1974 (прототип). У 4flS g I

| название | год | авторы | номер документа |

|---|---|---|---|

| Тиристорный логический элемент ИЛИ-НЕ | 1975 |

|

SU546247A1 |

| Устройство для индикации | 1974 |

|

SU546913A1 |

| Распределительное устройство | 1982 |

|

SU1083233A1 |

| Тлэс-ттл преобразователь | 1977 |

|

SU617844A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Симметричный тиросторный элемент памяти | 1976 |

|

SU652613A2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Формирователь импульсов сброса | 1980 |

|

SU884113A1 |

Авторы

Даты

1981-08-23—Публикация

1977-03-28—Подача