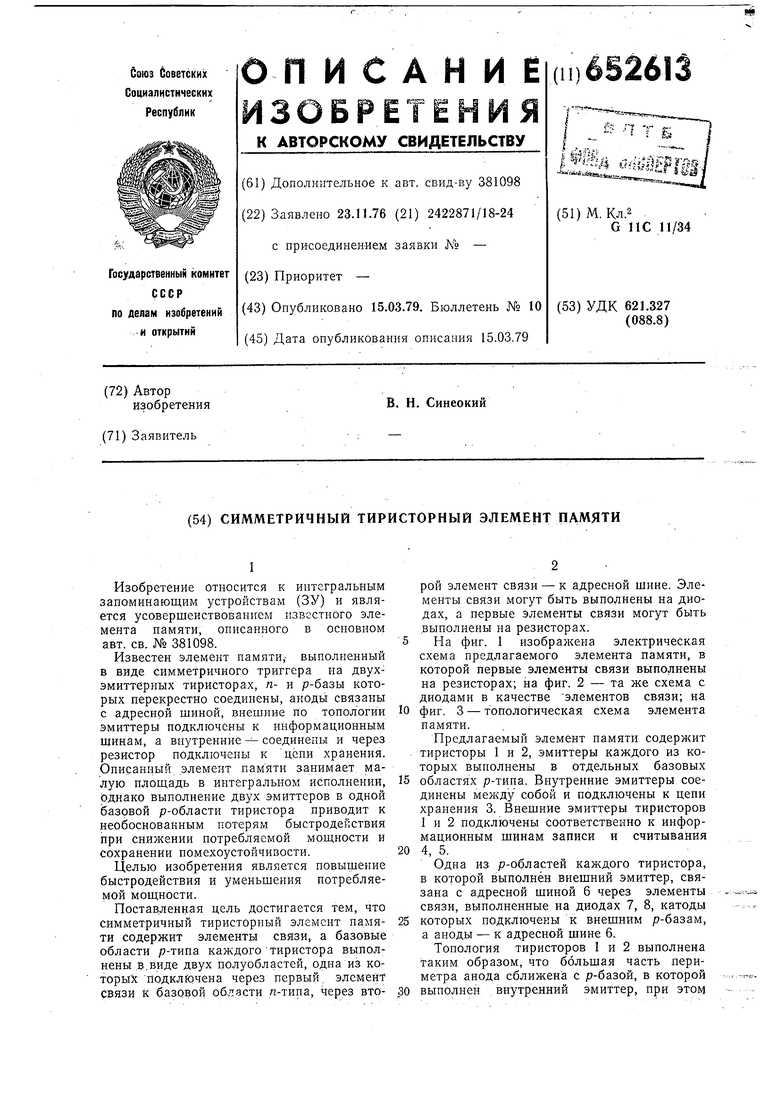

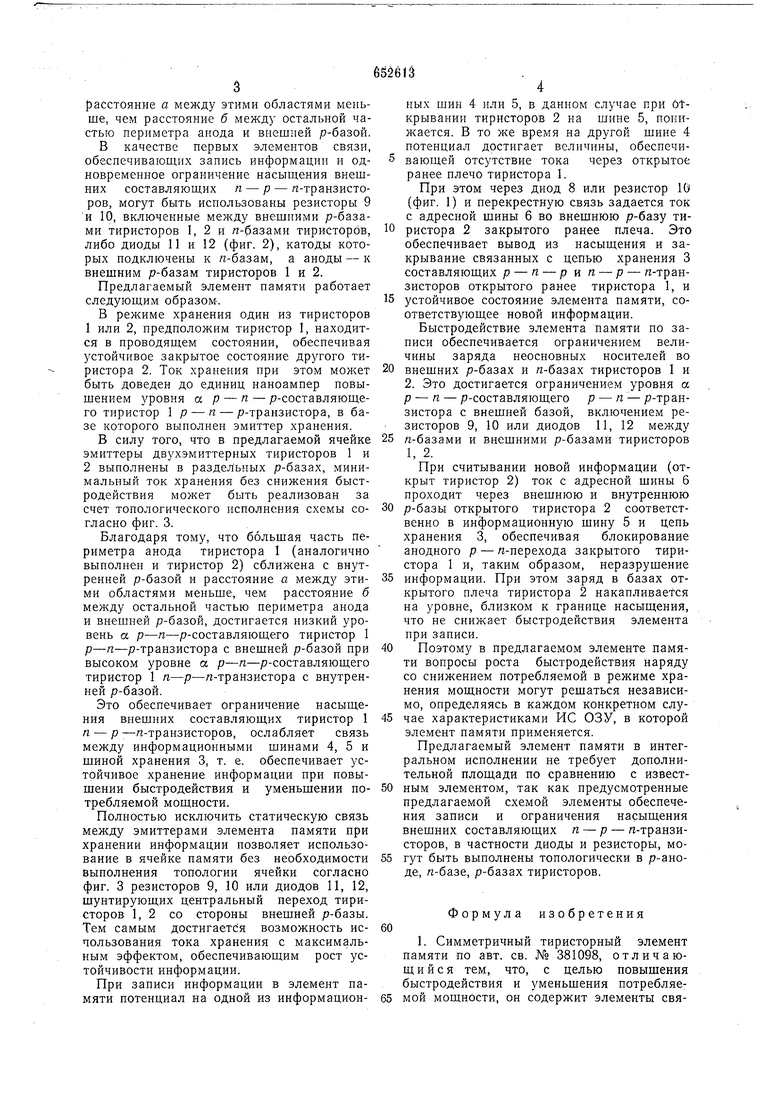

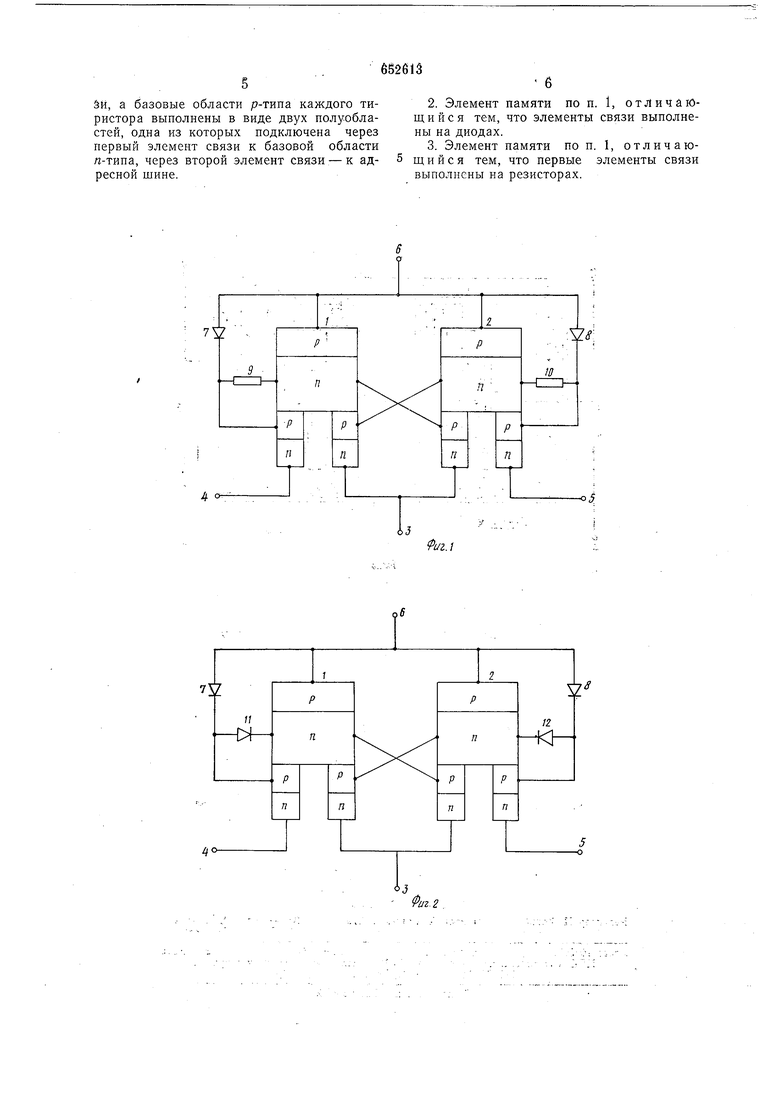

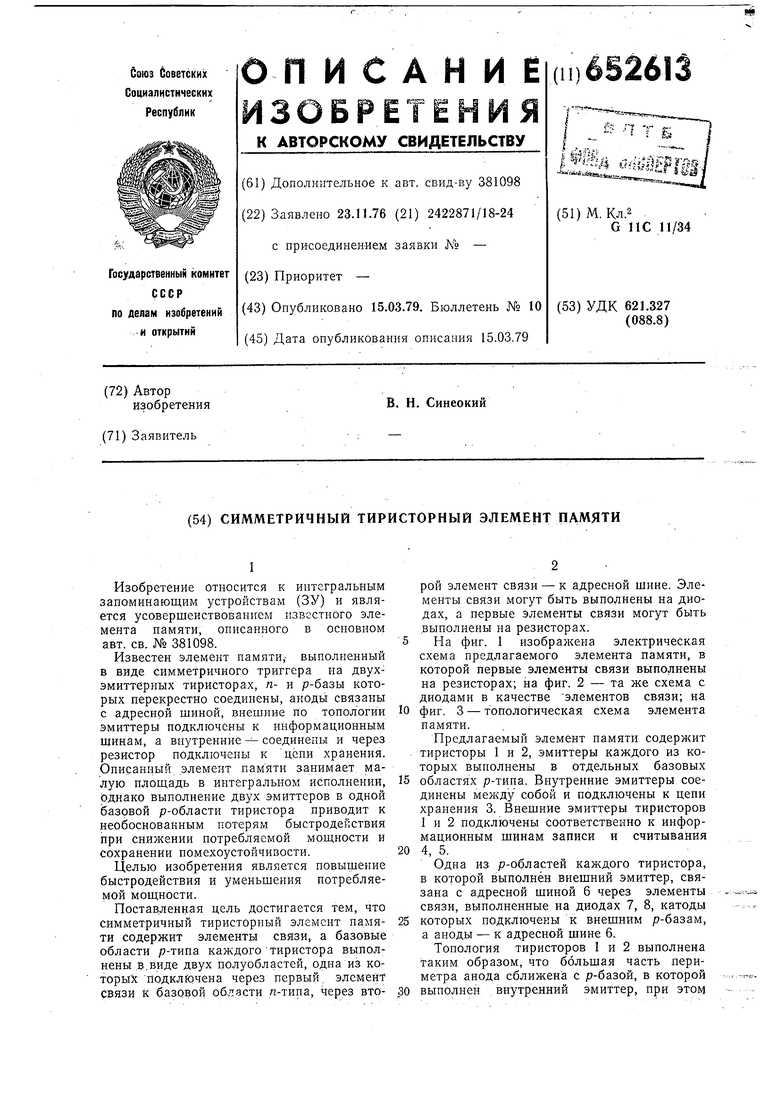

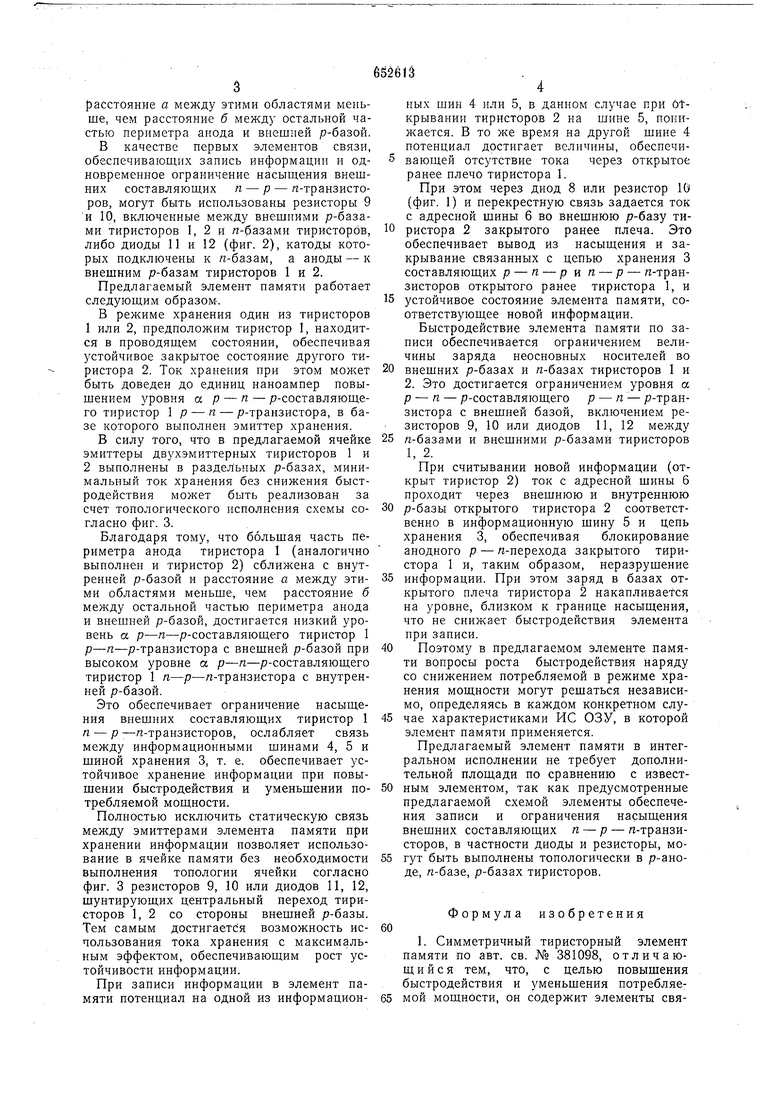

расстояние а между этими областями меньше, чем расстояние б между остальной частью периметра анода и внешней р-базой. В качестве первых элементов связи, обеспечиваюших запись информации и одновременное ограничение насыщения внешних составляюш.их п - р - п-транзисторов, могут быть иснользованы резисторы 9 и 10, включенные между внешними р-базами тиристоров 1, 2 и л-базами тиристоров, либо диоды 11 и 12 (фиг. 2), катоды которых подключены к л-базам, а аноды - к внешним р-базам тиристоров 1 и 2. Предлагаемый элемент памяти работает следующим образом-. В режиме хранения один из тиристоров 1или 2, предположим тиристор 1, находится в нроводящем состоянии, обеспечивая устойчивое закрытое состояние другого тиристора 2. Ток хранения при этом может быть доведен до единиц наноампер повышением уровня а р - п - р-составляющего тиристор 1 р - п - р-транзистора, в базе которого вынолнен эмиттер хранения. В силу того, что в предлагаемой ячейке эмиттеры двухэмиттерных тиристоров 1 и 2выполнены в раздельных р-базах, минимальный ток хранения без снижения быстродействия может быть реализован за счет топологического исполнения схемы согласно фиг. 3. Благодаря тому, что большая часть периметра анода тиристора 1 (аналогично выполнен и тиристор 2) сближена с внутренней р-базой и расстояние а между этими областями меньше, чем расстояние б остальной частью периметра анода и внешней р-базой, достигается низкий уровень ее р-л-р-составляющего тиристор 1 р-л-р-транзистора с внешней р-базой при высоком уровне а р-п-р-составляюшего тиристор 1 л-р-л-транзистора с внутренней р-базой. Это обеспечивает ограничение насыщения внешних составляющих тиристор 1 л - р --«-транзисторов, ослабляет связь между информационными шинами 4, 5 и шиной хранения 3, т. е. обеспечивает устойчивое хранение информации при повышении быстродействия и уменьшении потребляемой мощности. Полностью исключить статическую связь между эмиттерами элемента памяти при хранении информации позволяет использование в ячейке памяти без необходимости выполнения топологии ячейки согласно фиг. 3 резисторов 9, 10 или диодов И, 12, шунтирующих центральный переход тиристоров 1, 2 со стороны внещней р-базы. Тем самым достигается возможность использования тока хранения с максимальным эффектом, обеспечивающим рост устойчивости информации. При записи информации в элемент памяти потенциал на одной из информационных щин 4 или 5, в данном случае при 6tкрывании тиристоров 2 на шине 5, понижается. В то же время на другой щине 4 потенциал достигает величины, обеспечивающей отсутствие тока через открытое ранее плечо тиристора 1. При этом через диод 8 или резистор Ш (фиг. 1) и перекрестную связь задается ток с адресной щины 6 во внешнюю р-базу тиристора 2 закрытого ранее плеча. Это обеспечивает вывод из насыщения и закрывание связанных с цепью хранения 3 составляющих р - л - р и л - р - л-транзисторов открытого ранее тиристора 1, и устойчивое состояние элемента памяти, соответствующее новой информации. Быстродействие элемента памяти по записи обеспечивается ограничением величины заряда неосновных носителей во внешних р-базах и л-базах тиристоров 1 и 2. Это достигается ограничением уровня а р - л - р-составляющего р - л -р-транзистора с внешней базой, включением резисторов 9, 10 или диодов 11, 12 между л-базами и внешними р-базами тиристоров 1, 2. При считывании новой информации (открыт тиристор 2) ток с адресной шины 6 проходит через внешнюю и внутреннюю р-базы открытого тиристора 2 соответственно в информационную шину 5 и цепь хранения 3, обеспечивая блокирование анодного р - л-перехода закрытого тиристора 1 и, таким образом, неразрушение информации. При этом заряд в базах открытого плеча тиристора 2 накапливается на уровне, близком к границе насыщения, что не снижает быстродействия элемента при записи. Поэтому в предлагаемом элементе памяти вопросы роста быстродействия наряду со снижением потребляемой в режиме хранения мощности могут решаться независимо, определяясь в каждом конкретном случае характеристиками ИС ОЗУ, в которой элемент памяти применяется. Предлагаемый элемент памяти в интегральном исполнении не требует дополнительной площади по сравнению с известным элементом, так как предусмотренные предлагаемой схемой элементы обеспечения записи и ограничения насыщения внещних составляющих л - р - л-транзисторов, в частности диоды и резисторы, могут быть выполнены топологически в р-аноде, л-базе, р-базах тиристоров. Формула изобретения 1. Симметричный тиристорный элемент памяти по авт. св. № 381098, отличающийся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, он содержит элементы свяЭй, а базовые области р-типа каждого тиристора выполиены в виде двух полуобластей, одиа из которых подключена через первый элемент связи к базовой области «-типа, через второй элемент связи - к адресной шине. 2.Элемент памяти по п. 1, отличающийся тем, что элементы связи выполнены на диодах. 3.Элемент памяти по п. 1, отличающийся тем, что первые элементы связи выполнены на резисторах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Элемент памяти | 1975 |

|

SU525160A1 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| СИММЕТРИЧНЫЙ ТИРИСТОРНЫЙ ЭЛЕМЕНТ НАМЯТИ | 1973 |

|

SU381098A1 |

| Интегральный элемент памяти | 1977 |

|

SU858102A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| ВПТБ Ш14Ш11Жу1 | 1973 |

|

SU409292A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| Инжекционный запоминающий элемент | 1974 |

|

SU526951A1 |

4 оР п

Р п

405-о

Авторы

Даты

1979-03-15—Публикация

1976-11-23—Подача