.Изобретение относится к вычислительной технике и может найти применение в цифровых вычислительных машинах и приборах четвертого поколения. Известно постоянное запоминающее устройство, содержащее числовые бло ки с большим числом элементов связи либо с большим числом прошитых сердечников 1 . Однако данное устройство характе ризуется низкой надежностью, большо потребляемой мощностью, большой неравномерностью нагрузки на адресные шины. Наиболее близким техническим решением к предлагаемому является устройство, содержащее дешифратор адреса, выходы которого соединены со входами запоминающих элементов накопителя и блока управления, выхо запоминающих элементов накопителя подключены к входам шифратора, сумматор по модулю два, к первому вход которого подключен выход шифратора, а ко второму - выход блока управления 21. Недостатками известного устройст являются большое число элементов св зи, используемых при реализации устройства, большай разрядность числового блока, низкая надежность и технологичность устройства. Цель изобретения - уменьшение потребляемой мощности и повышение надежности устройства. Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее регистр адреса, подключенный через дешифратор адреса к накопителю, блок местного управления и сумматор по модулю два, введены дополнительный накопитель, первый и второй выходные регистры слова и две группы элементов ИЛИ, причем одни из выходов элементов ИЛИ первой группы соединены с одними выходами дополнительного накопителя, другие выходы которого подключены к входам блока местного управления, входы дополнительного накопителя соединены с соответствующими выходами дешифратора адреса, выходов блока местного управления соединены с управляющими входами регистра адреса, а другие - с управляющими входами первого и второго выходных регистров слова, входы первого выходного регистра слова соединены с выходами основного накопителя

через элементы ИЛИ второй группы, а входы второго выходного регистра слова соединены с выходами основного накопителя непосредственно, выходы выходных регистров слова.соединены с входами сумматоров по модулю два, выход которого подключен к одному i3 входов элементов ИЛИ второй груп

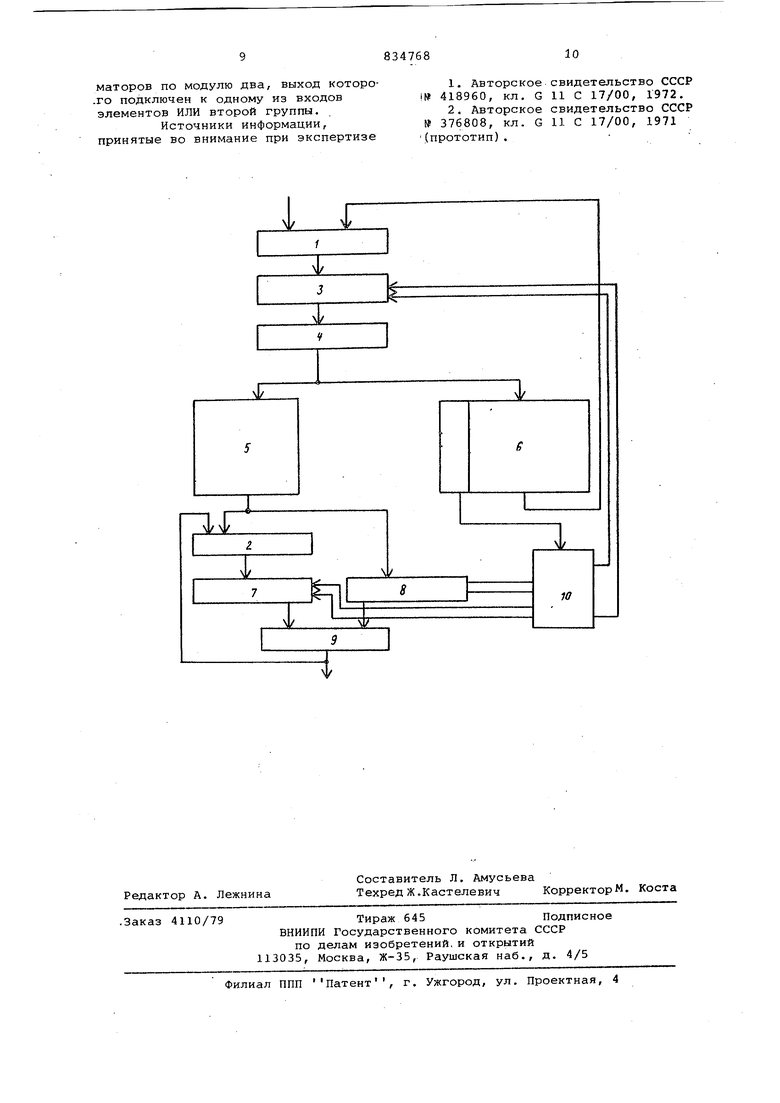

На чертеже представлена блок-схема постоянного запоминающего устройства.

Устройство содержит две группы 1 и 2 элементов ИЛИ, регистр 3 адреса, дешифратор 4 адреса, накопитель 5, дополнительный накопитель б, регистры 7 и 8 выходного слова, сумматоры 9 по модулю два, блок 10 местного управления.

В запоминающем устройстве записываемая исходная информация предварительно обрабатывается с целью уменьшения числа единиц по следующему алгоритму. Выбирается набор корректирующих кодов той же разрядности, как и записываемых в ПЗУ чисел. При этом для конкретного кода записываемого в ПЗУ числа выбирается из набора корректирующих кодов такой код , который после суммирования по модулю два с кодом исходного числа давал бы код с минимальным количеством единиц. Преобразованный код числа записывается в накопителе 5, но при считывании необходимо путем суммирования по модулю два считанного кода (преобразованного кода числа) с использованным корректирующим кодом восстановить исходный код числа. Выбор числа и значений корректирующих кодов может быть различным.

На практике при изготовлении матрицы накопителя возникают дефект которые могут быть типа генератор О или генератор 1. Введем условное понятие нулевой отказ, который имеет место при одинаковых направлениях возникшей неисправности и записываемой информации (т.е. имеется дефект типа генератор и нужно запиО

или имеется дефект типа

сать

генератор 1 и нужно записать ), и единичный отказ при разных направлениях неисправности и записываемого бита информации.Нулевые дефекты не оказывают влияние на правильность записи информации, а для маскировки единичных-дефектов (т.е. для исправления единичных отказов) значения разрядов, в которых есть единичные отказы, необходимо проинвертировать (суммировать по модулю два с единицей).

В устройстве есть возможность инвертировать часть разрядов записываемых чисел при помощи суммирования по модулю два с корректирующими кодами и таким образом маскировать влияние единичных отказов. При

этом необходимо учитывать, что в значениях разрядов , в местах записи которых есть нулевые отказы, инвертирование не производится, а , при наличии единичных отказов значения разрядов необходимо инвертировать.

Если предположить, что в ячейках, где записываются корректирующие коды нет отказов, то, используя выбранные корректирующие коды, можно маскировать отказы, возникшие для з.аписи исходных кодов чисел, значения которых не равны корректирующим кодам. В этом случае для восстановления исходного .числа (а) поступают следующим образом. При обращении по адресу числа а из накопителя 5 считывается преобразованный код этого числа, а из накопителя 6-адрес соответствующего корректирующего кода. После второго обращения к основному накопителю считывается, корректирующий код и производится суммирование по модулю два. Если же обращение производится по адресу корректирующего кода (т.е. корректирующий код является кодом исходной информации), то из накопителя 5 сразу считывается требуемый код, так как корректирующие коды не преобразуются, в этом случае для общности в дополнительном накопителе по адресу корректирующего кода записан фиктивный (несуществующий) адрес либо адрес ячейки, в которой записано число, равное нулю. Таким образом, при обращении по адресам корректирующих кодов необходимо дважды обращаться к накопителю 5, так как это приводит к упрощению блока управления, хотя второе обращение не нужно. Именно так организуется работа в устройстве, когда нет отказов в накопителе 5 и когда есть отказы в тех ячейках, в которых не записываются корректирующие коды. Однако и в ячей., где записываются корректирующие коды, также мо.гут возникнуть отказы. В этом случае можно поступить следующим образом. В ячейке корректирующего кода (к), в которой есть отказы, записывается такой код (с), который после суммирования по модулю два с одним из преобразованных кодов исходной информации или с одним из корректирующих кодов давал бы требуемый корректирующий код. Например, если необходимо записать корректирующий код 1010101 и в местах записи первого (2) и второго (2) разрядов этого числа есть соответственно нулевой и единичный отказы, то в ячейках есть код ааааа 11, где символом а обозначены исправные разряды ячейки, в которых можно записать либо О , либо . Выбирается код (Ь), являющийся либо преобразованным коде числа, либо корректирующим кодом, такой, чтобы с(Э b k, то есть: с - ааааа 11 b - ааааа 10 k - 10101101 В зависимости от кода (Ь), выбор которого осуществляется исходя из значений в данном случае его младши разрядов,определяется .код (с) . При обращении по адресу из накопителя 5 считывается код (с), а из накопи теля б считывается адресный код ячейки, где записан код (Ь). После считывания кода (Ь) производится суммирование по модулю два считанны кодов, т.е. производится двукратное обращение к накопителю 5. В случае обращения к ячейке, где записан код числа (d), для преобразования которого использован коррек тирующий код (к) ив месте записи которого есть отказы, считывание ин формации производится следующим образом. Одновременно со считыванием преобразованного кода (d ) числа считывается адрес корректирующего кода (к). Однако в основном накопителе по адресу корректирующего кода (к)-записан код (с). Одновременно со считыванием кода (с) из накопителя 5 из накопителя 6 считывается адресный код числа (Ь). После считывания (Ь) производится суммирование по модулю два (d)@(c) + (b) (d); (с)©(Ь) (к) Таким образом, при наличии отказов в ячейках корректирующих кодов число обращений к накопителю 5 пере менное (либо два, либо три). Поэтом в схему данного устройства необходимо ввести либо сигнальные триггер либо в накопителе б дополнительный разряд, указывающий число обращений к накопителю 5. В устройство вводят ся дополнительные разряды, при этом если значение дополнительного разря да равно нулю, то выполняются два обращения к накопителю 5, а если ед нице, то выполняются три обращения. Когда необходимо одно обращение к накопителю 5, тогда не требуется ячейки в накопителе б, так как не нужен адрес для вторичного обращени к накопителю 5. Следовательно, когд Требуется одно обращение к накопителю 5, можно не использовать фиктивные адреса. И тогда число ячеек накопителя б меньше числа ячеек накопителя 5. Есть возможность при наличии отказов в ячейках записи корректирующих кодов дважды обращаться к накопителю 5 в отличие от рассмотренног ранее, когда применяется трехкратно обращение к накопителю Ь. Для этого корректирующий код (к) помещается в ячейку, в которой нет отказов либо есть отказы, не оказывающие влияния, т.е. они являются нулевыми, где должен записываться код (Ь) числа .(Ь). При обращении в накопитель 5 по адресу ячейки, в которой должен быть записан преобразованной код (Ь), считывается корректирующий код (к), одновременно из накопителя 6 считывается адресный код ячейки, в которой записан такой код (с), что сумма по модулю два кода (с) и корректирующего кода (к) дала бы число (Ь). В ячейку, в которую должен быть записан корректирующий код (к) и в которой есть отказы, записывается такой код (d), что после суммирования его по модулю два с одним из преобразованных кодов исходной информации или с одним из корректирующих кодов, должен получиться требуемый корректирующий код (к). Выгодность такой.перестановки очевидна, если используемый корректирующий код (к) применяется для нескольких чисел исходной информации. Если необходимо двукратное обращение в накопитель 5, то устройство работает следующим образом. На входы элементов ИЛИ первой группы поступает код адреса, требуемый для считывания числа. Пусть это будет код (а). По сигналу Запись с одного из выходов блока 10 местного управления этот код записывается в регистр 3 адреса. По сигналу Считывание с другого выхода блока 10 местного управления код (а) подается на входы дешифратора 4, возбуждается один из его выходов, и из накопителя 5 считывается преобразованный код (Ъ), который по Запись сигналу с соответствующего выхода блока 10 местного управления записывается в регистр 8. Одновременно возбуждается еще один иэ выходов дешифратора 4, и из накопителя 6 считывается код адреса корректирующего кода, использованного для преобразования числа (с). Это код (d). Старший разряд этого кода является дополнительным, он связан с блоком 10 местного управления и указывает на количество обращений к накопителю 5. В данном случае значение дополнительного разряда равно О, следовательно, число обращений к накопителю равно 2. По сигналу Запись с одного из выходов блока 10 местного управления в регистр 3 адреса записывается код (d). По сигналу Считывание с другого выхода блока 10 местного управления код (d) подается на вход дешифратора 4, возбуждается один из его выходов, и на выходе накопителя 5 образуется код (f). По сигналу Запись с соответствующего выхода блока 10 естного управления через элементы ЛИ второй группы код (f) записывается в регистр 7. По сигналу Считывание с выходов блока 10 местного управления коды, записанные в регистрах 7 и 8, подаются на сумматоры 9 по модулю два, где происходит суммирование и подача результата через элементы ИЛИ второй группы на регистр 7. В регистре 7 будет записан код (bX3{t)c, т.е. необходимое число.

При трехкратном обращении к накопителю 5 устройство работает следующим образом.

При записи через элементы ИЛИ первой группы в регистр 3 адреса кода (а) с последующей подачей его через дешифратор 4 на входы накопителей 5 и б происходит считывание из накопителя 5 соответствующего кода (Ь) и запись его в регистр 8, а из накопителя.6 - считывание адресного кода (с).

Единица в дополнительном разряде указывает на то, что число обращений к накопителю 5 равно 3. Для этого из накопителя 6 в блок 10 местного управления подается соответствую.щий сигнал. По адресу (с) производится вторичное обращение к накопителю 5 и считывание кода (f) с последующей записью его через элементы И второй группы в регистр 7. А из накопителей 6 происходит считывание адресного кода (р) для обращения к накопителю 5. По сигналу Считывание, подаваемому с выходов блока 10 местного управления соответственно на регистры 7 и 8, происходит подача кодов (f) и (Ь) на сумматоры 9 по модулю два, их суммирование и прием результата (s) через элементы ИЛИ 2 второй группы в регистр 7. По сигналу Считывание с одного из выходов блока 10 местного управления через дешифратор 4 происходит считывание из накопителя 5 кода (т) и подача его по сигналу Запись с другого выхода блока 10 местного управления соответственно на регистр 8. По сигналу Считывание, подаваемому с выходов блока 10 местного управления соответственно на регистры 7 и В, происходит подача кодов (s) и (т) на сумматоры 9 по модулю два. Результат суммирования (s) через элементы ИЛИ второй группы записывается в регистр 7.

Пусть в накопителе 5 записаны корректирующие коды, причем в ячейках для их записи, как было принято нет отказов, тогда при обращении в накопитель 5 по одному из этих адресов из накопителя, считывается код 00000. Нуль в дополнительном разряде указывает, что число обращений к накопителю 5 равно 2.

Адресный код (00000) записывается в регистр 3 адреса, затем через дешифратор 4 происходит считывание по данному адресу соответствующего

кода, однако кода с таким адресом в накопителе 5 нет, поэтому при подаче сигнала Считывание на регистры 7 и 8 на сумматор подаются лишь значения разрядов регистра 8, куда 5 после первого обращения к накопителю 5 был записан соответствующий корректирующий код. С выходов сумматора 9 по модулю два корректирую1яий код записывается через элементы ИЛИ второй группы в регистр 7.

Для записи одной и той же информации в предлагаемом устройстве требуется емкость памяти

+ п+1

5 в

раз (при ) или в п+к

( +l)N+n2

раз(при )меньше п+к

чем в известном,что является несомненным преимуществом предлагаемого устройства,где п - разрядность N чисел; к - разрядность числа в дополнительном накопителе.

Предлагаемое устройство по сравнению с известным при незначительном увеличении аппаратурных затрат имеет более высокую надежность, кроме того, оно защищено от дефектов матрицы И имеет сравнительно небольшую потребляемую мощность.

Формула изобретения

Постоянное запоминающее устройство, содержащее регистр адреса,подключенный через дешифратор адреса к накопителю, блок местного управления и сумматор по модулю два, отличающееся тем, что, с целью уменьшения потребляемой мощности и повышения надежности устройства, в него введены дополнительный накопитель, первый и второй выходные регистры слова и группы элементов ИЛИ, причем один из выходов элементов ИЛИ первой группы соединены с одними выходами дополнительного накопителя, другие выходы которого подп ключены к входам блока местного управления, входы дополнительного накопителя соединены с соответствующими выходами дешифратора адреса, одни из выходов блока местного управления соединены с управляющими входами регистра адреса/ а другие с управляющими входами первого и второго выходных регистров слова, входы первого выходного регистра слова соединены с выходами основного накопителя через элементы ИЛИ

второй группы, а входы второго выходного регистра слова соединены с выт ходами основного накопителя непосредственно, выходы выходных регистров слова соединены с входами сумматоров по модулю два, выход которо.го подключен к одному из входов элементов ИЛИ второй группы.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 11 С 17/00, 1972.

свидетельство СССР 11 С 17/00, 1971

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Постоянное запоминающее устройсство | 1977 |

|

SU637869A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

Авторы

Даты

1981-05-30—Публикация

1977-03-23—Подача