ности, группу элементов И, элементы ИЛИ, элементы НЕ и элемент задержки, вход которого и выходы синхронизации регистра управляющих ;сигналов и регистра неисправности объединены и являются первым входом блока, вторьм и третьим входом которого являются соответственно вход признака записи-считывания и вход обращения регистра управлякяцих сигналов, установочный вход которого и установочный вход регистра неисправности объединены и являются четвертым входом блока, причем входы первого, второго и третьего элементов НЕ являются соответственно 1 пятым, шестым и седьмым входами блока, первый и второй входы элементов И группы подключены соответственно к выходу и входу элемента задержки, третий и четвертый входы элементов И группы соединены с выхо дом регистра згаравляющих сигналов и с выходом регистра неисправности, входы с пятого по десятый элементов И группы подключены соответственно к выходам и входам первого, второго и третьего элементов НЕ, выходы элементов И группы соединены с входами элементов ШШ, выходы которых являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU763977A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU809399A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU836682A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Устройство для записи и воспроизведения цифровой информации | 1990 |

|

SU1742856A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопитель, сумматоры по ьюдулю два, блок управления, регистр адреса и первый элемент И, причем выходы накопителя подключены к информационшл входам первого сумматора по модулю два и являются числовыми выходами устройства, управляющие входы накопителя, первого и второго сумматоров по модулю два соединеш 1 соответственном с первым, вторым и третьим выходами блока управления, первый вход которого и ОД1Ш из входов регистра адреса являются входами синхронизации устройства, второй и третий входы блока управления являются соответственно входом признака записи-считывания и входом обращения устройства, четвертый вход блока управления, установочные входы сумматоров по модулю два и управляющий вход регистра адреса являются входами начальной установки устройства, адресными входами которого являются другие входы регистра адреса, отличающееся тем, что, с целью упрощения устройства, в него введены счетчик адресов, блок сравнения. адресный мультиплексор, числовой мультиплексор и второй элемент И, входы которого соединены с выходами счетчика адресов и одними из входов блока сравнения и адресного мультиплексора, выходы которого подключены к адресным входам накопителя, а другие входы - к выходам регистра адреса и другим входам блока сравнения, входы числового мультиплексора соединены соответственно с выходами накопителя и с выходами первого сумматора по модулю два, а выходы - с информационными входами второго сумматора по модулю два, ш 1ходы которого подключены к входам первого элемента И, выход которого (П соединен с пятым входом блока управления, щестой и седьмоД которого подключены соответственно к выходу блока управления и к выходу Второго элемента И, дричец управля|(г щие входы числового мультиплексора и адресного мультиплексора соединены соответственно с четвертым и с пятым ;о выходами блока управления, щестой 4 выход которого подключен к входу заО пуска счетчика адресов, установоч sj ный вход которого соединен с управгг лякжрш входом регистра адреса, вы- ход второго сумматора по модулю два является контрольным выходом устройства, седьмой и восьмой выходы блока управления являются соответственно выходом сигнала; готовности и выходом сигнала исправности уст;ройства, 2. Устройство по п. 1, отличающееся тем, что блок управления содержит регистр управЛЯЮ1ЦИХ сигналов, регистр неисправ

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Известно запоминающее устройство (ЗУ) с самоконтролем, содержащее накопитель информации, первый и второй сумматоры, числовой мультиплек;сор и управляющую память со счетчиком количества считанньщ слов для реапизации алгоритма контроля LIU.

Недостатком этого устройства является его сложность.

Наиболее близким по технической сущности к изобретению является запоминающее устройство с самоконтролем, содержащее адресный накопитель информации, сумматоры, блок управления, использующееся в качестве управляющей памяти ассоциативное запоминающее устройство, одни из входов которого соединены с адресными входами адресного накопителя и выходами элементов И, другие входы подключены к выходам блока управления, а выходы соединены с входами второго сумматора, с первыми входами элементов И и с входами блока управления, один из управляющих и информационный входы адресного накопителя подключены ср. ответственно к первому и второму входам первого сумматора, выход адресного накопителя соединен с третьим входом первого сумматора и первым входом второго сумматора.

второй вход которого соединен с выходом первого сумматора, вторые входы элементов И. соединены с другим управляютщм входом адресного накопителя, а третьи входы являются адресными входами устройства С21.

Недостатком этого устройства является применение ассоциативного накопителя в качестве аппаратных средств уттравлепия контролем, что усложняет устройство.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, сумматоры по модулю два, блок управления, регистр адреса и первый элемент И, причем выходы накопителя подключены к информационным входам первого сумматора по модулю два и являются числовыми выходами устройства, управляющие входы накопителя, первого и второго сзгмматоров по модулю два соединены соответственно, с первым, вторым и третьим выходами блока управления, первый вход которого и один из входов регистра адреса являются входами синхронизации устройства, второй и третий входы блока управления являются соответственно входом 11ризяя1 а эаписи-считцвдния и обращения устройства, четверть вхо блока управления, установочные входы cyj axopoB по модулю два и управляющий вход регистра адреса являются входами начальной установки устройства, адресными входами которого являются другие входы регистра адреса, введены счетчик адресов, блок сравнения, адресный мультиплексор, числовой мультиплексор и второй элемент Н, входы которого соединены с выходами счетчика адресов и одними из входов блока сравнения и адресного мультиплексора, выходы которого подключены к адресным входам накопителя, а другие входы - к выходам регистра адреса и другим входам блока сравнения, входы числового мультиплексора соединены соответственйо с выходами накопителя и с выходами первого сумматора по модулю два, а выходы - с информационными входами второго сумматора по лодулю два, выходы которого подключены к входам первого элемента И, выход которого соединен с пятым входом блока управления, шестой и седьмой входа которого подключешл соответственно к выходу блока управления и к выходу второго элемента И, причем управляющие входы числового мультиплексора и адресного мультиплексора соединены соответственно с четвертым и с пятым выходами блока управления, шестой выход которого подключен к входу запуска счетчика адресов, установочный вход которого соединен с управляющим входом регистра адреса, выхоД второго сумматора по модулю два является конт,рольным выходом устройства, седьмой и восьмой выхода блока управления являются соответственно выходом сигнала готовности и выходом сигнала исправности устройства.

Кроме того,блок управления содержит регистр управляющих сигналов,регистр неисправности, группу элементов И, элементы ИЛИ, элементы НЕ и элемент задержки, вход которого и входы синхронизации регистра управляюд х сигналов и регистра неисправности объединены и являются nepBbiM входом блока, вторым и третьим входом которого являются соответственно вход признака записисчитывания и вход обращения регистра управляющих сигналов, установочный вход которого и установочный вход регистра неисп| авности объединены и являются четвертым входом блока,

причем входы первого, второго и третьего элементов НЕ являются соот ветственно пять, щестым и седьмьй входами , первый и второй, входы элементов Н группы подключены соответственно.к вьЬсоду и входу элемента задержки, третий и четвертьй входы элементов Н .группы соединены с выходом регистра управляклцих сигналов и с выходом регистра неисправoности, входы с пятого по десятый элементов И группы подключены соответственно к выходам и входам первого, второго и третьего элементов НЕ, выходы элементов И группы соединены

5 с входами элементов ИЛИ, выходы которых являются выходами блока.

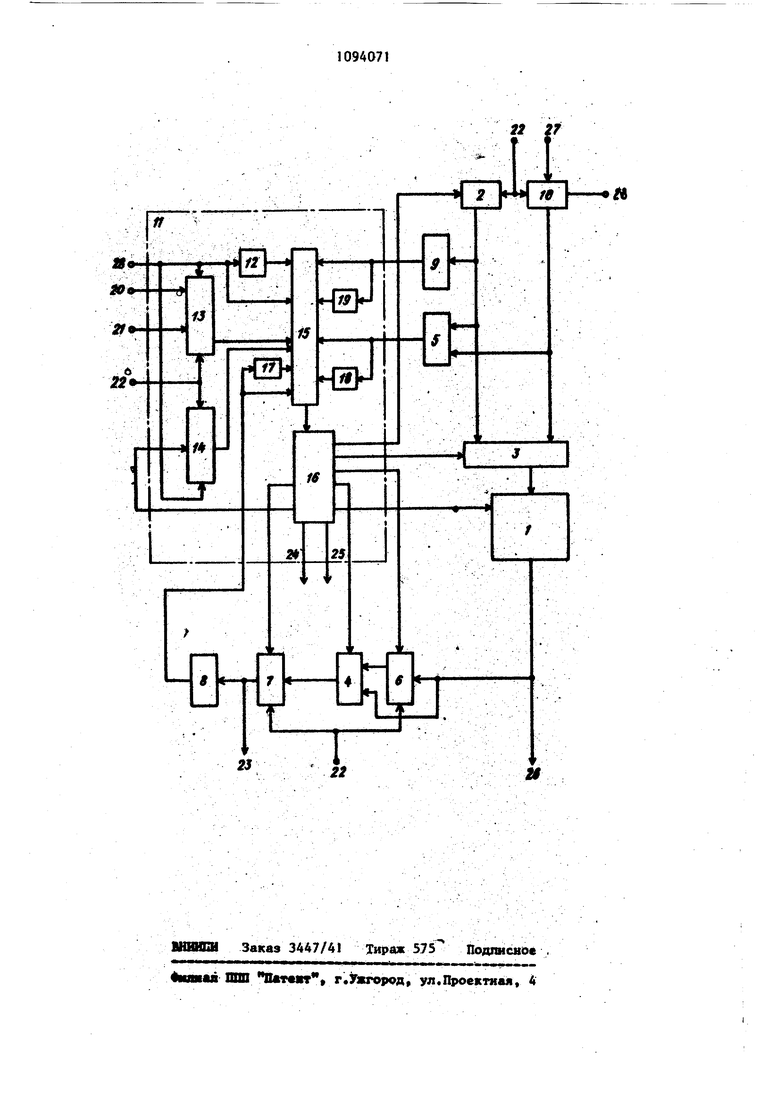

На чертеже изображена функциональная схема предлагаемого устройства.

0

Устройство содержит накопитель 1, счетчик 2 адресов, адресный 3 и числовой 4 мультиплексоры, блок 5 сравнения, первый 6 и второй 7 сумматоры по модулю два, первый 8 и второй 9 элементы И, регистр 10 адреса и блок I управления, содержащий элемент 12 задержки, регистр 13 управляющих сигналов, регистр 14 сигналов неисправности, группу 15 элементов И, элементы ИЛИ 16, первый 17, второй 18 и третий 19 элементы НЕ, На чертеже обозначены вход

20признака записи-считывания, вход

21обращения, входы 22 начальной установки, контрольные выходы 23, выход 24 сигнала готовности, выход 25 сигнала исправности, информационные выходы 26, адресные входы 27

и вход 28 синхронизации. Блок 5 сравнения может быть выполнен на

кросхеме К555 СП1...

1 Предлагаемое устройство в режимах начального и циклического конт-, рольного суммирования информации, . содержащейся в накопителе, работает следующим образом.

Начальное суммирование производится для определения контрольной суммы информахщи накопителя 1 до начала обмена информацией с внешним устройством (не показано) и происходит следуюи им образом.

Сигнал, поступающий на входы 22, устанавливает регистры 12 и суммагторы 6 и 7 в начальное (нулевое) состояние, а регистр 14 - в со:стояние начального суммирования. I Элементами И 15 и элементами 16 на выходе 24 вырабатывается сигнал запрета внешнего обращения к устройству, сигнал управления |ультидлексором 3, поступающий с блокд и, пропус1 ает на адресные входы накопителя .1 код адрес с выходов счетчика 2, При подаче сигналу синхронизации на ВХ9Д 28 -через элемент 12 задержки элементы И 15 и ИЛИ 16 формируют сигналы на управляющих входах сумма торов 6 и 7 для стробирования информации с выходов накопителя 1, а также сигналы Обращение и признак Чтение на управляющих входах нако пителя 1. Запуск счетчика 2 произво дится сигналами, совпадающими во времени с синхронизирующими. Значение кода счетчика 2 увеличивается на единицу при каждом сигнале запуска, поступающем с блока И на уп равляющие входы счетчика 2. Считыва мая по каждому адресу из накопителя I информация поступает на вход сумматора 6 и через мультиплексор 4 открытый сигналом от блока II, проходит на вход сумматора 7. Сумматоры 6 и 7 накапливают конт рольную сумму информации накопителя I. При достижении счетчиком 2 конеч ного состояния, определяемого элементов И 9, начальное суммирование заканчивается, сумматоры 6 и 7 хранят контрольную сумму информации, содержащейся во всем массиве адресо накопителя I. Рассмотренный реж1Ф1 кодируется определенным состоянием разрядов ре гистра 14. Переход к режиму циклического контрольного суммирования сопровождается установлением на счетчике 2 начального состояния, вцдачей сигнала готовности на выходе 24, состоянием контрольного суммирования регистра 14 и сигналом исправности на выходе 25. Работа устройства в режиме цикли ческого контрольного суммирования происходит в процессе обмени инфор мацией с внешним устройством. Предполагается, что при обращения: К устройству в режиме записи происходит предварительное считывание из накопителя 1 хранившейся информации на выходы 26, Внешние обращения синхронизированы сигналами на входе 28, При отсутствии сигнала обращения на входе 21 (в момент подачи синхронизирующего сигнала) иа адресные входы накопителя 1 через мультиплексор 3 передается код содержимого счетчика 2, т,е. код числа конт-, ролируемых адресов, J1 вырабатываются сигналы внутреннего обращения и признак Чтение на уптравляющих входах накопителя 1 при наличии синхроимпульса на входе 28,Информация из накопителя t при отсутствии внешнего обращения суммируется только сумматором 7. Сумматор 6 в этом случае суммирования не производит, Накапливакяций сумматор 6 образует и хранит ко 1трольную сумму, которая может меняться только прн наличии внешнего обращения в режиме записи. Образование нового значения контрольной суммы сумматоров 6 производится сложением хранящейся контрольной cjrMM i с разностью между записываемой и предварительно считанной из накопителя 1 информацией. Код адреса внешнего обращения по входу 27 поступает в регистр 10 и фиксируется в нем синхроимпульсом, поступающим по входу 28, Управлякяцие сигналы, поступающие при внешнем обращении по входам 20 и 21 на вход регистра 13, также фиксируются в нем синхроимпульсом со входа 28, Блок 11 обеспечивает передачу адреса и управляюпщх сигналов на адресные и управляющие входы накопителя 1 „ Работа сумматора 7 в этом случае определяется относительным значением кода счетчика 2 и кода регистра 10, сигналами признака Записьсчитывание на входе 20, сигналом обращения на входе 2I, состоянием счетчика 2, Сумматор 70 производит суммирование информации из накопителя 1 по адресу, содержащемуся в регистре 10, при внешнем обршцении, если код адреса в регистре 10 больше ко- да в счетчике 2 и производится операция Запись или код адреса в регистре 10 равен коду в счетчике 2 В первом случае по управляющим сигналам из блока 1.1 в сумматоре 7 образуется новое значение контрольной суммы сложением храняцейся в сумматоре 7 контрольной суммы с разностью между записываемой и предварительно считанной по этому адресу информацией из накопителя 1. Во втором случае суммируется только считываемая из накопителя 1 информация. Сумматор 7 не производит суммирование при внешнем обращении, если код адреса в регистре 10 меньше код в счетчике 2 или код адреса в регистре 10 больше кода счетчика 2 и производится операция Чтение. Относительное значение кодов регистра 10 и счетчика 2 в троичном алфавите состояний Больше, Равно Меньше определяется двоичными выходами блока 5, Код адреса в счетчике 2 после считывания по нему информации из на копителя 1 и последующего суммирова ния увеличивается на единицу. При достижении счетчиком 2 конеч ного адреса элемент И 9 передает в блок 10 соответствующий сигнал. После считьшания информации с конечного адреса блоком 11 производится анализ результата контрольног суммирования в текущем цикле путем опроса состояния сумматора 7, которое должно быть нулевым в случае ijP вильного считывания информации и оп ределяется элементом И 8, 718 При ненулевом состоянии сумматора 7 блоком 11 формируется сигнал неисправности на выходе 25, а регистр 14 устанавливается в состояние Неисправность ЗУ. Таким образом, устройство обнаруживает любое количество ошибок в считанном слове и обеспечивает локализацию, отказавших разрядов накопителя 1. Код состояния сумматора 7, соответствующий ошибке,, считывается внешним устройством с выходов 23. При нулевом состоянии сумматора 7 блок 11 при поступлении синхроимпульса на вход 28 формирует управ-, ляющие сигналы, поступающие на сумматоры 6 и 7 и мультиплексор 4, по которым происходит передача содержимого сумматора 6 в сумматор 7. Счетчик. 2 переводится в начальное состояние сигналом из блока 11, после чего начинается новый цикл контрольного суммирования, аналогичный рассмотренному. В предложенном устройстве не требуется наличия дополнительного разряда и ассоциативного накопителя для контроля, что упрощает устройство за счет сокращения аппаратных средств. Технико-экономическое преимущество предлагаемого устройства по сравнению с известным заключается в его упрощении.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU763977A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-23—Публикация

1983-01-06—Подача