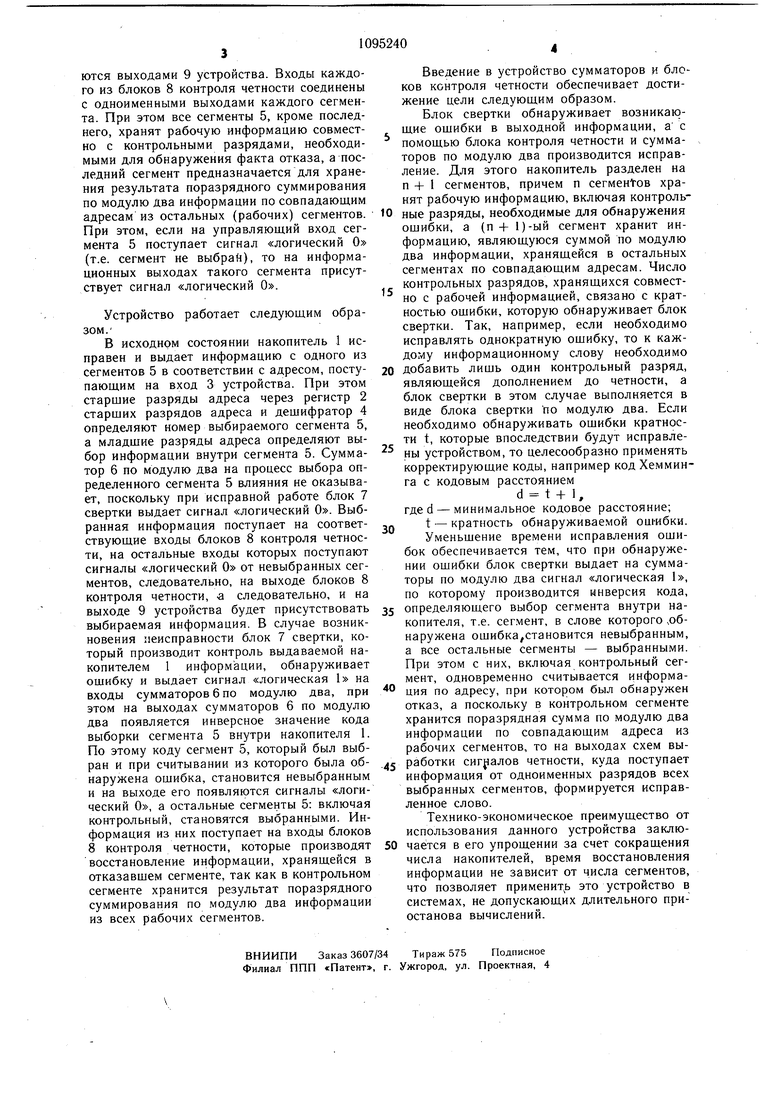

Изобретение относится к вычислительной технике и предназначено для использования в устройствах повышенной надежности, в частности в специализированных вычислительных машинах, применяемых на борту летательных аппаратов. Известно запоминающее устройство с самбконтролем, содержащее накопители, блок управления, входные и выходные коммутаторы, блоки свертки по модулю два, блок поразрядного сравнения, коммутатор, причем входы устройства соединены с соответствующими входами входных коммутаторов, выходы которых соединены со входами накопителей, их выходы соединены с входами выходных коммутаторов, выходы которых соединены с входами соответствующих блоков свертки по модулю два, входами блока поразрядного сравнения и входами коммутатора, выход его соединен с выходом устройства. Выходы блоков свертки по модулю два и блока поразрядного сравнения соединены со входами блока управления, выходы которого соединены с управляющими входами входных и выходных коммутаторов. Управляющий выход блока управления соединен с управляющим входом коммутатора 1. Устройство позволяет осуществлять исправную работу даже при наличии отказов в накопителях. Недостатком такого запоминающего устройства является низкая надежность, обусловленная тем, что в случае построения запоминающего устройства может исправлять ся лищь двухкратная ощибка и для повышения кратности исправляемой ошибки следует увеличить число накопителей. Следует отметить, что при построении постоянного запоминающего устройства кратность исправляемой ошибки при двух накопителях снижается до единицы. Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является запоминающее устройство с самоконтролем, содержащее блоки свертки по модулю два, блок поразрядного сравнения, предназначенный для сравнения информации, поступающей из накопителей, блок управления, предназначенный для выработки управляющих сигналов, коммутатор, предназначенный для подключения к выходу устройства исправного накопителя, причем одни из входов накопителей соответственно объединены и являются адресными входами устройства, а выходы соединены с информационными входами блоков свертки по модулю два, с входом блока поразрядного сравнения и коммутатора, выход которого является выходом устройства. Выходы блока поразрядного сравнения и блоков свертки по модулю два соединены с входами блока управления, первый вход которого соединен с управляющим входом коммутатора. Устроиство также содержит счетчик импульсов, который также может выполнять роль регистра старщих разрядов адреса, дещифратор, элемент И и генератор, выход которого соединен с одним из входов элемента И, выход которого соединен с одним из в;юдов счетчика импульсов, другие входы которого соединены с адресным входом устройства, а выходы - с входами дещифратора, выходы которого соединены с другими входами накопителей. Второй вход элемента И соединен со вторым выходом блока управления и управляющим входом блоков свертки по модулю два 2. Недостатками этого устройства являются высокая сложность, обусловленная наличием двух накопителей, хранящих идентичную информацию, и длительное время восстановления информации в случае обнаружения отказа, обусловленное необходимостью последовательного считывания и суммирования информации из сегментов, на которые разделены накопители. Целью изобретения является упрощение устройства и повыщение его быстродействия. Указанная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, регистр адреса, дещифратор, один вход накопителя подключен к входу регистра адреса и является входом устройства, выход регистра адреса подключен ко входу дещифратора, блок свертки по модулю два, введены сумматоры и блоки контроля четности, входы которых соединены с соответствующими выходами накопителя, а выходы соединены со входами блока свертки по модулю два и являются выходами устройства, выход блока свертки по модулю два подключен к первым входам сумматоров, вторые входы которых подключены к соответствующим выходам дещифратора, выходы сумматоров соединены с другими .входами накопителя. На чертеже изображена структурная схема запоминающего устройства с самоконтролем., Устройство содержит накопитель 1, один вход которого соединен с входом регистра 2 старших разрядов адреса и является входом 3 устройства, а выходы регистра 2 старших разрядов адреса соединены со входами де-. шифратора 4, который предназначен для выработки унитарного кода выбора определенного сегмента 5, на которые разделен накопитель 1. Управляющий вход каждого сегмента 5 соединен с выходом соответствующего сумматора 6 по модулю два, предназначенного для выработки инверсного значения сигнала, поступающего .на первый вход от соответствующего выхода дещифратора 4 по управляющему сигналу, поступающему на вторые входы с выхода блока 7 свертки, входы которого соединены с выходами блоков контроля четности 8, которые явля

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1089627A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1113790A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопитель, регистр адреса, дешифратор, один вход накопителя подключен к вхо.ау регистра адреса и является входом устрой г-ip. Т Т 1 т :,:;:.. твто вш ства, выход регистра адреса подключен к входу дешифратора, блок свертки по модулю два, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, в него введены сумматоры и блоки контроля i eTHOCTH, входы которых соединены с соответствующими выходами накопителя, а выходы соединены с входами блока свертки по модулю два и являются выходами устройства, выход блока свертки по модулю два подключен к первым входам сумматоров, вторые входы которых подключены к соответствующим выходам дешифратора, выходы сумматоров соединены с другими входами накопителя. (Л S со ел ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированное оперативное запоминащее устройство | 1975 |

|

SU589623A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-30—Публикация

1983-01-06—Подача