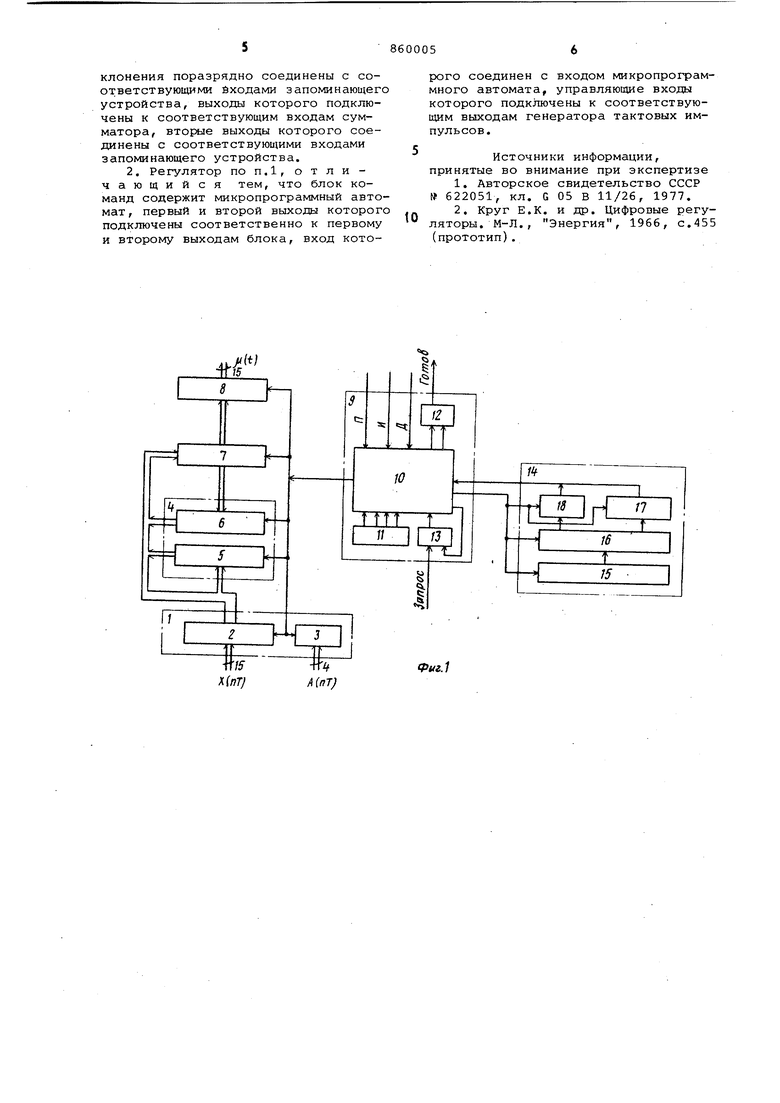

Изобретение относится к автоматическому управлению и может быть использовано для многоканальных электр приводов работотехнических систем. Известен цифровой регулятор, содеожащий вычислительное устройство, блок команд, блок настроек и регистры ll . Недостатками известного устройств являются невысокое быстродействие и сложность. Наиболее близким к предлагаемому по технической сущности является циф ровой пропорционально-интегральнодифференциальный регулятор, содержащий 6.ПОК команд, первый выход которо го соединен с первыми входами регист ра отклонения, регистра результата., запоминающего устройства и сумматора а второй выход - с входом блока настроек, причем первые выходы сумматора подключены поразрядно к соответ ствующим входам регистра результата Недостатками данного регулятора являются сложность и низкое быстродействие. Цель изобретения - повышение быст родействия и упрощение регулятора. Указанная цель достигается тем, что выход блока настроек регулятора соединен с входом блока команд, выходы регистра отклонения поразрядно соединены с соответствующими входами запоминающего устройства, выходы которого подключены к соответствующим входам cyMNiaTopa, вторые выходы которого соединены с соответствующими входами запоминающего устройства. Причем блок команд содержит микропрограммный автомат, первый и второй выходы которого подключены соответственно к первому и второму выходам блока, вход которого соединен с входом микропрограммного автомата,управляющие входы которого подключены к соответствующим выходам генератора тактовых импульсов. . На фиг. 1 изображена блок-схема предлагаемого регулятора; на фиг. 2 то же, алгоритма работы микропрограммного автомата. Регулятор содержит регистр 1 -отклонения, включающий регистр 2 ошибки и регистр 3 адреса, запоминающее устройство 4, состоящее из ячеек памяти величины ошибки слежения 5 и ве.личины суммы 6, сумматор 7, регистр 8 результата, блок 9 команд, состоящий из микропрограммного автомата (МПА) 10, выдающего микрокоманды, которые управляют работой всего регулятора, генератора 11 импульсов, триггера 12 готовности, триггера 13 запуска, блок 14 настроек, состоящий из схемы 15 опроса констант, схемы 16 формирователя констант, регистра 17 кон:зтант и счетчика 18. Регулятор обеспечивает формирование регулирующего воздействия по каждому каналу, описываемое формулой a)- K K XCvrr)tK2lx(iTM(HT)-x(() где X (и Т ) - величинарассогласовани для канала, к.к,к - параметры настройки рег лятора для канала. Полный цикл работы ПИД регулятора определяется состоянием г шкропрограм много автомата, В новое состояние автомат переходит по первому такту, выдаваемому генератором 11 импульсов и одно состояние длится четыре такта частоты 500 кГц. Выходы МПА подсоеди нены к управляющим входам всех функциональных узлов регулятора, а на его вход подается информация о состо яниях счетчика 18 и регистра 17 констант в младший разряд последнего. Величина ошибки слежения Х(цТ) (15раэрядное двоичное число) поступает в регистр оглибки, а адрес соответствующего следящего привода А(и Т) (4 разрядное двоичное число) - в адреса одновременно с сигналом запро са. Последний устанавливает триггер 13 запуска в единичное состоягше, а триггер 12 готовности в нулевое состояние и запускает МПА , В состоянии автомата С,, кроме записи в регистр отклонения ошибки слежения и адреса привода, происходит обнуление сумматора 7 и предварительный выбор константы К. После чего автомат переходит в следующее состояние С2(фиг.2 В этом состоянии производится очистка сумматора 7 и выбранная константа К 2 записывается в регистр 17 констан и счетчик 18 (мантисса - в регистр константы, порядок - в счетчик), В состояниях осуществляется пред вычисление очередного слагаемого интгегральной составляющей при участии сумматора 7, регистра 2 ошибки МПА I В состоянии С завершается вычисление очередного слагаемого интегральной составляющей в сумматоре 7. В состоянии С 7 вычисляется текущее значение интегральной составляющей закона регулирования, В следующем состоянии С g текущее значение интегральной составляющей запоминается в ячейки б памяти для данного канала и. .на этом завершается вычисление интегральной составляющей . в текущем цикле. В состоянии С «5 обнуляется триггер 13 запуска,сумматор 7 очищается для вычисления пропорциональной составляющей и производится выбор константы К, Далее повторяется состояние автомата Су, но уже в регистр 17 констант и счетчик 18 записываются мантисса и порядок константы Kj, а в состояниях осуществляется вычисление пропорциональной составляющей закона регулирования. В состоянии С опроизводится суммирование пропорциональной составляющей, находящейся в сумматоре, с хранящимся в ячейке 5 памяти предыдущим значением величины рассогласования, взятым с обратным знаком. В состоянии С завершается формирование суммы пропорциональной и дифференциальной составляющих закона регулирования в сумматоре 7 и производится запоминание величины текущего рассогласования с обратным знаком в ячейки 5 запоминающего устройства. Завершается формирование суммы всех составляющих закона регулирования в состоянии С. В состоянии автомата производится запись суммы всех составляющих закона регулирования в выходной регистр 8 результата и выбор константы Kg, которая в этом состоянии записывается в счетчик блока настроек. Умножение суммы составляющих на константу для завершения вычисления по закону регулирования производится в состоянии а затем МПА 10 переходит в состояние С и регулятор возвращается в исходное состояние: триггер 12 готовности устанавливается в единичное состояние и блок 9 ожидает очередного запроса на обслуживание. Применение в цифровом ПИД-регуляторе сумматора-вычитателя параллельного типа, управляемого МПА,позволяет увеличить быстродействие устройства, так как нет лишних пересылок из сумматора в регистр и все вычисления производятся в сумматоре. Это дает возможность значительно повысить скорость вычисления управляющего воздействия по ПИД-закону при более простой структуре регулятора и получить в результате значительный технико-экономический эффект. Формула изобретения 1, Цифровой пропорционально-интегрально-дифференциальный регулятор, содержащий блок команд, первый выход которого соединен с первыми входами регистра отклонения, регистра результата, запоминающего устройства и сумматора, а второй выход - с входом блока настроек, причем первые выходы сумматора подключены поразрядно к соответствующим входам регистра результата, отличающийся тем, что, с целью повышения быстродействия и упрощения регулятора, выход блока настроек соединен с входом блока команд, выходы регистра отклонения поразрядно соединены с соответствующими входами запоминающего устройства, выходы которого подключены к соответствующим входам сумматора, вторые выходы которого соединены с соответствующими входами запоминающего устройства.

2, Регулятор по п.1, отлитем, что блок кочающийся

М СЯ W Щ ri

манд содержит микропрограммный автомат, первый и второй выходы которого подключены соответственно к первому и второму выходам блока, вход которого соединен с входом микропрограммного автомата, управляющие входы которого подключены к соответствующим выходам генератора тактовых импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 622051, кл. G 05 В 11/26, 1977.

2.Круг Е.К. и др. Цифровые регу0ляторы. М-Л. , Энергия, 1966, с.455

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство микропрограммного управления при к-значном кодировании | 1972 |

|

SU474806A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 2000 |

|

RU2182359C2 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

Авторы

Даты

1981-08-30—Публикация

1979-06-07—Подача