3

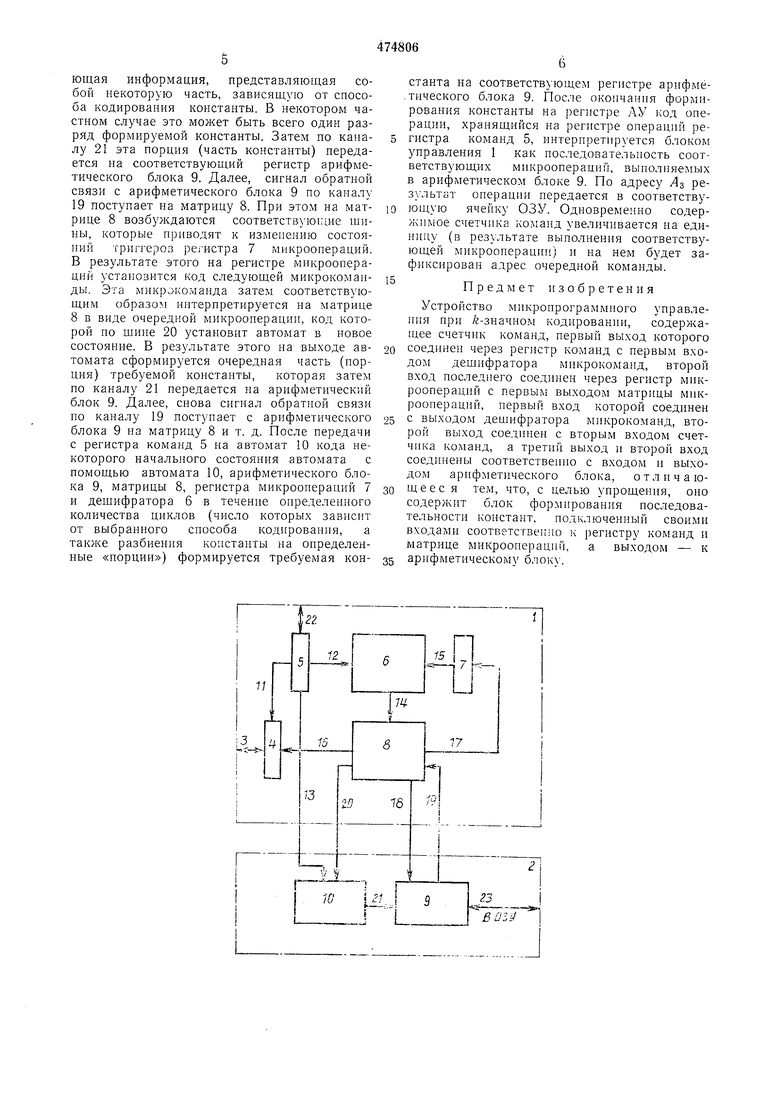

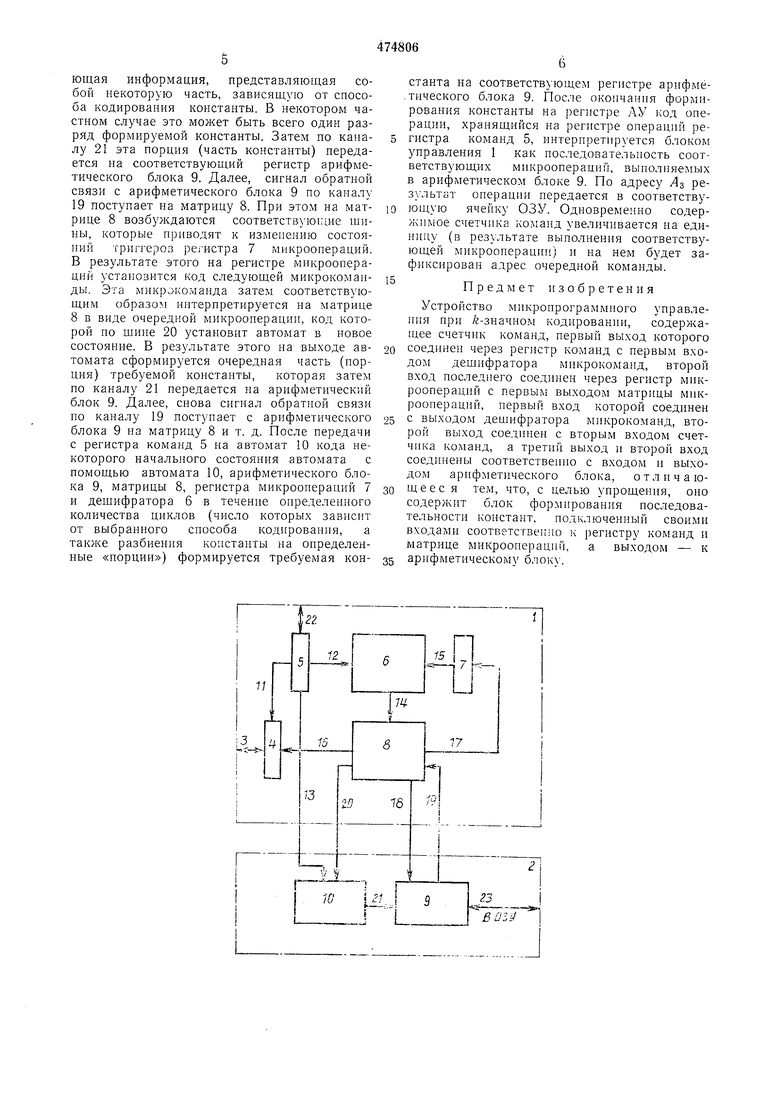

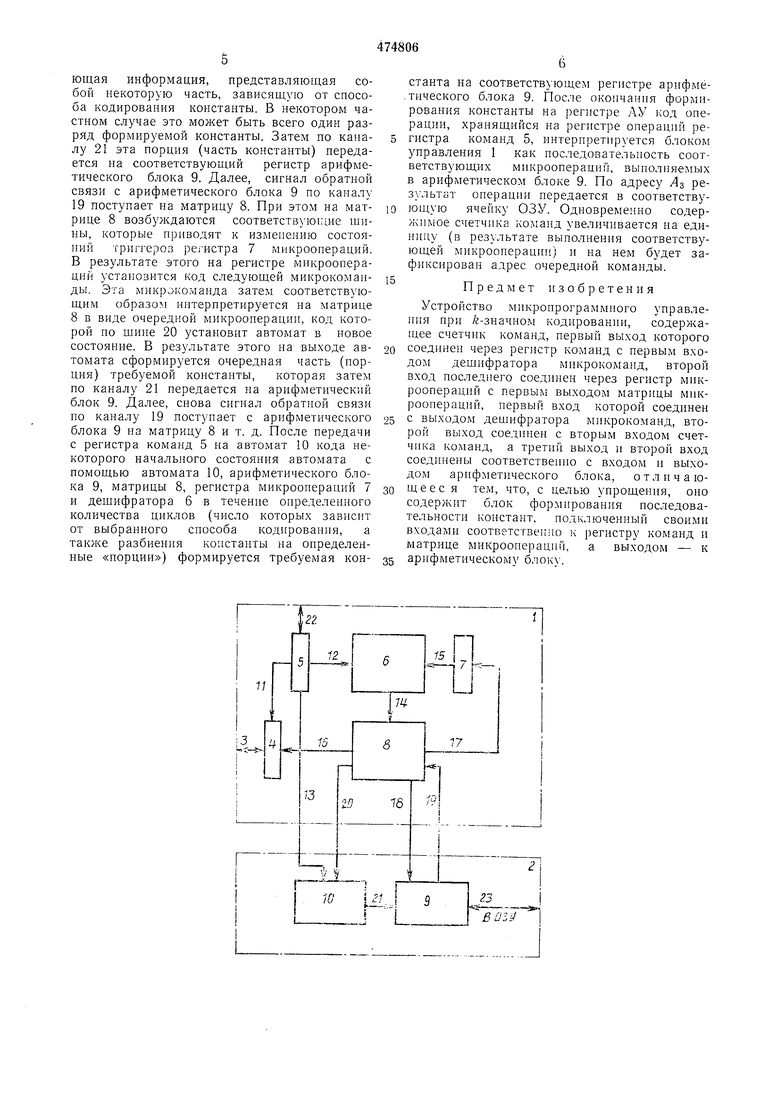

ку команд 4, дешифратору 6 и блоку 10 формирования последовательности констант соответственно. По каналу 11 происходит нередача кода адреса очередной команды на счетчик команд 4 при выполнении операций переадресации и условного перехода по точному совпадению слов. По каналу 22 происходит обмен командами с ОЗУ машины. При этом могут выполняться следующие микрооперации: передача кода из регистра числа ОЗУ иа регистр команд; передача первого адреса из регистра адреса, входящего в состав регистра команд, в регистр адреса ОЗУ и т. д.

Дешифратор 6 - специальный микропрограммный дешифратор, управляется выходными сигналами триггеров регистра операций, входящего в состав регистра команд 5, по каналу 12 и выходными сигналами регистра микроопераций 7 по каналу 15. Назначение дешифратора 6 заключается в выборке соответствующей горизонтальной шины в матрице 8 но каналу 14. При этом выполняется соответствующая микрокоманда (набор микроопераций).

Регистр микроопераций 7 предназначен для запоминания кода, выполняемого в каждый данный момент приказа микропрограммы (микрокоманды), т. е. кода, обозначающего совокунность выполняемых в данный момент микроопераций. Установка на регистре кода соответствующей микрокоманды осуществляется сигналом, поступающим из матрицы 8 по каналу 17.

Матрица 8 обычно состоит из двух матриц, назначение которых состоит в выработке полного набора микроопераций, обеспечивающих работу различных устройств машины. По каналу 18 поступают микрооперации, управляющие работой арифметического устройства 9. По каналу 16 поступает сигнал микроопераций, увеличивающий состояние счетчика команд 4 на единицу (при естественном порядке следования команд). По каналу 20 поступает сигнал микрооперации, осуществляющий управление блоком 10 формирования последовательности констант.

Арифметический блок 9 предназначен для выполнения арифметических операций над кодами операндов, которые поступают в АУ по каналу 23 из ОЗУ и по каналу 21 из блока формирования последовательности констант. По каналу 19 сигналы обратной связи поступают в матрицу 8.

Блок 10 формирования последовательности констант представляет собой автомат с памятью некоторого специального вида, вынолняющий функции не хранения, а формирования постоянной, не изменяемой в процессе вычисления определенного класса задач информации. Формирование этой информации осуществляется определенными «порциями, зависящими от способа построения блока формирования констант. По своему функциональному цазначению он выполняет

функции постоянного запоминающего устройства, однако этот блок песет в себе отличительные признаки, определяемые способом его построения. Эти признаки касаются как схемных отличий и при1щипов работы, так и принципов использования его в устройстве микропрограммного управления в целом.

В основу построения блока формирования последовательности констант автомата ноложен следующий нринцин.

Фиксируется определенная последовательность констант. При этом константа с номером «i всегда следует за константой с номером «/-j-l. При последовательном и

поразрядном формировании констант учитывается как число констант и их разрядность, так и разбиение каждой константы на отдельные части (порции), определяемые в свою очередь выбранным способом кодирования.

В зависимости от числа констант, их разрядности и разбиения каждой константы на части определяется число состояний автомата, которое в наиболее общем случае равно сумме разрядов всех констант. Переход автомата из состояния с номером Ui в состояние Ui+i определяется переходом от одного разряда констаиты (группы разрядов) к другому (к другой группе разрядов) и от константы к константе.

Таким образом, каждому состоянию автомата ставится во взаимнооднозначное соответствие определенный разряд (группа разрядов) констаиты и переключение автомата из одного состояния в другое (соседнее)

обеспечивает последовательное поразрядное (или группы разрядов) формирование констант.

Работа предлагаемого устройства микропрограммного управления состоит в следующем.

Пусть, например, необходимо сложить число, хранящееся в ОЗУ машины, с определенной константой, которая получается на выходе блока 10 формирования последовательмости констант. Адрес этой команды сформировался на счетчике команд в результате выполнения какой-либо предыдущей команды. По каналу 3 код адреса требуемой команды со счетчика команд 4 передается в регистр адреса ОЗУ. Данная команда считывается из ОЗУ и по каналу 22 поступает на регистр команд 5. При использовании, например, трехадресной системы команд рабочий цикл устройства микропрограммного управления

состоит в выполнении следующей последовательности команд. По адресу AI считывается код операнда из ОЗУ и но каналу 23 передается на требуемый регистр АУ 9. По адресу AZ хранится код некоторого начального

состояния блока формирования последовательности констант (далее - автомата), передача которого по каналу 13 на автомат приведет к установлению автомата в определенное состояние. В результате этого на

выходах автомата сформируется соответству

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Авторы

Даты

1975-06-25—Публикация

1972-03-06—Подача