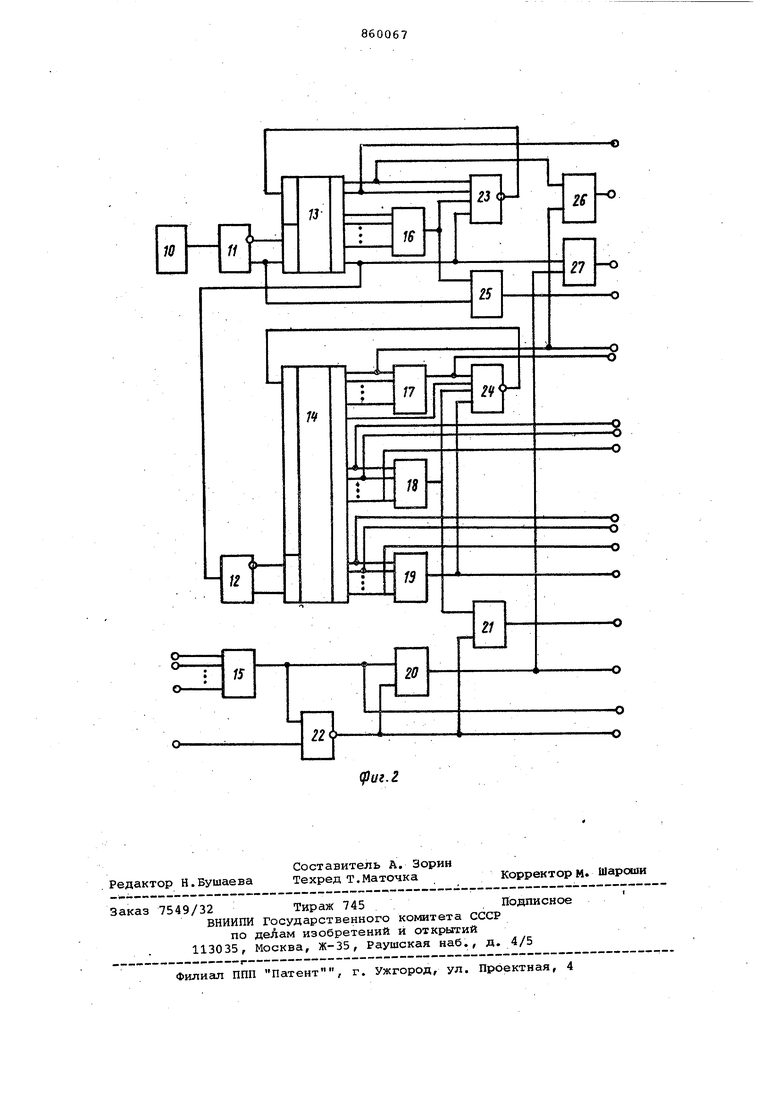

Устройство содержит вход 1 устрой ства, сдвигающий регистр 2, блок 3 управления, дешифратор 4, блок 5 памяти, вспомогательный регистр 6, ком мутатор 7, сумматор 8, регистр 9 результата. Блок 3 управления содержит генерс тор 10 импульсов, элементы НЕ 11 и 12, регистры 13 и 14, элементы ИЛИ :15-21, элементы ИЛИ-НЕ 22-24, элеЫенты И 25-27. Устройство работает следующим образом. ; Логарифмируемое число N записывается в сдвигающий регистр 2 так, что на его первых п выходах представ лога лены разряды с весом 2 рифмируемого числа, а на остальных т+К выходах - разряды с весом , . . . Логарифмирован11е производится за несколько этапов по формуле я;±М1од 2 + 1 од .(1 од Х - о9аХ ) X . На первом этапе производится сдви логарифмируемого числа на соответствующее число двоичных разрядов с целью приведения этого числа к виду J., л .... а уу. .... в .... к При этом по сигналу блока 3 управ ления дешифратор 4 выдает на блок 5 памяти код, в соответствии с которым с выходов блока памяти во вспомогательный регистр б записывается число logа 2 и суммируется в сумматоре 8 столько раз, на сколько разрядов про изведен сдвиг числа. Результат заносится в регистр 9 результата со знаком плюс, если сдвиг производится в сторону уменьшения, и со знаком минус, если сдвиг производился в сто рону увеличения, так как сумматор обладает возможностью переключаться из режима суммирования в режим вычитания по командам блока управления. На втором этапе по сигналу блока 3 управления дешифратор 4 производит дешифрирование числа а ... ау„ представленного на выходах регистра В результате с блока 5 на регистр 6записывается число log 1, а . ..а так как блок памяти представляет собой набор многовходовых элементов ИЛИ, сформированных так, что каждый выход дешифратора однозначно набирает на выходе блока памяти в двоичном коде логарифмы чисел 1 до дискретностью изменения входного чис ла 2. На втором этапе через коммутатор 7производится поочередное подключение выходов регистра б к сумматору при этом подключаются только те выходы регистра 6, которым соответствует логическая единица на последних к выходах сдвигающего регистра 2. Сумматор переключается из режима сложения в режим вычитания таким образом, что по окончании второго этапа в регистре 9 результата будет записано число +М1од 2 + log Х - Ь. . . . Ь В течение третьего этапа по сигналу блока 3 управления производится переключение в дешифраторе 4 так, что на выходе дешифратора появляется код, соответствующий дешифрированию числа а Эд.. . 4- 1 , и на регистр 6 с блока 5 памяти выдается i где X 2 Х + 2 Так же, как и на втором, на третьем этапе производится поочередное подключение выходов регистра б в зависимости от значений последних (к) разрядов сдвигающего регистра 2 ко входу, сумматора 8. По окончании третьего этапа в регистре 9 результата будет записано число +М1од 2 + + )Х XuXftJlog N. Устройство дает возможность вычислять значения логарифмов при любом основании. Испытанный макет для случая п 16, m 5, к 7 имеет следующие характеристики: погрешность вычисления логарифмов по основанию а 10 во всем диапазоне входных чисел 0-3-КГ быстродействие 5-6 мс для тактовой частоты 100 кГц. Формула изобретения 1. Устройство для вычисления логарифма числа, содержащее сдвиговый регистр, дешифратор, блок памяти, регистр результата и сумматор, причемвход устройства соединен с входом сдвигового регистра, первая группа выходов которого подключена к входам дешифратора, выходы которого соединены со входами блока памяти, о т л и ч а ю щ е е ся тем, что, с целью расширения функциональных возможностей за счет вычисления логарифма число по произвольному основанию, в него введены вспомогательный регистр, коммутатор и блок управления, причем вторая группа выходов сдвигового регистра подключена к входам блока управления, выходы которого подключены к управляющим входам сдвигового регистра, дешифратора, вспомогательного регистра, коммутатора, сумматора- и регистра результата, выходы блока памяти через вспомогательный регистр подключены к первой группе входов коммутатора, вторая группа входов которого соединена с третьей группой выходов сдвигающего регистра, выход коммутатора соединен с первым входом сумматора, второй вход кото рого подключен к выходу регистра р зультата, вход которого соединен с выходом сумматора. 2. Устройство по п.1, о т л и чающееся тем, что блок упр ления содержит генератор импульсов два инвертора, семь элементов ИЛИ, два регистра , три элемента ИЛИ-НЕ и три элемента И, причем выход генератора импульсов через первый элеме НЕ соединен с первым и вторым входами первого регистра, выходы которого соединены с входами первого эл мента ИЛИ, выход которого соединен первыми входами первого элемента И и первого .элемента ИЛИ-НЕ, второй и третий входы которого соединены с первым и вторым выходами первого регистра, четвертый вход и выход первого элемента ИЛИ-НЕ соединены соответственно с третьими выходом и входом первого регистра, второй вход первого элемента и соединен с прямым выходом первого элемента НЕ, третий выход первого регистра через второй элемент НЕ соединен с первым и вторым входами второго регистра,первая, вторая и третья группы выходов которого через второй,третий и четвер тый элементы ИЛИ соответственно под ключены к первому, второму и третье му входам второго элемента ИЛИ-НЕ, четвертый вход которого соединен с выходом второго регистра, выход вто рого элемента ИЛИ-НЕ соединен с третьим входом второго регистра,вхо ды пятого элемента ИЛИ соединены с входами блока управления, выход пятого элемента ИЛИ соединен с первым входами шестого элемента ИЛИ и трет его элемента ИЛ.1-НЕ, вторые входы которых соединены соответственно с выходом третьего элемента ИЛИ-НЕ и входом устройства, выход шестого элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого соединен с третьим выходом первого регистра, входы третьего элемента И соединены соответственно с первыми выходами первого и второго регистров, входа седьмого элемента ИЛИ соединены с выходами соответственно третьего элемента ИЛИ-НЕ и третьего элемента ИЛИ, второй выход первого регистра соединен с первым управляющим входом вспомогательного регистра, второй управляющий вход которого и управляющий вход регистра результата соединены с выходом первого элемента И, выходы второго и третьего элементов И соединены с первым и вторым управляющими входами сдвигового регистра, первый выход второго регистра и выход седьмого элемента ИЛИ подключены к первому и второму управляющим входам сумматора, выход второго элемента ИЛИ соединен с управляющим входом дешифратора, выходы второй и третьей групп подключены к управляющим входам коммутатора, выход шестого элемента ИЛИ соединен с управлякицим входом блока памяти, выходы пятого элемента ИЛИ и третьего элемента ИЛИ-НЕ подключены к третьему и четвертому управляющим входам сдвигового регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 489112, кл. G 06 F 15/20, 1974. 2.Авторское свидетельство СССР №624233, кл, G 06 F 15/20, 1978 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмирующее устройство | 1976 |

|

SU634272A1 |

| Устройство для логарифмирования чисел | 1980 |

|

SU926655A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Устройство для вычисления логарифма | 1978 |

|

SU744560A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

Авторы

Даты

1981-08-30—Публикация

1979-09-13—Подача