12

& ел

ЬО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования и контроля управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки | 1986 |

|

SU1451676A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

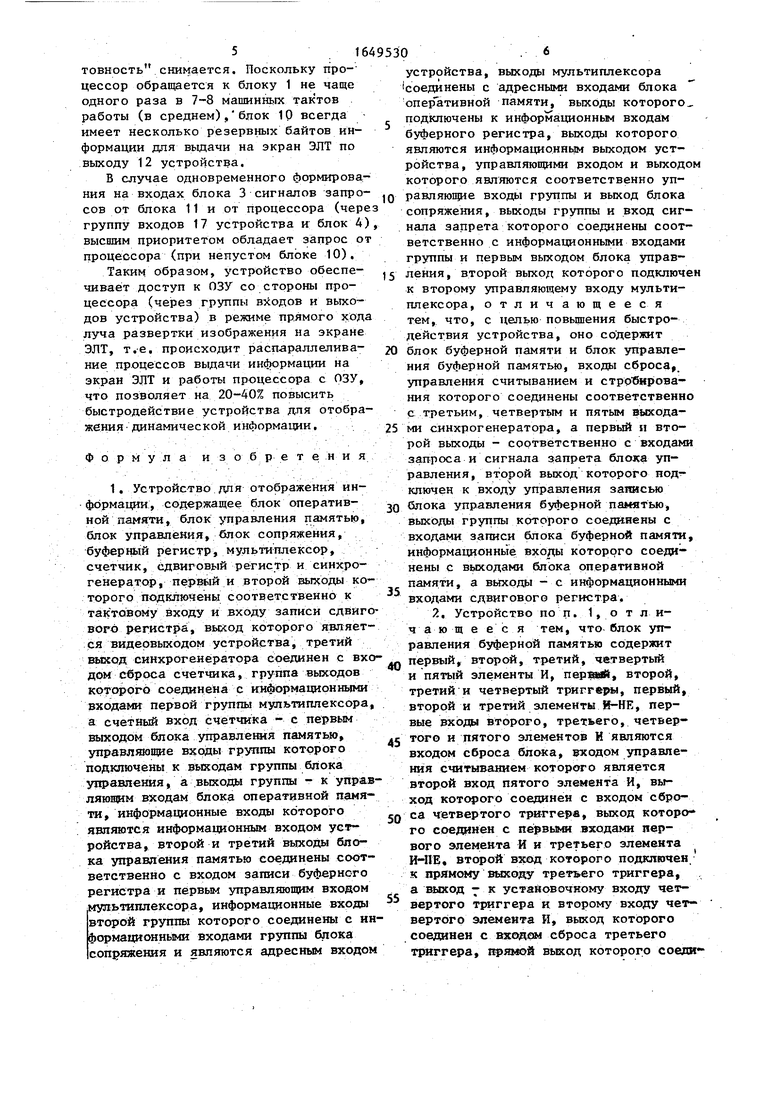

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах вывода микроЭВМ для отображения алфавитно-цифровой и графической информации на экране электронно-лучевой трубки (ЭЛТ). Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 оперативной памяти, блок 2 управления памятью, блок 3 управления, блок 4 сопряжения, синхро- генератор 5, буферный регистр 6, мультиплексор 7, счетчик 8, сдвиговый регистр 9, блок 10 буферной памяти, блок 11 управления буферной памятью с соответствующими связями. Введение блоков 10 и 11 позволяет распараллелить запись и считывание изображения и повысить быстродействие устройства при отображении динамической информации. 1 з.п.ф-лы, 2 ил.

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть, использовано в устройствах вывода микроЭВМ для отображения алфа- витно-цифровой и графической информации на экране электронно-лучевой трубки (ЭЛТ).

Цель изобретения - повышение быстродействия устройства.

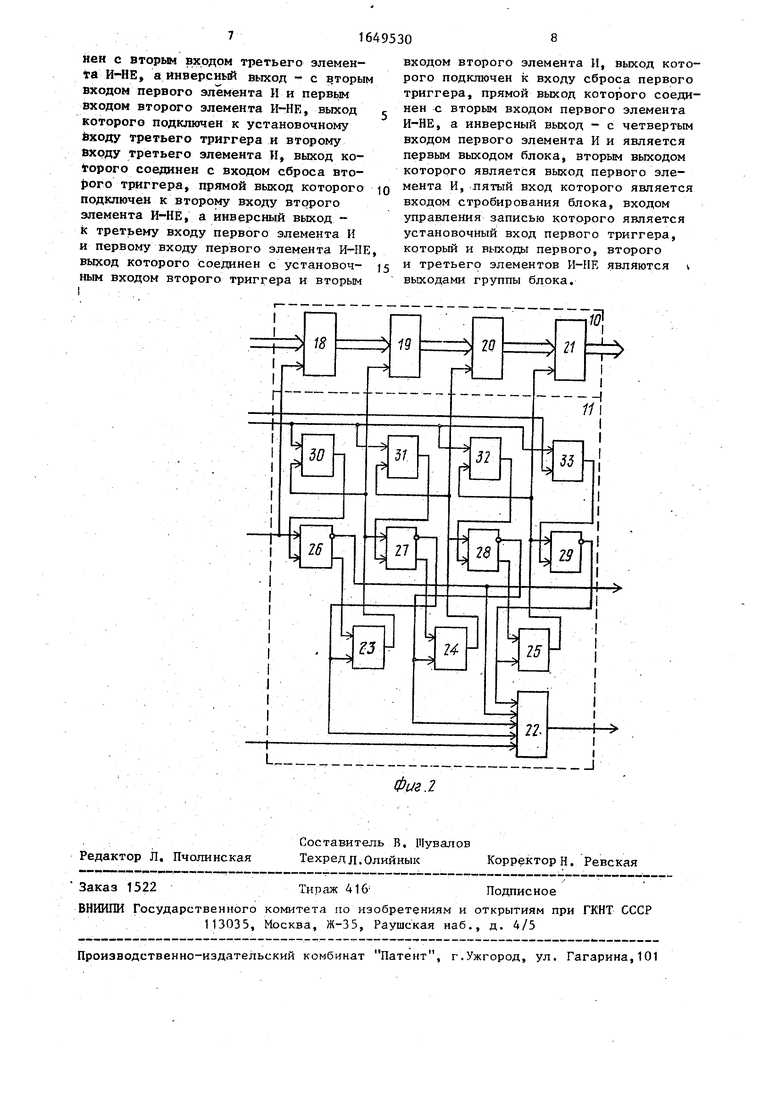

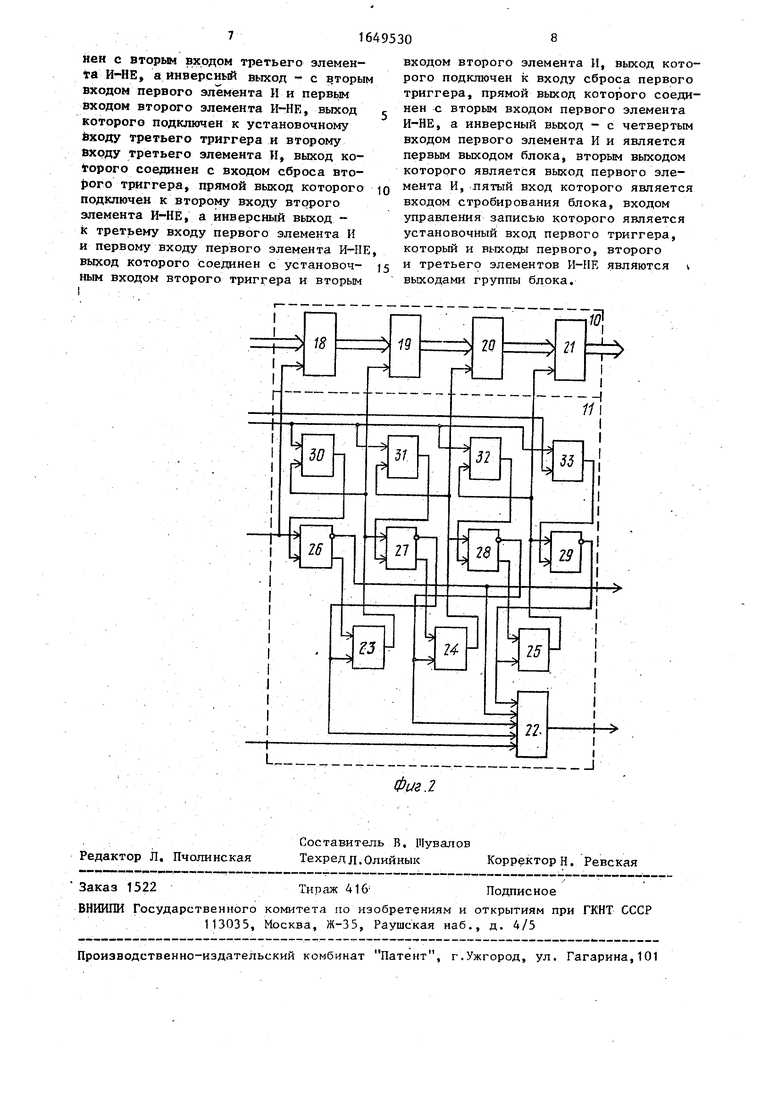

На фиг, 1 приведена блок-схема устройства для отображения информации на фиг. 2 - структурные схемы блока управления буферной памятью и блока буферной памяти.

Устройство для отображения информации содержит блок 1 оперативной памяти, блок 2 управления памятью, блок 3 управления, блок 4 сопряжения, синхрогенератор 5, буферный регистр 6 мультиплексор 7, счетчик 8, сдвиговый регистр 9, блок 10 буферной памяти и блок 11 управления буферной памятью

Позициями 12-17 обозначены входы и выходы устройства.

Блок 10 буферной памяти состоит из первого 18, второго 19, третьего 20 и четвертого 21 регистров.

Блок 11 управления буферной памятью содержит первый элемент И 22, первый 23, второй 24 и третий 25 элементы g-HE, первый 26, второй 27, третий 28 и четвертый 29 триггеры, второй 30, третий 31, четвертый 32 и пятый 33 элементы И,

Устройство работает следующим образом.

При включении устройства на третьем выходе синхрогенератора 5 форми- руется сигнал, устанавливающий на выходах счетчика 8 адрес первого считываемого из блока 1 на экран ЭЛТ байта информации, а на выходах блока 11 состояние незаполненного информацией блока 10. Сигнал Запрос на первом выходе блока 11, возникающий в результате незаполненного состояния младшей ячейки (регистра 18) блока 10, принимается для обслуживания блоком 2 На втором выходе блока 3 и третьем выходе блока 2 формируются сигналы Разрешение, которые переключают мультиплексор 7 на передачу содержимого счетчика 8 на группу адресных входов блока 1. Байт информации из блока 1 пересыпается в младшую ячейку блока 10, а содержимое счетчика 8 сигналом с первого выхода блока 2 увели

5

0

5

.Q

5

чивается на единицу. Сигналами на группе выходов блока 11 принятый в младшую ячейку блока 10 байт пересы- лается в старшую незаполненную ячейку блока 10 (в данном случае в регистр 21). На первом выходе блока 11 последовательно формируются сигналы Запрос, по которым аналогично происходит дальнейшее заполнение информацией блока 10.

По сигналам на втором и четвертом выходах синхрогенератора 5 производится перезапись содержимого старшего байта блока 10 в сдвиговый регистр 9. На группе выходов блока 11 формируются управляющие сигналы, обеспечивающие побайтный сдвиг содержимого блока 10 от младшей ячейки к старшей с одновременным освобождением младшей ячейки Синхроимпульсами, поступающими Не 1ход сдвигового регистра 9 с первого ыхода синхрогенератора 5, производится побитный вывод записанного в регистр 9 байта информации на выход 12 устройства для регенерации изображения . На первом выходе блока 11 формируется сигнал Запрос, по которому в случае отсутствия запроса от процессора производится заполнение информацией освободившейся ячейки блока 10. Если же на группе входов блока 3 присутствует запрос на обращение к блоку 1 со стороны процессора, то сигналами с выходов блоков 2 иЗ мультиплексор 7 переключается на передачу информации с группы адресных входов 14 устройства на группу адресных входов блока 1, а через группу входов 13 или группу выходов 17 производится заг пись или считывание информации из блока 1 .В это время сигнал Запрос от блока 11 не обслуживается, а сдвиговый регистр 9 заполняется информацией из ячеек блока 10. После снятия запроса на обращение к блоку 1 со стороны процессора обслуживаются запросы со стороны блока 11 и производится доза- полнение блока 10 информацией по описанной схеме.

Если блок 10 пуст, а запрос со стороны процессора присутствует, то на втором выходе блока 11 формируется сигнал, который через блок 3 и блок 4 на один такт работы устройства блоки- , рует сигнал Готовность на управляющем выходе 16 устройства. В это время происходит заполнение младшей ячейки блока 10 и блокировка сигнала Готонкость снимается. Поскольку процессор обращается к блоку 1 не чаще одного раза в 7-8 машинных тактов работы (в среднем), блок 10 всегда имеет несколько резервных байтов информации для выдачи на экран ЭЛТ по выходу 12 устройства.

В случае одновременного формирования на входах блока 3 сигналов запросов от блока 11 и от процессора (чере группу входов 17 устройства и блок 4) высшим приоритетом обладает запрос от процессора (при непустом блоке 10).

Таким образом, устройство обеспечивает доступ к ОЗУ со стороны процессора (через группы входов и выходов устройства) в режиме прямого хода луча развертки изображения на экране ЭЛТ, т.е. происходит распараллеливание процессов выдачи информации на экран ЭЛТ и работы процессора с ОЗУ, что позволяет на 20-40% повысить быстродействие устройства для отображения динамической информации.

Формула изобретения

выход синхрогенератора соединен с вхо- первый, второй, третий, четвертый

дом сброса счетчика, группа выходов которого соединена с информационными входами первой группы мультиплексора, а счетный вход счетчика - с первым выходом блока управления памятью, управляющие входы группы которого подключены к выходам группы блока управления, а выходы группы - к управляющим входам блока оперативной памяти, информационные входы которого являются информационным входом устройства, второй и третий выходы блока управления памятью соединены соответственно с входом записи буферного регистра и первым управляющим входом ,мультиплексора, информационные входы второй группы которого соединены с информационными входами группы блока сопряжения и являются адресным входом

45

50

55

и пятый элементы И, первый, второй третий и четвертый триггеры, первы второй и третий элементы Й-НЕ, пер вые входы второго, третьего, четв того и пятого элементов И являются входом сброса блока, входом управл ния считыванием которого является второй вход пятого элемента И, выход которого соединен с входом сбр са четвертого триггера, выход кото го соединен с первыми входами первого элемента И и третьего элемент И-НЕ, второй вход которого подключ к прямому выходу третьего триггера а выход - к установочному входу че вертого триггера и второму входу ч вертого элемента И, выход которого соединен с входом сброса третьего триггера, прямой выход которого со

0

5

0

5

устройства, выходы мультиплексора соединены с адресными входами блока оперативной памяти, выходы которого, подключены к информационным входам буферного регистра, выходы которого являются информационным выходом устройства, управляющими входом и выходом которого являются соответственно управляющие входы группы и выход блока сопряжения, выходы группы и вход сигнала запрета которого соединены соответственно с информационными входами группы и первым выходом блока управления, второй выход которого подключен к второму управляющему входу мультиплексора, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок буферной памяти и блок управления буферной памятью, входы сброса,, управления считыванием и строВнрова- ния которого соединены соответственно с третьим, четвертым и пятым выходами синхрогенератора, а первый и второй выходы - соответственно с входами запроса и сигнала запрета блока управления, второй выход которого подключен к входу управления записью блока управления буферной памятью, выходы группы которого соединены с входами записи блока буферной памяти, информационные входы которого соединены с выходами блока оперативной памяти, а выходы - с информационными входами сдвигового регистра.

2, Устройство по п. отличающееся тем, что блок управления буферной память содержит

первый, второй, третий, четвертый

и пятый элементы И, первый, второй, третий и четвертый триггеры, первый, второй и третий элементы Й-НЕ, первые входы второго, третьего, четвертого и пятого элементов И являются входом сброса блока, входом управления считыванием которого является второй вход пятого элемента И, выход которого соединен с входом сброса четвертого триггера, выход которого соединен с первыми входами первого элемента И и третьего элемента И-НЕ, второй вход которого подключен к прямому выходу третьего триггера, а выход - к установочному входу четвертого триггера и второму входу четвертого элемента И, выход которого соединен с входом сброса третьего триггера, прямой выход которого соеди нен с вторым входом третьего элемента И-НЕ, а инверсный выход - с вторы входом первого элемента И и первым входом второго элемента И-НЕ, выход которого подключен к установочному входу третьего триггера и второму входу третьего элемента И, выход которого соединен с входом сброса второго триггера, прямой выход которого подключен к второму входу второго элемента И-НЕ, а инверсный выход - к третьему входу первого элемента И и первому входу первого элемента И-Н выход которого соединен с установоч- ным входом второго триггера и вторым

входом второго элемента И, выход которого подключен к входу сброса первого триггера, прямой выход которого соединен с вторым входом первого элемента И-НЕ, а инверсный выход - с четвертым входом первого элемента И и является первым выходом блока, вторым выходом которого является выход первого элемента И, пятый вход которого является входом стробирования блока, входом управления записью которого является установочный вход первого триггера, который и выходы первого, второго и третьего элементов И-HR являются v выходами группы блока.

| Микропроцессорные средства и системы, 1986, № 1 , с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1991-05-15—Публикация

1988-12-26—Подача