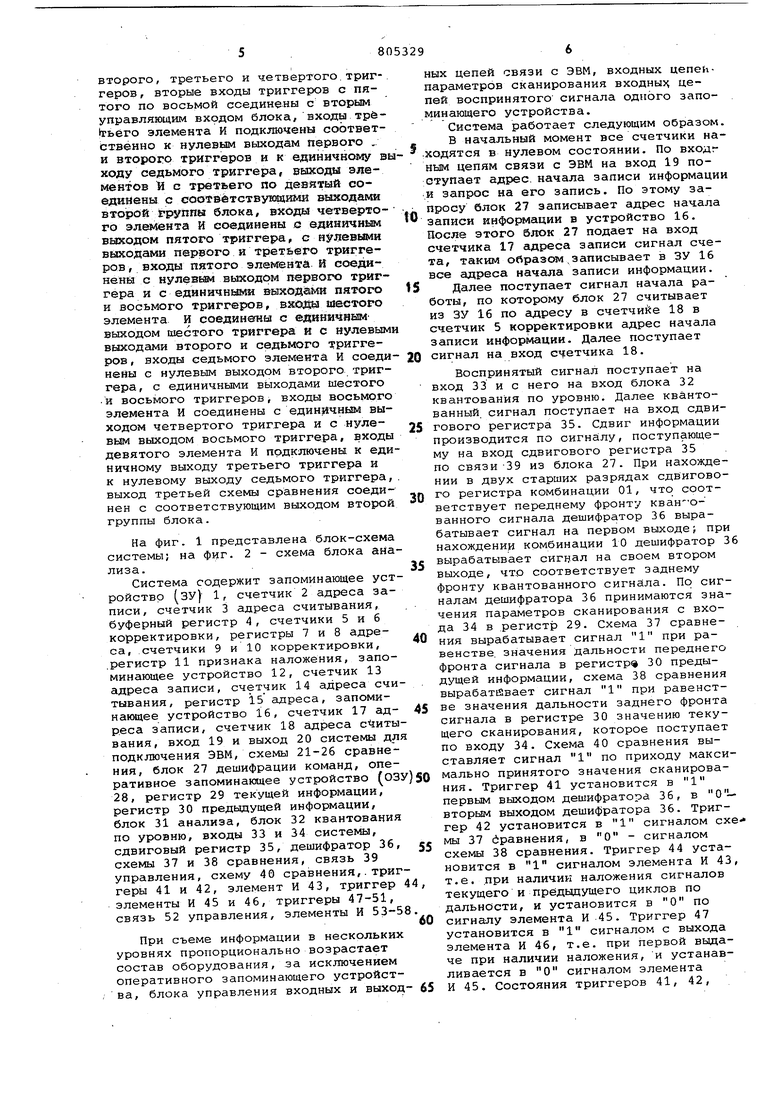

Изобретение относится к вычислительной технике и может быть использовано для первичной обработки радио локационной и другой развертываемой во времени информации. : Известно устройство первичной обработки радиолокационной информации, которое содержит блок квантования сигналов по уровню, блок кодирования временных задержек и цифровую вычислительную машину, содержащую буферно запоминающее устройство, оперативное запоминающее устройство, арифметическое устройство и устройство управ ления 1 . Однако значи лую часть информации хранит только один цикл, группирование информации в пачки при слиянии целей (изображений) и при наличии по мехи может содержать ошибку, быстродействие устройства ограничено .быстродействием арифметического устройст ва.. Наиболее близкой по технической сущности к изобретению является система, которая содержит ЭВМ, буферное запоминающее устройство, .связанное с ocHOBHbiM запоминайвдим устройством, в которое записываются как входные данные, так и результаты предварител ных вычислений в схеме для перемножения векторов. Входные аналоговые сигналы преобразуются в цифровой код с .помощью аналого-цифрового преобразователя. Система предназначена для обработки сигналов, образованных при радиолокационных измерениях 2j . Недостатки системы состоят в-.том, что значимую информацию она хранит только один цикл. Подборка информации в пачки при слиянии целей (изображений) и при наличии помехи может содержать ошибку. Общее быстродействие ограничивается быстродействием узлов арифметической обработки. Цель изобретения - повЕлаение быстродействия и достоверности работы. Поставленная цель достигается тем, что в систему, содержащую регистры текущей инфоря ации и предыдущей информации, блок квантования по уровню, вход которого является первым входом системы, оперативное запоминаклдее устройство и блок дешифрации команд, введейы запоминающие устройства, счетчйки адреса записи, счетчики адреса считывания, буферные регистры, счетчики корректировки, регистр признака наложения, схемы сравнения, регистры адреса и блок анализа, причем адресные входы каждого запоминаю щего .устройства соединены с первыми выходами соответствующих счетчика ад реса записи и счетчика адреса считывания, второй выход каждого счетчика адреса записи, кроме первого, через буферный регистр соединен с адресным входом запоминающего устройства, вход первого запоминающего устройства, первые входы оперативного запоми нающего устройства и блока дешифрации команд подключены к второму входу системы, управляющие входы счетчи ков адреса записи, адреса считывания буферных регистров и запоминающих устройств соединены, с первым выходом блока дешифрации команд, выходы запоминающих устройств, кроме первого, .подключены к входам первого и второго счетчиков корректировки и к входу регистра признака наложения, выход первого запоминающего устройства соединен с входом третьего счетчика ко ректировки, входы запоминающих устройств, кроме первого, соединены с первыми выходами третьего и четвертого счетчиков корректировки, первого и второго регистров адреса, входы первого регистра адреса соединены со ответственно с первыми выходами первого и второго счетчиков корректиров ки, с вторым выходом третьего счетчи ка корректировки и с вторым входом оперативного запоминающего устройства, второй выход первого регистра ад реса, первый выход оперативного запо минающего устройства и второй выход блока дешифрации команд соединены с выходом системы, вход второго регист ра адреса соединен с третьим выходом первого регистра адреса, четвертый выход которого и вторые выходы второ го регистра адреса и четвертого счетчика корректировки подключены к третьему входу оперативного запоминающего устройства, четвертый вход которого соединен с выходом регистра текущей информации, второй выход подключен к входу регистра предыдущей информации, третий выход тре,тьего счетчика корректировки подключен к первому входу четвертого счетчика кор ректировки, второй вход которого подключен к третьему выходу второго регистра адреса, первые входы первой второй и третьей схем сравнения подключены соответственно к первому и второму выходам регистра признака наложения и к третьему выходу четвертого счетчика корректировки, вторые, входы первой и второй схем сравнения подключены соответственно к вторым выходам второго и первого счетчиков корректировки, третий выход регистра признака наложения соединен с вторым входом блока дешифрации команд, входы которого, начиная с третьего, подключены соответственно к выходам схем сравнения с первой по шестую, входы. четвертой схемы сравнения соединены с вторыми выходами первых счетчиков адреса записи и адреса считывания, входы пятой схемы сравнения соединены с третьим выходом второго счетчика адреса записи и с вторым выходом треттьего счетчика адреса считывания, входы шестой схемы сравнения соединены с вторым выходом второго счетчика адреса считывания и с третьим выходом третьего счетчика адреса записи, управляющие входы счетчиков корректировки, регистров адреса, оперативного запоминающего устройства и регистра предыдущей информации соединены с третьим выходом блока дешифраций команд, четвертый и пятый выходы которого подключены соответственно к первому и второму управляющим входам блока анализа, первый и второй входы которого соединены соответственно с выходами регистра предыдущей информации и блока квантования по уровню, . третий вход блока анализа и вход регистра текущей информации соединены с третьим входом системы, выходы первой и второй групп блока анализа соединены соответственно с группами входом регистра текущей информации и блока дешифрации команд. Кроме того, в системе блок анализа содержит триггеры, элементы И, сдвиговый регистр, дешифратор и схемы сравнения, первые входы которых соединены с третьим входом блока, вторые входы первой и второй схем сравнения подключены к первому входу блока, третьи входы первой и второй схем сравнения и первый вход сдвигового регистра соединены с первым управляющим входом блока, второй вход сдвигового регистра подключен к второму входу блока, выход сдвигового регистра соединен с входом дешифратора, выходы которого являются первой группой выходов блока, -единичный вход первого триггера соединен с первым выходом дешифратора, нулевой вход - с вторым выходом дешифратора, единичный вход второго триггера соединен с выходом первой схемы сравнения, выход второй схемы сравнения подключен к соответствующему выходу второй группы блока и к нулевому входу второго триггера, входы первого элемента И соединены с един 1чнь1ми выходами первого и второго триггеров, выход подключен к единичному входу третьего триггера, входы второго элемента И соединены с вторым выходом дешифратора и с единичньм выходом третьего триггера, выход - подключен к единичному входу четвертого триггера, нулевые входы третьего и четвертого триггеров соединены с выходом третьего элемента И, первые входы пятого, шестого, седьмого и восьмого триггеров соединены соответственно с единичными выходами первого.

второго, третьего и четвертого.триггеров , вторые входы триггеров с пятого по восьмой соединены с вторьвл управляющим входом блока, входы третьего элемента И подключены соответственно к нулевым выходам первого ,. и второго триггеров и к единичному выходу седьмого триггера, выходы элеплентов И с третьего по девятый соединены с соответствующими выходами вто1рОй гигппы блока, входы четвертого элемента И соединены о единичным выходом пятого триггера, е ну евьши выходами первого и третьего триггеров , входы пятого элеменфа И соединены с нулевш4 выходом первого триггера и с единичными выходами пятого и восьмого триггеров, вясдаа шесторо элемента И соединены с еяйничиым выходом шестого триггера и с нулевыми выходами второго и седьмого триггеров , входы седьмого элемента И соединены с нулевым выходом второго триггера, с единичными выходами шестого и восьмого триггеров, входы восьмого элемента И соединены с единИ1чным выходом четвертого триггера и с нулевым выходом восьмого триггера, входы девятого элемента И подключены к единичному выходу третьего триггера и к нулевому выходу седьмого триггера, выход третьей схемы сравнения соединен с соответствующим выходом второй группы блока.

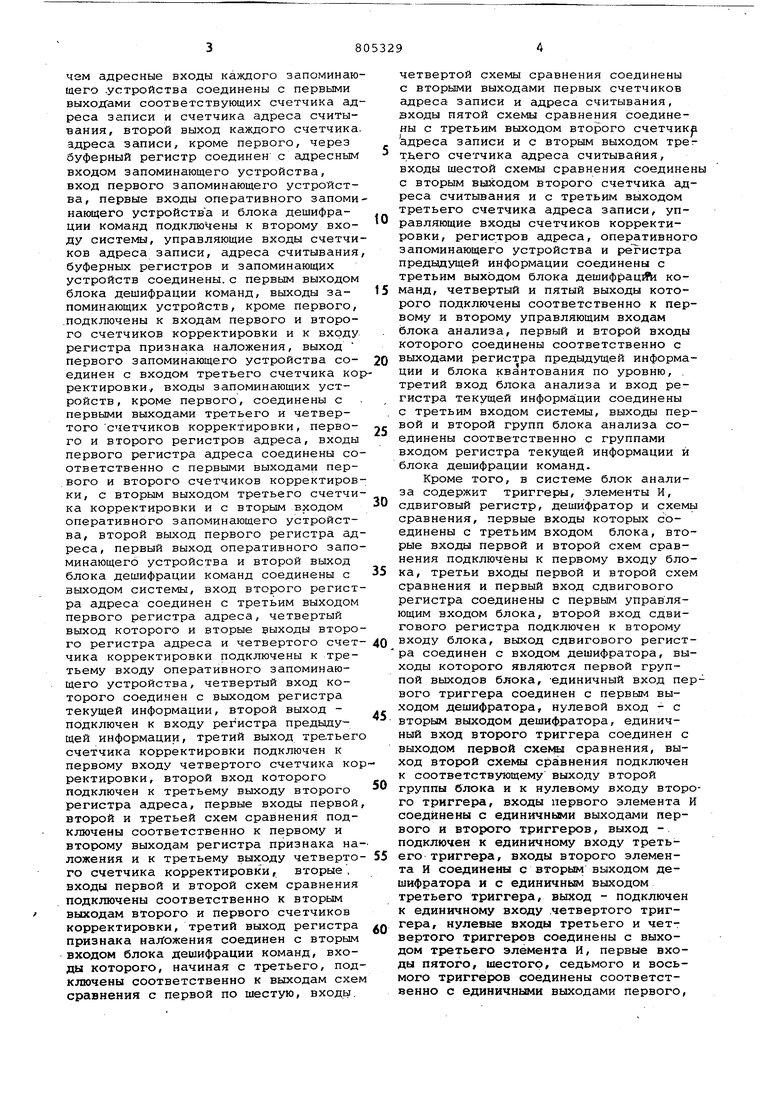

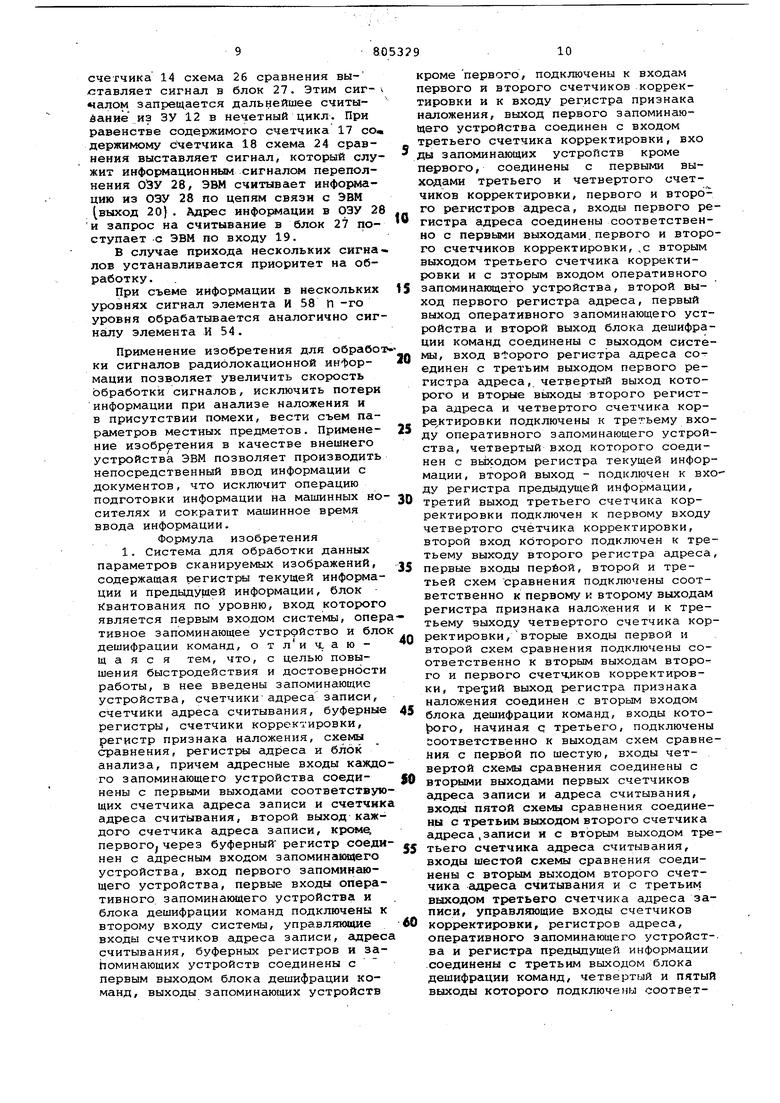

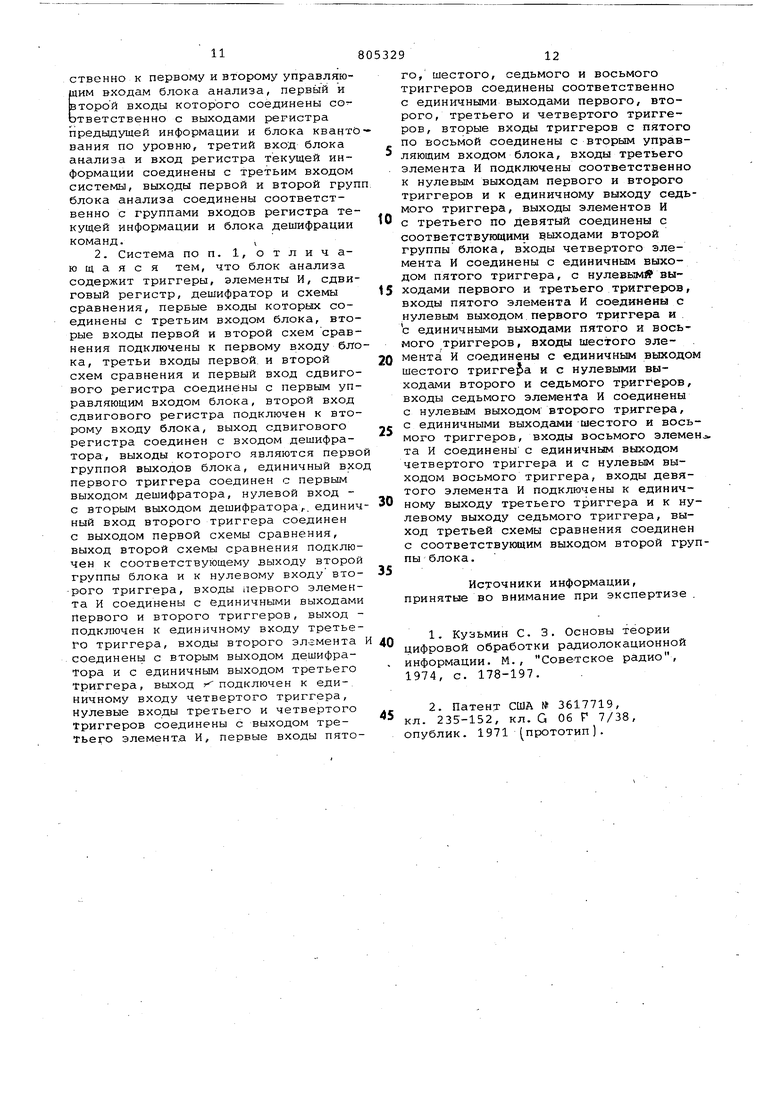

На фиг, 1 представлена блок-схема системы; на фиг. 2 - схема блока анализа.

Система содержит запоминающее устройство (ЗУ) 1, счетчик 2 адреса записи, счетчик 3 адреса считывания, буферный регистр 4, счетчики 5 и 6 корректировки, регистры 7 и 8 адреса, счетчики 9 и 10 корректировки, .регистр 11 признака наложения, запоминающее устройство 12, счетчик 13 адреса записи, счетчик 14 адреса считывания, регистр 15 адреса, запоминающее устройство 16, счетчик 17 адреса записи, счетчик 18 адреса с гитывания, вход 19 и выход 20 системы для подключения ЭВМ, схемы 21-26 сравнения, блок 27 дешифрации команд, оперативное запоминающее устройство (ОЗУ 28, регистр 29 текущей информации, регистр 30 предыдущей информации, блок 31 анализа, блок 32 квантования по уровню, входы 33 и 34 системы, сдвиговый регистр 35, дешифратор 36, схемы 37 и 38 сравнения, связь 39 управления, схему 40 сравнения,.триггеры 41 и 42, элемент И 43, триггер 4 элементы И 45 и 46, триггеры 47-51, связь 52 управления, элементы И 53-58

При съеме информации в нескольких уровнях пропорционально возрастает состав оборудования, за исключением оперативного запоминающего устройства, блока управления входных и выходных цепей связи с ЭВМ, входных цепейпараметров сканирования входных Цепей воспринятого сигнала одного запоминающего устройства.

Система работает следующим образом

В начальный момент все счетчики на.ходятся в нулевом состоянии. По входг ным цепям связи с ЭВМ на вход 19 поступает адрес, начала записи информаци и запрос на его запись. По этому запросу блок 27 записывает адрес начала записи инфОЕ 1ации в устройство 16. После этого блок 27 подает на вход счетчика 17 адреса записи сигнал счета, таким ойразсяи, записывает в ЗУ 16 все адреса начала записи информации.

Далее поступает сигнал начала работы, по которому блок 27 считывает из ЗУ 16 по адресу в счетчийе 18 в счетчик 5 корректировки адрес начала записи информации. Далее поступает сигнал на вход счетчика 18.

Воспринятый сигнал поступает на вход 33 и с него на вход блока 32 квантования по уровню. Далее квантованный, сигнал поступает на вход сдвигового регистра 35. Сдвиг информации производится по сигналу, поступающему на вход сдвигового регистра 35 по связи39 из блока 27. При нахождении в двух старших разрядах сдвигового регистра комбинации 01, что соответствует переднему фронту кван ованного сигнала дешифратор 36 вырабатывает сигнал на первом выходе; при нахождении комбинации 10 дешифратор вырабатывает сигнал на своем втором выходе, что соответствует заднему фронту квантованного сигнала. По сигналам дешифратора 36 принимаются значения параметров сканирования с входа 34 в регистр 29. Схема 37 сравнения вырабатывает сигнал 1 при равенстве, значения дальности переднего фронта сигнала в регистр 30 предыдущей информации, схема 38 сравнения вырабатывает сигнал 1 при равенстве значения дальности заднего фронта сигнала в регистре 30 значению текущего сканирования, которое поступает по входу 34. Схема 40 сравнения выставляет сигнал 1 по приходу максимально принятого значения сканирования. Триггер 41 установится в 1 первым выходом дешифратора 36, в О- вторым выходом дешифратора 36. Триггер 42 установится в 1 сигналом сх мы 37 йравнения, в О - сигналом схемы 38 сравнения. Триггер 44 установится в 1 сигналом элемента И 43 т.е. .при наличии наложения сигналов текущего и предыдущего циклов по дальности, и установится в О по сигналу элемента И 45. Триггер 47 установится в 1 сигналом с выхода элемента И 46, т.е. при первой выдаче при наличии наложения, и устанавливается в О сигналом элемента И 45. Состояния триггеров 41, 42,

44 и 47 переписываются соответственн в три-ггеры 48-51 по сигналу синхронизации, поступающему по связи 52 Элементы И 45, 53-58 вырабатывают сигналы наложения. По, сигналу элемента И 53 блок 27 по адресу в счет(чике 5 корректировки записывает в ОЗУ 28 содержимое регистра 29.Далее по адресу в счетчике 2 адреса записи записывает в ЗУ 1 содержимое счетчика 5 корректировки, подает на вход счетчика 2 счетный сигнал. Далее по адресу в счетчике 18 считывает из ЗУ 16 адрес начала записи информации в счетчик 5 корректировки, подает на вход счетчика 18 счетный сигнал. По сигналу схемы сравнения 40 блок 27 меняет четность цикла. Устанавливается четный цикл. При этом установятся в О счетчик 3 и счетчик 13. По ад.ресу в счетчике 3 считывается из ЗУ в счетчик 9 корректировки, счетчик 1 корректировки, регистр 11 признака наложения. Далее прибавляется единицы в счетчик 3, считывается из ОЗУ 28 по адресу в счетчике 9 информация в регистр 30. При равенстве нулю содержимого регистра 11 признак наложения прибавляется единица к содержимому счетчика 9 корректировки и выдается в регистр 7. При равенств единице регистра 11 признака наложения прибавляется единица к содержимому счетчика 10 корректировки и выдается в регистр 7 адреса. Схема 23 сравнения выставит сигнал единица, если содержимое младших, разрядов счетчика 9 корректировки равно максимуму за вычетом единицы и содержимое регистра 11 признака наложения равно О. Схема 22 сравнения выставит сигнал единица, если содержимое младших разрядов счетчика 10 .корректировки равно максимуму за вычетом единицы, а содержимое регистра 11 признака наложения равно единице. Далее по сигналу единица схемы 23 сравнения блок 27 прибавит единицу к содержимому счетчика 9 корректировки. По полученному адресу в ОЗУ 28 записывается содержимое счетчика 5 корректировки и признак зависимости из блока 27. Далее записывается по адресу в счетчике 5 корректировки содержимое счетчика 9 корректировки и признака зависимости из блока 27. Затем прибавляется единица к содержимому счетчика 5 корректировки и передается его содержимое в регистр 7 адреса. Аналогично обрабатывается единичный сигнал схемы 22 сравнения. По сигналу элемента И 58 блок 27 передает содержимое регистра 7 адреса в регистр 8 адреса. По сигналу элемента И 57 блок 27 по адресу в регистре 8 записывает в ОЗУ 28 содержимое регистра 29 текущей информации} передает содержимое регистра 8 адреса з счетчик б корректировки, записывает

в ЗУ 12 по адресу в счетчике 13 содержимое регистра 8 адреса передает содержимое счетчика 13 в буферный регистр 15, прибавляет единицу к содержимому счетчика 13, вьщает следующую информацию за предыдущий цикл в 5 регистр 7 адреса и регистр 30 предьщущей информации. По сигналу элемента И 56 в присутствии сигнала схемы 38 сравнения блок 27 прибавляет единицу к содержимому счетчика 6 корректировки, по полученному адресу записывает содержимо е регистра 7 адреса и признака зависимости из блока.27 в ОЗУ 28; далее записывает по адресу в регистре 7 адреса содержимое с тчи5 ка 6 корректировки и признак зависимости из блока 27 в ОЗУ 28. Схема 21 сравнения выставит сигнал единица, если обнаружит в младших разрядах номер, равный максимуму.минус ёдини0 ца. По этому сигналу блок 27 прибавляет единицу в счетчик б корректировки, по полученному адресу записывает содержимое счетчика 5 корректировки в ОЗУ 28 и признак зависимости из блока 27, далее по адресу в счетчике 5 корректировки записывает содержимое счетчика б корректировки и признак зависимости из блока 27 в ОЗУ 28. Содержимое счетчика 5 корректировки затем пересылается в счетчик 6 корректировки,.считывается следующий адрес начала записи информации из ЗУ 16 в счетчик 5 корректировки. По сигналу элемента И 54 блок 27 прибавляет единицу к содержимому счетчика б корректировки, производит запись взаимной зависимости содержимого счетчика 6 корректировки и счетчи-ка 5 корректировки в ОЗУ 28, далее прибавляет единицу к содержимому

0 счетчика 5 корректировки, по полученному адресу записывает в ОЗУ 28 - содержимое регистра 29, записывает в ЗУ 12 очередность поступления адреса из счетчика 5 корректировки. Далее

из ЗУ 16 считывается следующий адрес

анат}иза в счетчик 5 корректировки. По сигналу элемента И 55 блок 27 выставляет запрос на обслуживание от ЭВМ и выдает на выходные цепи связи с ЭВМ содержимое регистра 7 адреса.

Далее блок 27 засылает в регистр 7 адреса и регистр 30 очередную информацию. По сигналу схемы 38 сравнения засылается очередная информация в регистр 7 адреса и в регистр 30. По

5 сигналу элемента И 45 блок 27 записывает по адресу в буферном регистре 15 в ЗУ 12 содержимое регистра 8 адреса, счетчика 6 корректировки и признак зависимости из блока 27. При

равенстве содержимого счетчика 3 и счетчика 13 схема 25 сравнения посылает сигнал в блок 27. Этим сигналам запрещается дальнейшее считывание из ЗУ 1 в четный цикл. При равенстве ... содержимого счетчика 2 содержимом . счетчика 14 схема 26 сравнения выдтавляет сигнал в блок 27. Этим сиг«чалом запрещается дальнейшее считывание из ЗУ 12 в нечетный цикл. При равенстве содержимого счетчика 17 со держимому сметчика 18 схема 24 сравнения выставляет сигнал, который слу жит информационным сигналом переполнения ОЗУ 28, ЭВМ считывает информацию из ОЗУ 28 по цепям связи с ЭВМ выход 20), Адрес информации в ОЗУ 2 и запрос на считывание в блок 27 поступает с ЭВМ по входу 19. В случае прихода нескольких сигна лов устанавливается приоритет на обработку. При съеме информации в нескольких уровнях сигнал элемента И 58 п -го уровня обрабатывается аналогично сиг налу элемента И 54. Применение изобретения для обрабо ки сигналов радиолокационной информации позволяет увеличить скорость обработки сигналов, исключить потери информации при анализе наложения и в присутствии помехи/ вести съем параметров местных предметов. Применение изобретения в качестве внешнего устройства ЭВМ позволяет производить непосредственный ввод информации с документов, что исключит операцию подготовки информации на машинных но сителях и сократит машинное ввода информации. Формула изобретения 1. Система для обработки данных параметров сканируемых изображений, содержащая регистры текущей информации и предыдущей информации, блок Квантования по уровню, вход которого является первым входом системы, опер тивное запоминающее устройство и бло дешифрации команд, отлич,ающ а я с я тем, что, с целью повышения быстродействия и достоверности работы, в нее введены запоминающие устройства, счетчики адреса записи, счетчики адреса считывания, буферные регистры, счетчики корректировки, регистр признака наложения, схемы сравнения, регистры адреса и блок анализа, причем гщресные входы каждо го запоминающего устройства соединены с первыми выходами соответствую щих счетчика адреса записи и счетчик адреса считывания, второй выход-каждого счетчика адреса записи, крсяле первого через буферный регистр соеди нен с адресным входом запоминающего устройства, вход первого запоминающего устройства, первые входы оперативного запоминающего устройства и блока дешифрации команд подключены к второму входу системы, управляющие входы счетчиков адреса записи, адрес считывания, буферных регистров и заЬоминающих устройств соединены с первым выходом блока дешифрации команд, выходы запоминающих устройств кроме первого, подключены к входам первого и второго счетчиков корректировки и к входу регистра признака наложения, выход первого запоминающего устройства соединен с входом третьего счетчика корректировки, вхо ды запоминающих устройств кроме первого, соединены с первыми выходами третьего и четвертого счетчиков корректировки, первого и второго регистров адреса, входы первого регистра адреса соединены соответственно с первьми выходами.первого и второго счетчиков корректировки,,с вторым выходом третьего счетчика корректировки и с вторым входом оперативного запоминающе го устройства, второй выход первого регистра адреса, первый выход оперативного запоминающего устройства и второй выход блока дешифрации команд соединены с выходом система, вход второго регистра адреса со-г единен с третьим выходом первого регистра адреса,, четвертый выход которого и вторые выходы второго регистра адреса и четвертого счетчика корре ктировки подключены к третьему входу оперативного запоминающего устройства, четвертый вход которого соединен с вь1ходом регистра текущей информации, второй выход - подключен к входу регистра предыдущей информации, третий выход третьего счетчика корректировки подключен к первому входу четвертого счётчика корректировки, второй вход которого подключен к третьему выходу второго регистра адреса, первые входы пербой, второй и третьей схем сравнения подключены соответственно к первому к второму выходам регистра признака наложения и к третьему выходу четвертого счетчика корректировки, вторые входы первой н второй схем сравнения подключены соответственно к вторым выходам второго и первого счетчиков корректировки, выход регистра признака наложения соединен с вторым входом блока дешифрации команд, входы кото юго, начиная с третьего, подключены йоответственно к выходам схем сравнения с первой по шестую, входы четвертой схемы сравнения соединены с вторыми выходс1ми первых счетчиков адреса записи и адреса считывания, входы пятой схемы сравнения соединены с третьим выходом второго счетчика адреса.записи и с вторым выходом третьего счетчика адреса считывания, входы шестой схемы сравнения соединены с вторым выходом второго счетчика адреса считывания и с третьим выходом третьего счетчика адреса записи, управляющие входы счетчиков корректировки, регистров адреса, оперативного запоминающего устройст-. ва и регистра предыдущей информации .соединены с третьим выходом блока дешифрации команд, четвертый и пятый выходы которого подключены соответственно к первому и второму управляющим входам блока анализа, первый и второй входы которого соединены со ответственно с выходами регистра предьщущей информации и блока кванто вания по уровню, третий вход блока анализа и вход регистра текущей информации соединены с третьим входом системы, выходы первой и второй груп блока анализа соединены соответственно с группами входов регистра текущей информации и блока дешифрации команд. 2. Система по п. 1, отличающаяся тем, что блок анализа содержит триггеры, элементы И, сдвиговый регистр, дешифратор и схемы сравнения, первые входы которых соединены с третьим входом блока, вторые входы первой и второй схем сравнения подключены к первому входу бло ка, третьи входы первой, и второй схем сравнения и первый вход сдвигового регистра соединены с первым управляющим входом блока, второй вход сдвигового регистра подключен к второму входу блока, выход сдвигового регистра соединен с входом дешифратора, выходы которого являются перво группой выходов блока, единичный вхо первого триггера соединен с первым выходом дешифратора, нулевой вход с BToptJM выходом дешифратора,, единич ный вход второго триггера соединен с выходом первой схемы сравнения, выход второй схемы сравнения подключен к соответствующему выходу второй группы блока и к нулевому входу вто-рого триггера, входы первого элемента И соединены с единичными выходами первого и второго триггеров, выход подключен к единичному входу третьего триггера, входы второго элемента соединены с вторым выходом дешифратора и с единичным выходом третьего триггера, выход т подключен к еди-. ничному входу четвертого триггера, Нулевые входы третьего и четвертого Триггеров соединены с выходом третьего элемента И, первые входы пятого, шестого, седьмого и восьмого триггеров соединены соответственно с единичными выходами первого, второго, третьего и четвертого триггеров, вторые входы триггеров с пятого по восьмой соединены с вторым управляющим входом блока, входы третьего элемента И подключены соответственно к нулевым выходам первого и второго триггеров и к единичному выходу седьмого триггера, выходы элементов И с третьего по девятый соединены с соответствующими выходами второй группы блока, входы четвертого элемента И соединены с единичным выходом пятого триггера, с нулевБ 1 выходами первого и третьего триггеров, входы пятого элемента И соединены с нулевым выходом первого триггера и с единичными выходами пятого и восьмого триггеров, входы шестого элемента И соединены с единичным выходом шестого триггера и с нулевыми выходами второго и седьмого триггеров, входы седьмого элемента И соединены с нулевым выходом второго триггера. с единичными выходами шестого и восьмого триггеров, входы восьмого элемен та и соединены с единичным выходом четвертого триггера и с нулевым выходом восьмого триггера, входы девятого элемента И подключены к единичному выходу третьего триггера и к нулевому выходу седьмого триггера, выход третьей схемы сравнения соединен с соответствующим выходом второй группы блока. Источники информации, принятые во внимание при экспертизе . 1. Кузьмин С. 3. Основы теории цифровой обработки радиолокационной информации. М., Советское радио, 1974, с. 178-197. 2. Патент США № 3617719, кл. 235-152, кл. G 06 Г 7/38, опублик. 1971 прототип).

J«

w.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для упорядочения массива чисел | 1984 |

|

SU1234827A1 |

| Анализатор амплитудных распределений | 1984 |

|

SU1247894A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

Авторы

Даты

1981-02-15—Публикация

1978-12-27—Подача