(54) СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий стохастический интегратор | 1979 |

|

SU789998A1 |

| Стохастический интегратор | 1978 |

|

SU744607A1 |

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Весоизмерительное устройство | 1985 |

|

SU1255866A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Аналоговый интегратор | 1986 |

|

SU1339592A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

Изобретение относится к вычислительной технике и может быть использовано дпя построения стохастичес- ких вычислительных устройств. Известны стохастические интеграторы, содержащие реверсивный счетчик, вход которого является входом интегратора, а разрядные выходы подключены к разрядным входам блока стохастического кодирования, выход которого является выходом интегратора 1 и 2. Недостаток таких интеграторов отсутствие возможности изменения шага интегрирования в процессе их эксплуатации, что существенно сужает и функциональные возможности. Наиболее близок к предлагаемому стохастический интегратор, содержащий блок стохастического кодирования (схема сравнения, разрядные входы которой подключены к генератору случайных чисел), выход которого является выходом интегратора, реверсивный счетчик, состоящий из п синхронных Т-триггеров (Т-К-триггеров) и п блоков формирования переноса, причем выход блока формирования переноса 1го разряда подключен ко входу блока цепи переноса (i+l)-ro разряда и к Т-входу триггера (i,+ l)-ro разряда З Такое устройство обладаем узкими функциональными возможностями (невозможность изменения шага интегрирования устройства в процессе его эксплуатации без применения соответствующих электрических и механических переключений). Это объясняется тем, что входные приращения в таком устройстве должны быть фиксированными, с весом, равным весу единицы младшего разряда реверсивного счетчика. Поэтому изменение величины входных приращений (шага интегрирования) в известном устройстве влечет за собой необходимость.введения соответствующих переключателей в схеме реверсивного счетчика, что существенно усложняет последний и снижает надежность устройства в целом. Вместе с тем, широкий круг практических задач, например решение систем дифференциальных и логических уравнений с использованием стохастических интеграторов, требует в общем случае нгьпичия различных величин входных приращений интеграторов. Аналогичное требование возникает также в случае

решения одной и той же задачи с раз ной точностью и скоростью.

Цель изобретения - расширение функциональных возможностей за счет обеспечения изменения шага интегрирования.

Поставленная цель достигается тем что в стохастическом интеграторе, содержащем блок стохастического кодирования, выход которого является выходом интегратора, п-разрядный реверсивный счетчик, первые входы разрядов которого соединены с соответствующими входами блока с ;охастического кодирования, второй выход каждого разряда реверсивного счетчика, кроме старшего разряда, соединен с первым входом соседнего старшего разрядаJ реверсивный счетчик содержит дополнительный нулевой разряд, вход которого соединен с третьим выходом первого разряда, а первый выход - с первым входом первого разряда, третий выход каждого разряда реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, соединен со вторым входом соседнего младшего разряда, кроме дополнительного нулевого разряда, второй выход старшего разряда реверсивного счетчика соединен со вторым входом соседнего младшего разряда, третьи входы разрядов реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, и второй вход Старшего разряда подключены к синхронизирующему входу интегратора, каждый, начиная с четвертого по (К+3)-ый, вход каждого К-го разряда реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, и каждый, начиная с третьего псь (п+2)-ый, вход последнего старшего разряда соединен с четвертым выходом соответствующего соседнего младшего разряда и вторым выходом дополнительного нулевого разряда.

Кроме того, каждый разряд дополнительного нулевого и старшего разрдов содержит триггер, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, элемент НЕ и блок формирования переноса, первый вход которого соединен с Т-входом триггера и является первым входом разряда реверсивного счетчика, прямой выход триггера соединен с первыми в: одэми первого элемента ИЛИ, певого и третьего элементов И, выход третьего элемента И явJ;Iяeтcя первым выходом разряда реверсивного счетчика, инверсный выход триггера соед иен с первым входом второго элемента ИЛИ и является четвертым выходом разряда реверсивного счетчика, каждый/ начиная со второго по (1+1)-ый вход первого элемента И является соответствующим входом разряда реверс ного счетчика, начиная с четвертого

по (К+3)-ый, выход первого элемента соединен с первым входом третьего элемента ИЛИ, второй вход которого является вторым входом разряда реверсивного счетчика, выход третьего элемента ИЛИ соединен со входом элемента НЕ, со вторыми входами первого и второго, элементов ИЛИ и является третьим выходом разряда реверсивного счетчика, выход элемента НЕ соединен со вторым входом третьего элемента И и первым входом второго элемента И, второй вход которого является третьим входом разряда реверсивного счетчика, а выход соединен с С-входом триггера, выходы первого и второго элементов ИЛИ соединены соответственно со вторым и третьим входами блока формирования переноса, выход которого является вторь1м выходом разряда реверсивного счетчика.

Старший разряд реверсивного счетчика содержит триггер первый, второй и третий элементы И и элемент НЕ причем Т-вход триггера является первым входом старшего разряда реверсивного счетчика, прямой выход триггера соединен с первыми входами первого и третьего элементов И, выход третьего элемента И является первым выходом старшего разряда реверсивного счетчика, каждый начиная со второго по (п+1)-ый, вход первого элемента И является соответствующим входом старшего разряда реверсивного счетчика, начиная с третьего по (п+2)-ый выход первого элемента И соединен со входом элемента НЕ и является вторым выходом старшего разряда реверсивного счетчика, выход элемента НЕ соединен со вторым входом третьего элемента И и первым входом второго элемента И, второй вход itoToporo является вторым входом старшего разряда реверсивного счетчика, а выхсад соединен с С-входом триггера.

Дополнительньой нулевой разряд реверсивного счетчика содержит триггер и источник постоянного сигнала логической единицы, выход которого является первым выходом дополнительного нулевого разряда реверсивного счетчика. Т-вход триггера является входом дополнительного нулевого разряда реверсивного счетчика, а инверсный выход - вторым выходом дополнительного нулевого разряда реверсивного счетчика.

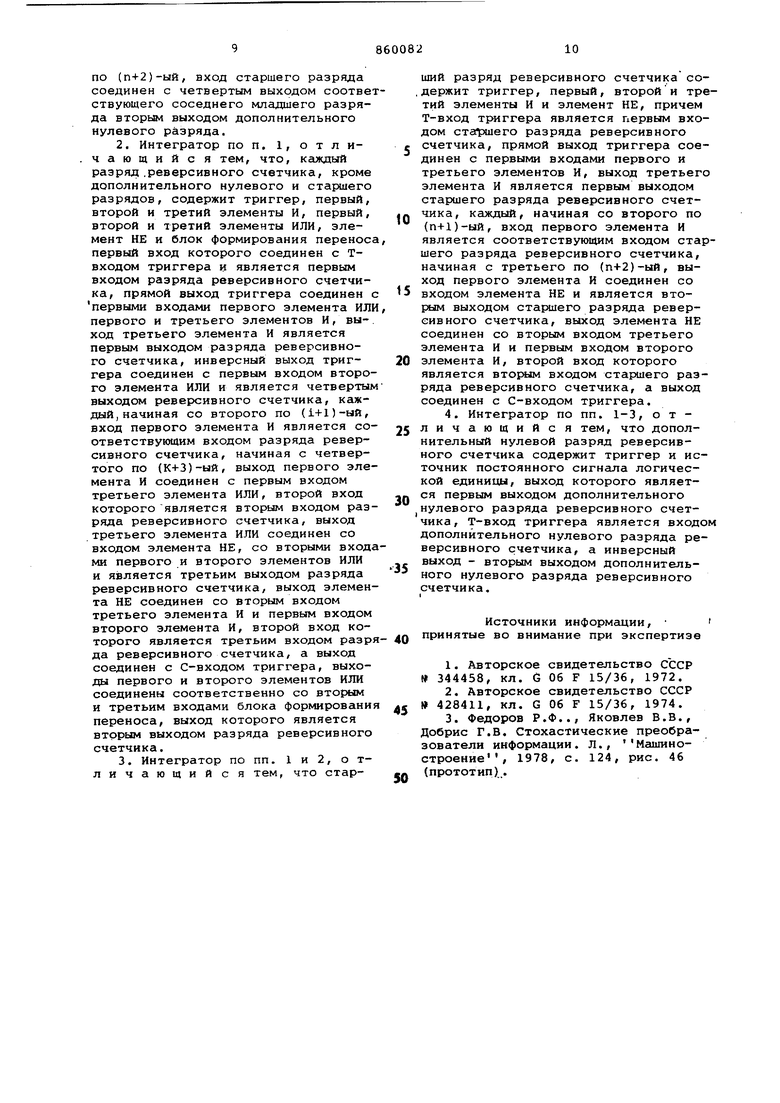

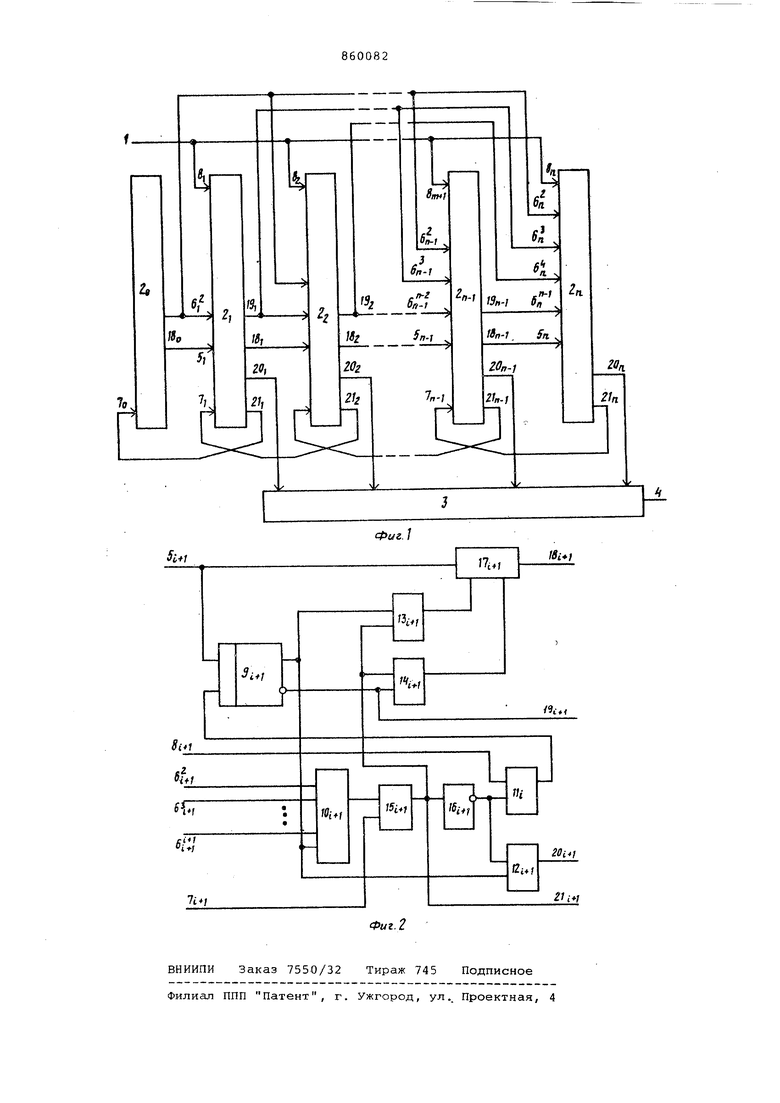

На фиг. 1 приведена блок-схема стохастического интегратора; на фиг. 2 - схема (1+1)-го разряда реверсивного счетчика(1 0,1,2,.. . (пСтохастический интегратор имеет синхронизирующий вход 1, дополнительный нулевой разряд 2 и л разрядов 2., 2,..2у,1 2 у, реверсивного счетчика, блок 3 стохастического кодирования, выход которого является выходом 4 стохастического интегратор

Любой (1+1)-ый разряд реверсивноо счетчика, за исключением дополниельного нулевого и старшего разряов имеет фиг. 2) вход для сигалов переноса 5 , , входы 6, , 6 Д ... , связывающие его с сосед- с ими младшими i разрядами, вход Tf. ля сигнала блокировки счета, синхроизирующий вход 8 ,ч ; триггер 9j , ервый 10 , второй и третий элементы И,-первый 13.1 ; второй Л . и третий элементы ИЛИ, лемент НЕ , блок формироания переноса, выход для сигналов переноса, инверсный выход . триггера, прямой выход (i-H)-ro разряда, выход сигнала бло- М кировки счета.

Вход интегратора 1 подключен ко входам 8 всех разрядов реверсивного счетчика, кроме дополнительного нулевого. Вход . для сигнала пере- 20 носа в (1+1)-ый разряд подключен к выходу для сигнала переноса из соседнего младшего i-ro разряда, а также к Т-входу триггера . (i) входов , бД J... элемента 25 И . подключены к инверсным выхоам всех триггеров соседних младишх разрядов счетчика. Вход подключен к выходу (i+2)-го разряда и ко второму входу элемента ИЛИ Первые входы элементов ИЛИ и 14 подключены соответственно к прямому и инверсному выходам триггера 9 . Вторые входы этих элементов соединены между собой и подключены к выходу элемента ИЛИ , и к выходу . (i-H)-ro разряда счетчика, а выходы подключены соответственно ко второму и третьему входам блока формирования переноса . . Прямой выход триггера 9. подключен 40 также к (1+2)-му входу элемента . И ко входу элемента И 12 ,выход 20 которого соединен со входом (i+l)-ro разряда блока 3 стохастического кодирования. Инверсный j выход триггера 9 через выход подключен на входы элементов И 10 всех старших разрядов счетчика. Выход элемента И соединен со вторым входом элемента ИЛИ 15 ц. , ал выход которого подключен ко входу 7, i-ro разряда, а через элемент НЕ . - ко входам элементов И . и Выход последнего подключен к С-входу триггера 9 . Выход блока 3 стохастического ходи- рования подключен к выходу 4 устройства.

Следует отметить отличие дополнительного нулевого и старшего п-го разрядов от остальных разрядов.Триг- М гер 9 нулевого разряда предназначен для хранения масштабной единицы (маркера) при работе интегратора с минимальным шагом. Этот триггер не работает в счетном режиме, его С- 45

вход не подключен ко входу 1 устройства, а прямой выход не подключен к блоку 3. Кроме того, дополнительный нулевой разряд не имеет блока 1 формирования переноса. Поэтому он не содержит элементов И 10,, 11, 12, ИЛИ 13о, 1, 15о и элемента НЕ 16о. Вход 5 блока формирования переноса первого разряда подклчен к источнику постоянного сигнала логической единицы.

Старший п-ый разряд не имеет блока 17и формирования переноса элемен тов ИЛИ 13и и 14и и входа 7, в силу этого отпадает также необходимость в элементе ИЛИ 15ц.

Упоминае№лй в формуле изобретения индекс порядкового номера разряда реверсивного счетчика К имеет следующие пределы изменения: 2,3...п.

Устройство работает следующим образом.

Перед началом процесса интегрировния в реверсивный счетчик заносится начальное значение подынтегральной функции Уд, например, путем подачи параллельного кода у, на установочные S-входы триггеров. Младший разряд записываемого кода должен содержать масштабную единицу (маркер), которая в преобразовании двоичного кода функции у в стохастическую последовательность не участвует. Так если интегратор содержит 10 числовых разрядов (п-10) и должен работать с шагом л , то код начального значения функции у имеет вид

. 10000Если необходимо, чтобы интегратор

работал с минимально возможным шагом (используется вся разрядность) , то код УО дЬлжен быть следующим :

О, у y-sУЬ У У УО УЧО Если начальное значение подынтегральной функции у равно нулю, то при занесении его°в счетчик необходимо масзатабную единицу записывать только в разряд,определяемый величиной ш&га интегрирования. Например, при , код начального условия будет

0,00000100000.

Занесение начального значения подынтегральной функции с масштабной единицей автоматически настраивает интегратор на работу с соответствующей величиной шага интегрирования. Это достигается тем, что приращения ±лу, поступающие со входа 1 устройства на входы 8 всех разрядов, кроме нулевого, проходят лишь на С-входы триггерюв более старших разрядов по отношению к разряду, хранящему масштабную единиLQT. в разряд, хранящий масштабную единицу, а также в младшие по отношению к нему разряды приращения на С-входы триггеров не поступают. Например, интегратор, имеющий 10 числовых разрядов и один дополнитель ный, должен быть настроен на работу с шагом . в счетчик заносится код начального значения подынтегральной функции ,,,У4У5Уь 10000. Е циничные сигнсцты с инверсных выходов триггеров младших четырех разрядов и с прямого выхода триггера пятого разряда, хранящего масштабную единицу, вызывают срабатывание элеме тов И 10 5, ИЛИ 15, формирующих сигнал блокировки счета. С выхода эле1Мента ИЛИ 15 сигнал инвертируется элементом ИЛИ 16 и закрывает, элемен ты И 115-/ И 125-. В результате приращения +ду не проходят через элемент И llg на С-вход триггера 9. Си нал с выхода элемента ИЛИ 15 прохо дит также через цепочку элементов ИЛИ 15д,15з,155г и 15 ,элементы НЕ 1 16, 16 2, 16 и запрещает поступление приращений ±йу через элементы И 11, llj,, 11 на С-входы три геров 9 2.f 9 f которые в течение всего интервала интегрирования остаются в нулевом состоянии. Для того, чтобы триггеры в разрядах старше масштабного работали в счетном режиме (при сложении или выЧита нии), блоки формирования переноса 17, 17,, 17,, 174, 17 неработающих разрядов должны вырабатывать единичные сигналы. Это обеспечивается тем, что на всем интервале интегрирования в режиме сложения чере 134, 1 132., 13э, элементы ИЛИ 13, а в режиме вычитания через элементы ИЛИ 14х}, 142,, 14, 145 единичные сигналы с выходов элементов ИЛИ 15 ISj, 15}, 164, 15 поступают на сОот етствуквдие входы блоков формирования переноса 17 , 17,2., 17,,, 174, 175. Так как масштабная единица является только управляющей и не несе информации о величине и знаке Функции у, то она, во избежание искажения результата, не должна воприниматься блоком 3 стохастического кодирования. Это достигается тем, что сигнал с прямого выхода триггера Эд блокируется элементом И 125-, закрытым сигналом с элемента НЕ 16 и на вход блока 3 не поступает. ПосколйКу в разряде старше масштабного элементы И 12 и ИЛИ 15 при заданном шаге интегрирования никогда не срабатывают, то на выходах элемвнт 1в .НЕ 16 этих разрядов будут существовать единичныесигналы, раз р@11гиощие прохождение через элементы И 11 приращений j-йУ С-входы триггерюв 9, а через элементы И 12 - сигналов с прямых выходов этих триггеров на входы блока 3. Блок стохастического кодирования 3 обеспечивает преобразование текущего значения подынтегральной ункции у в стохастическую тактироанную последовательность f (j в , оответствии с известным алгоритмом (1,если N.J Я,,-; (о,если j R/, , где R. -п - разрядные равномерно d распределенные случайные числа; N - число статистических испытаний (шагов интегрирования) . Предлагаемое изобретение, позволяющее реализовать стохастический интегра.тор с возможностью автоматического изменения величины шага интегрирования путем простой корректировки кода начального условия, су-дественно расширяют функционаЪьные возможности этого устройства. Так, очень эффективно использование предлагаемого интегратора в различных системах моделирования, в которых в целях оптимизации модели требуется оперативно изменять ее параметры в процессе многократного просчета. Формула изобретения 1. Стохастический интегратор, содержащий блок стохастического кодирования, выход которого является выходом интегратора, п-разрядный реверсивный счетчик, первые выходы разрядов которого соединены с соответствующими входами блока стохастического, кодирования, второй вход каждого разряда реверсивного счетчика, кроме старшего разряда, соединен с первым входом соседнего старшего разряда, отличающийс я тем, что, с целью:расширения Функциональных возможностей за счет обеспечения изменения шага интегрирования, реверсивный счетчик содержит дополнительный нулевой разряд, вход которого- соединен с третьим выходом первого разряда, а первый выход - с первым входом первого разряда, третий выход каждого разряда реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, соединен со вторым входом соседнего младшего разряда, кроме дополнительного нулевого разряда, второй выход старшего разряда реверсивного счетчика соединен со вторым входом соседнего младшего разряда, третьи входы разрядов реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, и йторой вход старшего разряда подключены к синхронизирующему входу интегратора, каждый, начиная с четвертого по (К+3)-ый, вход каждого К-го разряда реверсивного счетчика, кроме дополнительного нулевого и старшего разрядов, и каждый, начиная с третьего

по (п+2)-ый, вход старшего разряда соединен с четвертым выходом соответствующего соседнего младшего разряда вторым выходом дополнительного нулевого разряда.

первыми входами первого элемента ИЛИ первого и третьего элементов И, вы-, ход третьего элемента И является первым выходом разряда реверсивного счетчика, инверсный выход триггера соединен с первым входом второго элемента ИЛИ и является четвертым выходом реверсивного счетчика, каждый, начиная со второго по (1+1)-ый, вход первого элемента И является соответствующим входом разряда реверсивного счетчика, начиная с четвертого по (К+3)-ый, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого является вторым входом разряда реверсивного счетчика, выход третьего элемента ИЛИ соединен со входом элемента НЕ, со вторыми входами первого и второго элементов ИЛИ и является третьим выходом разряда реверсивного счетчика, выход элемента НЕ соединен со вторым входом третьего элемента И и первым входом второго элемента И, второй вход которого является третьим входом разряда реверсивного счетчика, а выход соединен с С-входом триггера, выходы первого и второго элементов ИЛИ соединены соответственно со вторым и третьим входами блока формирования переноса, выход которого является вторым выходом разряда реверсивного счетчика.

0 (п+1)-ый, вход первого элемента И является соответствующим входом старшего разряда реверсивного счетчика, начиная с третьего по (п+2)-ый, выход первого элемента И соединен со

5 входом элемента НЕ и является втоftJM выходом старшего разряда реверсивного счетчика, выход элемента НЕ соединен со вторым входом третьего элемента И и первым входом второго

0 элемента И, второй вход которого является вторым входом старшего разряда реверсивного счетчика, а выход соединен с С-входом триггера.

0 I нулевого разряда реверсивного счетчика, Т-вход триггера является входом дополнительного нулевого разряда реверсивного счетчика, а инверсный выход - вторым выходом дополнительного нулевого разряда реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе

0

Авторы

Даты

1981-08-30—Публикация

1979-10-03—Подача