(54) УСТРОЙСТВО ДЛЯ АЛГЕБРАИЧЕСКОГО СЛОЖЕНИЯ КОДОВ ЦЕЛЫХ КОМПЛЕКСНЫХ ЧИСЕЛ 1 Изобретение относится к вычислиТельной технике и может быть испольёовано в вычислительних машинах и комплексах при обработке информации предстг1влениой комплексными чйслглда а также при решении уравнений и систем с комплексными, корнями. Известно устройство для алгебраического сложения кодов целых комплек ных чисел (ЦКЧ) ; которое содержит . елок сложения в системе счисления с основанием и блок вычитания в этой же.системе счисления LljИзвестно также устройство для алгебраического сложения кодов ЦКЧг которое содержит два регистра операндов, сумматор кодов целых комплек ных чисел в системе счисления с основанием , специальный блок инвертирования для получения инверс нрго значения кода вычитаемого при выполнении операции вычитания. В основу работы специального блок инвертирования положен принцип умножения на -1 (код -1 в системе счисления с основанием имеет вид 11101) Г23. Наиболее близким по технической сущности к изобретению является устройство для алгебраического сложения кодов ЦКЧ CBJ , которое содержит регистры первого и второго операндов, элементы ИЛИ, элементы задержки, специальный блок инвертирования, блоки элементов И, блок элементов ИЛИ, сумматор в системе счисления с основанием , блок управления, где прямые выходы разрядов регистра первого операнда подключены к першдм входам элементов И первого блока элементов и параллельно, прямые выходы разрядов регистра второго операнда подключены к первым входам элементов И второго блока элементов И параллельно, выходы регистра второго операнда подключены паргшлельно к входг1М блока инвертирования, первый выход блока управления подклк)чен к первому входу элемента ИЛИ и через первый элемент задержки к входам элементов И второго блока элементов И, второй выход блока управления подключен к второму входу элемента-ИЛИ и через второй элемент задержки - ко вторым входам элементов И третьего блока элементов И, выход элекюнта ИЛИ подключен, к вторым входам элементов И первого блока элементов, выходы элементов И первого, второго к третьего блоко

элементов И подключены соответственн к входам элементов ИЛИ блока элементов ИЛИ параллельно, выходы элементов ИЛИ блока элементов ИЛИ подключены к входам сумматора в системе счисления Соснованием параллельно.

Недостатками этого устройства являются низкое быстродействие, так как при вычитании основное время затрачивается на выполнение операции инвертирования, и большие затраты оборудования для построения блока инвертирования.

Целью изобретения является повышение быстродействия устройства и снижение аппаратурных затрат для .его построения.

Поставленная цель достигается тем, что устройство, для алгебраического сложения кодов целых комплексных чисел, содержащее два регистра операндов, элемент ИЛИ, первый и. второй элементы задержки, первый, второй и третий блоки элементов И, блок элементов ИЛИ, сумматор в системе счисления с основанием , причем первые входы элементов И первого блока элементов И соединены с выходом элемента ИЛИ, а вторые входы - с выходами разрядов регистра первого операнда, первый вход элемеьРга ИЛИ соединен с управляющим входом сложения устройства и с входом первого элемента задержки, выход которого соединен с первыми входами элементов И второго блока элементов И, вторые входы которых подключены к прямым выходам разрядов регистра второго о перанда, выход второго элемента задержки подключен к первым входам элементов И третьего блока элементов И, выходы элементов И первого, второго и третьего блоков элементов И соединены соответственно с первыми, вторыми и третьими входа. ми элементов ИЛИ, блока элементов ИЛИ, выходы которого подключены ко входам сумматора в системе счисления с основанием , содержит третий элемент задержки, вход которого соединен с управляющим входом вычитания устройства, а выход соединен с вторы входом элемента ИЛИ и с входом второго элемента задержки. Управляющий вход вычитания устройства соединен с четвертыми i входами элемента ИЛИ блока элементов ИЛИ с номерами пЗк и п«3к+1(к 0,1,2...). Инверсные выходы разрядов регистра второ го операнда подключены к вторым входам элементов И третьего блока элементов И.

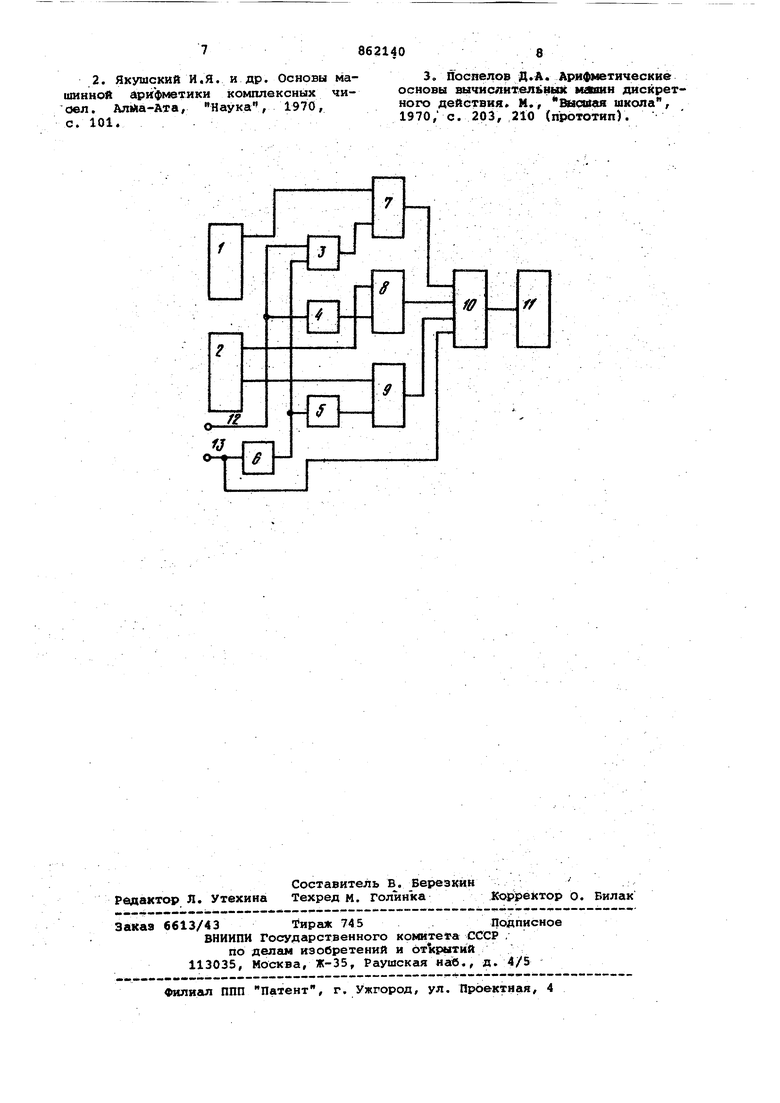

На чертеже представлена структурная схема устройствадля алгебраического сложения кодов целых комплексных чисел.

Устройство содержит регистры 1 и 2 первого и второго операндов, элегмент ИЛИ 3. .элементы задержки 4-6, блоки 7-9 элементов И, блок 10 элементрв ИЛИ, сумматор 11 в системе счисления с основанием .

Регистры 1 и 2 предназначены для приема и хранения кодов операндов перед выполнением операций сложения или вычитания.

Блоки 7-9 элементов,И,и блок 10 элементов ИЛИ предназначены для пердачи операндЬв на сумматор 11.

Сумматор 11 в системе счисления с основанием предназначен для суммирования кодов.

Элементы 4-7 задержки предназначены для организации вычислительного процесса.

Устройство работает следующим образом.

После приема операндов в регистры 1 и 2 подается сигнал на вход 12 если необходимо выполнить операцию сложения) или на вход 13 (если необходимо вычест1Р.4 из первого операнда второй). Операция сложения в устройстве выполняется так же, как и в прототипе.

При выполнении операции вычитания сигнал подается на вход 13. По ЭТОМУ сигналу на сумматор 11 в системе счисления с основанием через элементы ИЛИ блока 10 подаетс код 011...011011 (что выполнено схено, и код записывается непосредствено сигналом с входа 13).

По сигналу на входе 13, задержанному на элементе 6 задержки на врем поДачи в сумматор 11 кода 011... 011011,код первого операнда, считанный с прямых выходов разрядов регис ра 1, через элементы блока 7 и элементы ИЛИ блока 10 подается на сумматор, где складывается с поданным туда кодом 011...011011.

Но Сигналу с входа 13, задержанному на элементе 5 задержки на врем сложения в сумматоре 11, код, считанньЯ с инверсных выходов разрядов регистра 2, через элементы И блока 9 и элементы ИЛИ блока 10 подается на сумматор 11.

В результате сложения получается разность первого и второго операндов. ,

Пример 1. Пусть необходимо проннаэртировать код

А 1010. А 1010 1+J3, Разбиваем данный код на триады, причем старшую триаду необходимо допояни ь двумя нулями

А 001 010

i UpOHHeeptHpyeM разряды кода с учетом допрлйенных разрядов: . S 110101.

сложим код X с кодом 011011 tnv А 110010 -1 -j3, Сложение проводилось по правил для cHcteKU счисления с основание р-l+j. При применении данного апго{)итм необходимо, чтобы разрядность кЬд была кратной трем. Если .это не та то старшую триаду необходима допо нить нулями. Пример 2, А 1010 1 + уменьшаемое; В 100 --J2, - вычитаемое. Инвертируем разряоды вычитаемог . В он:, Inv В ОН + 011 1Д10100, Разность .. 1010 1110100 1111110 1 + j5. Пример 3. А 000...000 001 010 1 + J3, S 111...Ill llOllfil 111...Ill 110 101 он.. .011 oil oil ...000 110 010 -l-j3. T. e. дополнять можно проиэвол .ным количеством нулей, но разрядность кода А при этом должна оста ваться кратной трем. Длина.кода 011. ..011011 должна при этом быть равной длине операн дов. Проведем сравнительную оценку быстродействия прототипа данного устройства. Примем при этом, что появление операций сложения и вычит ния равновероятно. Учитывать будем тЬлько время суммирования, как самое длинное. t (tcM -t-tMHU ) (t:cм+7 t&in ) 9 . - tc. где ц - среднее время работы прототипа; tg, - время операщии сложения ВЫч Р® операции вычита ни (прототип); %ЫМ1 кНб tp - время суммирования на сумматоре в систем счи ления с основанием р -i+j; 7tp, - время инвертирования на блоке инвертирования tел +1 ьым 1 ,4 tgM +2tcM 3 а - J- . Чмч Р операции вычитани (предложенное устройств Выигрыш в быстродействий В предложенном устройстве коли чество оборудования уменьшено, так как для реализащии блока инвертирования прототипа необходикы элементы И-НЛИ-НЕ по колнчествуразрядов вычитаемого, а блок инвертирования в данном устройстве заменяется одним.элементом задержки. Формула изобретения Устройство для алгебраического сложения ксщоэ комплексных чисел, содержащее два регистра операндов, элемент ИЛИ, первый и второй элементы задержки, первый, второй и третий блоки элементов И, блок элементоь ИЛИ, сумматор в системе счисления с оснёванием , причем первые входы элементов И первого блока элементов И соединены с выходом элемента ИЛИ, а вторые входы - с выходами разрядов регистра первого операнда, первый вход элемента ИЛИ соединен с управляющим входом сложения устройства и с входом первого элемента задержки, выход которого соединен с перйыми входами элементов И второго блока элементов И, вторые входы которых подключены к прямым выходам разрядов регистра второго операнда, выход второго элемента задержки подключен к первым входам элементов И.третьего блока элементов И, выходы элементов И первого, второго и третьего блоков элементов И соединены соответственно с первыми, вторыми и третьими входами элементов ИЛИ, блока элементов ИЛИ, выходы которого подключены к входам сумматора в системе счисления с основанием l-fj, отличающееся тем, что, с целью увеличения быстродействия и снижения аппаратурных затрат, оно содержит третий элемент задержки, вход которого соединен с уп равляюедям входом вычитания устройст- . ва, а выход соединен с вторым входом элемента ИЛИ и с входом второго элеента задержки, управляюмий вход вы €итания устройства соединен с четвертыми входа В( элементов 1ИИ блока элемейтоа ИЛИ и номерами п Зк и п « Зк + 1 (к 0,1,2...), инверсные выходы разрядов регистра второго опера1зда подключены к вторым входам элементов И третьего блока элементов И. Источаи1си информации, щ}И11ЯШе во внимание при экспертизе 1, Акушский И.Я. и др. Основы мгаоинной арифметики комплексных чисел. Айма-Ата, Наука, 1970, г. 9в-101.

2. Яхушсхий И.Я. и др. Основы машинной apйф 4eтикн комплексных чисзел. АлМа-Ата, Наука , 1970, с. 101. .

3. Поспелов Д.Л. Арифметические основы вычислителбйшс машин дискретного действия. М., Высшая школа, 1970/ с. 203, 210 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для параллельного алгебраического сложения в знакоразрядной системе счисления | 1981 |

|

SU1003074A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

Авторы

Даты

1981-09-07—Публикация

1980-01-07—Подача