(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ВЫСТРОПРОТЕКАЮЩЕГО СЛУЧАЙНОГО ПРОЦЕССА

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1983 |

|

SU1120323A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство коррекции телевизионного сигнала | 1988 |

|

SU1628224A1 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Логарифмический аналого-цифровой преобразователь | 1989 |

|

SU1656563A2 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

I

Изобретение относится к аналоговой вычислительной технике и может быть использовано для точного воспроизведения быстропротукающих случайных процессов.

Известно устройство для кусрчяолинейной аппроксимации функций, со держа1(ее регистры, преобразователи код-напряжение,, интегратор, аналоговое вычитанядее устройство 1.

Однако это устройство имеет недостаточную точность воспроизведения быстропротекающих случай1ых процессовтак как необходимо время сброса интегратора или переключения одного интегратор1а на другой.

Наиболее близким по технической сущности к изобретению является устройство, содержащее оперативное запоминающее устройство, устройство ввода данных, два регистра, цифровой га,1читатель, преобразователь, коднапряжение, интегратор, блок синхронизации L2

Однако это устройство имеет недостаточную точность воспроизведения сигналов большей длительности , так как ошибка интегратора по напряжению смещения и току смещения операционного усилителя приводит к уходу нулевой линии моделируемого сигнала .

Цель изобретения - повышение точности моделирования случайного сигнала.

Поставленная цель достигается тем, что в устройство для моделирования быстропротекающего случайного процесса, содержащее оперативный зало

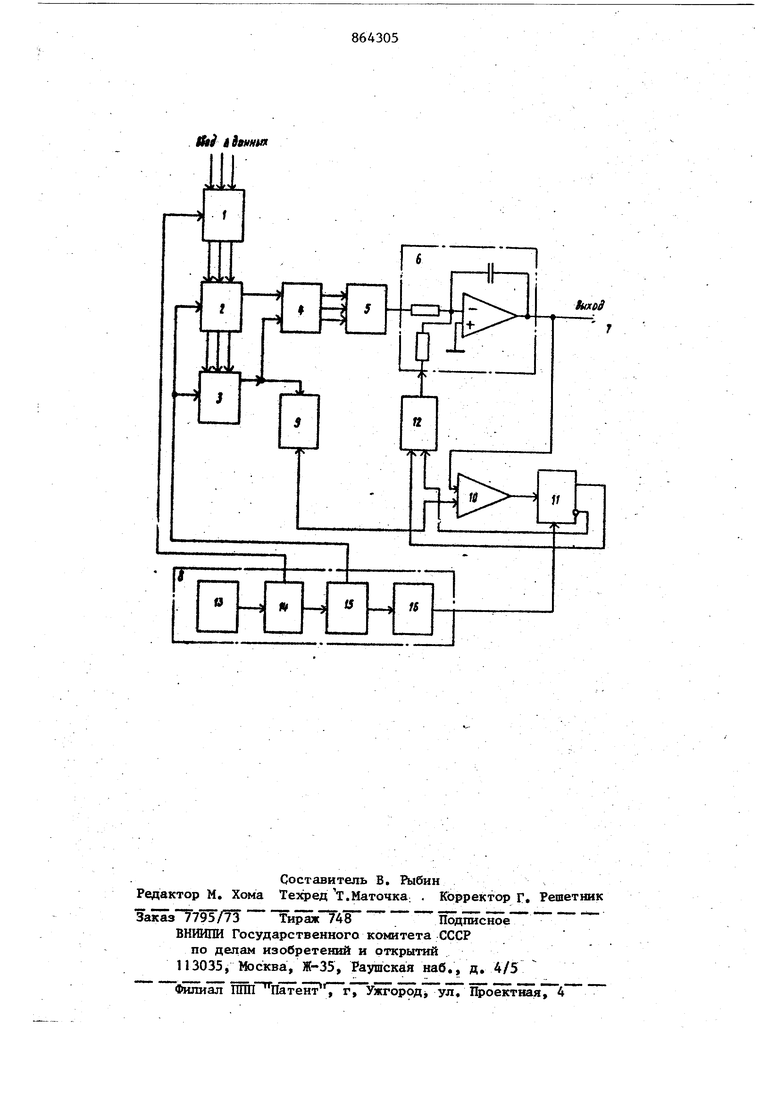

IS минающий блок, группа входов которого являет:;я группой входов устройства, информационные выходы оперативнсрго запоминагацего блока соединены с и формационными входами первого регист20ра, выход которого подключен к первому входу вычитателя, выход которого соединен со входом первого преобразователя кода в напряжение, вьтход которого подключен к первому суммирукицему интегратора, выход которого является выходом устройства, к управляющему входу оперативного за поминающего блока подключен первый выход блока синхронизации, второй выход которого соединен с управляющими входами первого и второго регистров, информационные выходы первого регистра подключены к информационным входам второго регистра, выход которого соединен со вторым входом вычитателя, введены второй преобразователь кода в напряжение, источник двуполярного опорного напряжения, компаратор и триггер, причем выход второго регистра подключен ко входу второго преобразователя кода в напряжение, выход которого подключен к первому.входу компаратора, выход которого соединен с первым входом триггера, прямой выход которого подключен к первому входу двуполярного источника опорного напряжения, выход которого соединен со вторым суммирующим входом интегратора, выход которого подключен ко второму входу компаратора, третий выход блока синхронизации соединен со вторым входом триггера, инверсньй выход которо.-о подключен ко второму входу двуполярного источника напряжения. На чертеже изображена схема пред лагаемого устройства, Устройство содержит оперативный запомина1(лций .блок 1, регистры 2,3, вьгчитатель 4, первьй преобразовател кода в напряжение 5, интегратор 6, клемму 7 вьщоду устройства блока 8 синхронизации, второй преобразовате 9 кода в напряжение, компаратор 10, триггер 1.1, источник 12 двуполярного опорного напряжения. Блок 8 синх ронизации содержит генератор тактов частоты 13 и последовательно соединенные три одновибратора 14-16, Выход генератора тактовой частоты 13 подключен ко входу одновибратора 14 первый выход которого является первым выходом блока 8, Второй выход однрвибрйтора 14 подключен ко входу одновибратора 15, первый выход кото го является вторым выходом блока 8, Второй выход, одновибратора 15 подкл чен ко входу одновибратора 16, выхо которого является третьим выходом б ка 8. Устройство работает следующим об разом. Входные данные об ординатах моделируемого сигнала поступают в оперативный запоминающий блок 1 и хранятся там, До начала формирования сигнала регистры 2,3 находятся в нулевом состоянии, В связи с тем, что интегратор 6 имеет ошибку интегрирования, . вызванную напряжением смещения или током смещения, напряжение на выходе интегратора 6 не равно нулю, поэтому компаратор 10 в соответствии с разницей напряжений на выходе второго преобразователя 9 кода в напряжение и интегратора б устанавливает триггер 1 1 по команде от блока синхронизации 8 в соответствующее положение так, что его выход устанавливает соответствующую полярность управляемого источника 12 двуполярного опорного напряжения таким образом, чтобы уменьшить величину ошибки интегратора 6, По началу фopмIipoвaния сигнала код первой ординаты поступает в первьш регистр 2, В это время во второй регистр 3 переписывается нуль. Так как на выходе второго регистра 3 записан нуль, то на выходе второго преобразователя 9 кода в напряжение также нулевое напряжение. Поэтому заряд емкости интегратора 6 на первом шаге моделирования осуществляется с целью этой компенсации. Далее в соответствии с разностью кодов двух регистров 2,3 вычитатель 4 устанавливает на выходе первого преобразователя 5 кода в напряжение, которое приводит к линейному заряду емкости интегратора 6, Через время, определяемое интервалами между ординатами из оперативного запоминающего блока 1, поступает значение кода второй ординат) в (буферный) регистр 2, а значение кода первой ординаты перепишем по команде от блока 8 синхронизации во второй регистр 3, На втором шаге моделирования в соответствии с разностью кодов второй и первой ординат, записанных соответственно в регистры 2,3 вычитатель 4 устанавливает на выходе преобразователи кода в напряжение 5 напряжение, которое приводит к дальнейшему заряду емкости интегратора 6, Так же началу второго шага моделирования происходит сравнение выходного напряжения первой ординаты, с пгмаемого с выхода преобразователя 9 кода в напряжение, с выходным напряжением интегратора 6 на компараторе 10, который через.триггер 11 устанавливает по команде от блока 8 синхронизации соответствующую полярность управляемого источника 12 двуполярногр опорного напряжения, при этом на втором этапе измерения корректируется ошибка интегратора, полученная на первом этапе,

В предлагаемом устройстве устраняется ошибка ин тегрировакия, оно поддерживает нуль на выходе при остановке оперативного запоминакицего блока и записи нуля в регистры 2,3, что позволяет установить нуль на выходе устройства автоматически.

Формула изобретения

Устройство для моделирования бы-ч стропротекающего случайного процесса, содержащее оперативный запоминающий блок, группа входов которого является группой входов устройства, информационные выходы оперативного запоминающего блока соединены с информационными входами первого регистра, выход которого подключен к первому входу вычитателя, выход КОТОРОГО соегтинрн со входом первого преобразователя кода в напряжение, выход которого подключен к первому суммирующему входу интегратора, выход которого является выходом уст- . ройства, к управляющему входу оперативного запоминающего блока подключен первый вьпсод блока синхронизации, второй выход которого соединен с управляющими вxoдa o первоего и второго регистров, информацнон

ные выходы первого регистра подключены к информационным входам второго регистра, выход которого соедийен со вторым входом вычитателя, отличающееся тем, что,

с целью повьшения точности моделирования, в него введены второй преобразователь, кода в напряжение, и источник двуполярного опорного напряжения, компаратор и триггер, причем

выход второго .регистра подключен ко входу второго преобразователя кода в напряжение, выход которого подключен к первому входу компара тора, выход которого соединен с первым входом триггера, прямой выход которого подключен к первому входу двуполярного источника опорного нап ряжения, выход которого соединен со вторым суммирующим входом интегратора, выход которого подключен ко второму входу компаратора, третий выход блока синхронизации соединен со вторым входом триггера, инверсный обратный выход которого подключен ко второму входу двуполярного источника напряжения.

Источники информации, во внимание при экспертизе

1, Авторское свидетельство СССР № 570070, кл. G 06 G 7/48, 1975.

Авторы

Даты

1981-09-15—Публикация

1979-12-05—Подача