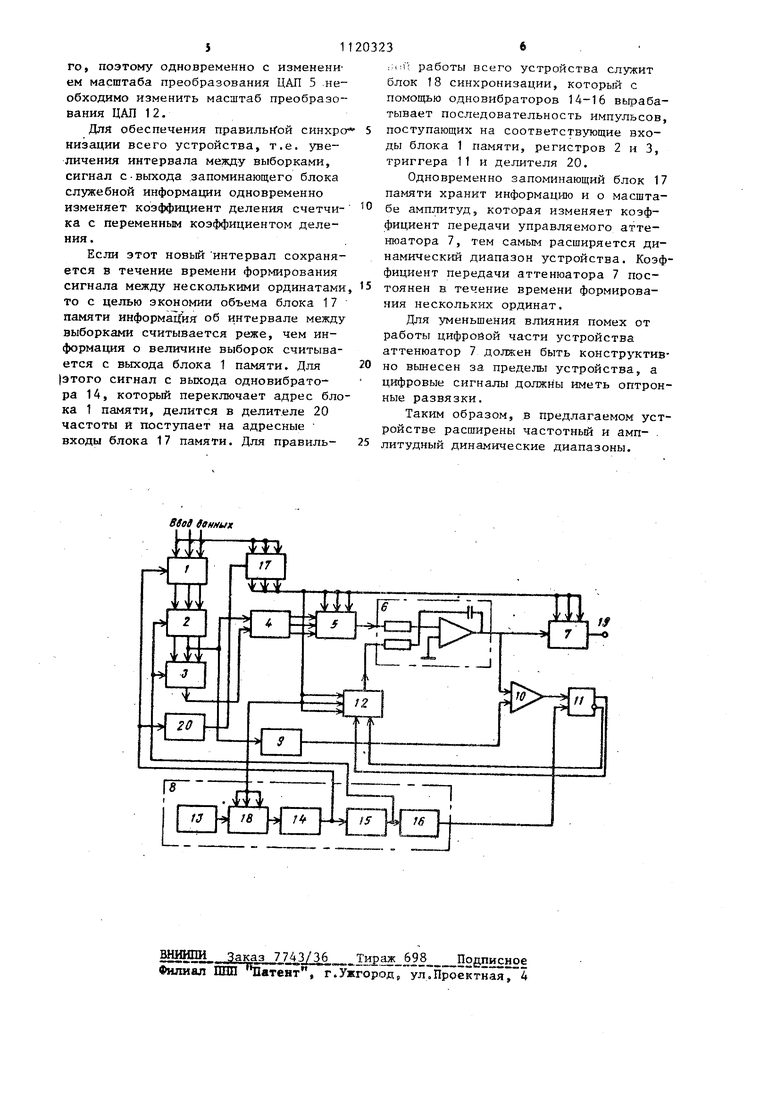

Изобретение относится к вычислительной технике и может найти применение при моделировании быстропроте кающих случайных процессов. Известен генератор случайного процесса, содержащий блоки памяти, интегратор, цифроаналоговый преобра зователь, блок управления и регистры памяти Cl 3. Недостатком этого генератора является узкий частотньй диапазон. Наиболее близким к изобретению является генератор случайного процесса, содержащий первьш блок памят информационньш вход которого являет ся информационным входом генератора выход первого блока памяти соединен с информационным входом первого регистра памяти, выход которого соеди нен с входом уменьшаемого вычитателя, входом первого цифроаналогового преобразователя и с информационным входом второго регистра памяти, выход которого соединен с входом вычитаемого вычитателя, выход первого цифроаналогового преобразователя соединен с управляющим входом компаратора, выход которого соединен с единичным входом триггера, единичньй и нулевой выходы которого соединены Соответственно с первым и вторым знаковыми входами второго цифроанартогового преобразователя, выход кото рого соединен с управляющим входом интегратора, выход которого соединен с информационным входом компаратора генератор тактовых импульсов, первый одновибратор, вькод которого соедине со считывающим входом первого блока памяти и входом второго одновибратор вькод которого соединен с синхронизи рзтощими входами первого и второго регистров памяти и входом третьего одновибратора , выход которого соединен с нулевым входом триге1 а 2|. Однако известный генератор имеет узкие амплитудньй и частотньй диапазоны. Целью изобретения является расши рение амплитудного и частотного диа rtaaoHOB моделируемого процесса. Поставленная цель достигается тем что генератор случайного процесса, содержащий первьй блок памяти, информационньй вход которого является информационным входом генератора, выход первого блока памяти соединен с информационньш входом первого регистра памяти, выход которого соединен с входом уменьшаемого вычитателя входом первого цифроаналогового преобразователя и с информационным входом второго регистра памяти, выход которого соединен с входом вычитаемого вьиитателя, выход первого цифроаналогового преобразователя соединен с первьм входом компаратора, выход которого соединен с единичным входом триггера, единичньй и нулевой выходы которого соединены соответственно с первым и вторьм знаковьс-1И входами второго цифроаналогового преобразователя, выход которого соединен с первым входом задания начальных условий интегратора, вькод которого соединен с вторым входом компаратора, генератор тактовых импульсов, первьй одновибратор, выход которого соединен со считывающим входом первого блока памяти и входом второго одновибратора, выход которого соединен с синхронизирующими входами первого и второго регистров памяти и входом третьего одновибратора, выход которо-го соединен с нулевым входом триггера, введены второй блок памяти, умножитель, аттенюатор, делитель частоты и счетчик, счетньй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и входом первого одновибратора, выход которого через делитель частоты соединен со считывающим входом второго блока памяти, информаи;ионньй вход которого подключен к информационному входу генератора, а выход второго блока памяти соединен с управляющим входом счетчика, с информационным входом второго цифроаналогового преобразователя, с управляющим входом аттенюатора и с первым входом умножителя, второй вход и выход которого соединены соответственно с выходом вычитателя и с вторым информационным входом интегратора, выход которого соединен с информационным входом аттенюатора, выход которого является выходом генератора. На чертеже приведена блок-схема предлагаемого генератора. Генератор содержит первьй блок 1 памяти, регистры 2 и 3 памяти, татель 4, умножитель 5, интегратор 6, аттенюатор 7,, блок 8 синхронизации, цифроаналоговьй пребразователь (ЦАП)9 компаратор 10, триггер 11 и ЦАП 12. Блок 8 синхронизации содержит генератор 13 тактовых импульсов и одновибраторы 14-16. Кроме того, генератор содержит второй блок 17 памяти а 6jfoK 8 синхронизации - управляемый счетчик 18, выход 19 и делитель 20 частоты. Генератор работает следующим образом. Данные об ординатах процесса заносятся в блоки 1 и 17 памяти. До начала формирования сигнала регистры 2 и 3 находятся в нулевом состоянии. Число на вькоде вьгчитателя 4 равно О, поэтому сигнал на выхо де умножителя также равен О (один из множителей - нуль). Сигнал на выходе ЦАП 9 О, а напряжение на выходе интегратора 6 может быть не рав ным нулю, поэтому компаратор 10 опрокидывается в соответствии со знако на выходе интегратора 6, а по тактовому импульсу от блока 8 синхронизации (выход одновибратора 16) триггер 11 также опрокидывается и устана ливает такую полярность напряжения на выходе ЦАП 12, чтобы скомпенсировать напряжение на выходе интегра;тора 6. Импульсы от одновибратора 16 поступают на триггер 11 непрерывно, поэтому если на выходе интегратора 6 происходит перекомпенсация, то сра-батывают компаратор 10 и триггер 11, а на выходе ЦАП 12 изменяется полярность компенсирующего напряжения. При воспроизведении сигнала с пос тоянными интервалами между ординатам Данные от блока 1 памяти последовательно поступают на регистры 2 и 3. Разница кодов между двумя соседними ординатами поступает на вторые входы умножителя 5, на первые входы которо го поступает какое-либо число от бло ка 17 памяти (величина этого числа не принципиальна для объяснения этого такта работы устройства). Разница кодов преобразуется ЦАП 5 в аналоговую величину и интегрируется интегра тором 6. Одновременно на вход ЦАП 9 последовательно поступают коды ординат формируемого сигнала. Этот ЦАП является эталонным и служит для компенсации ошибок интегратора. Непременным условием правильной работы является полная компенсация ошибки интегратора во время формирования сигнала между следующими ординатами. В противном случае возникает прогрессирующая ошибка. Перекомпенсация устраняется на следующем интервале и т.д. Таким образом, напряжение на выходе устройства представляет собой сигнал с линейной интерполяцией между ординатами, причем ошибки интегрирований скомпенсированы . Преимущества устройства для воспро изведения сигнала с переменными интервалами между выборками аналогичны адаптивному аналого-цифровому преобразователю, когда передаются или записываются только существенные ординаты в зависимости от частотного спектра сигнала. Интервалы между медленно изменяющимися сигналами больше, чем для быстро изменяющихся, при этом количество ординат, а следовательно, и объем ЗУ уменьшаются. Одновременно с записью существенных ординат сигнала записывают или передают величину интервала между ними. В принципе, переменный интервал меж ду ординатами не обязательно должен быть .для каждой выборки, а может быть для группы выборок. Работа устройства с переменными интервалами между выборками позволяет расширить частотный динамический диапазон вопроизведения сигнала, что эквивалентно увеличению длительности формируемого сигнала с сохранением , ВЫСОКОЧАСТОТНЫХ колебаний на нем при заданном объеме блока 1 памяти, Для реализации принципа переменного масштаба времени необходимо изменять частоту тактового генератора, а в случае линейной интерполяции изменять также и ток на входе интегратора, чтобы за большее время между выборками напряжение на интеграторе изменилось только на величину разности между значениями ординат. При работе устройства с переменными интервалами между выборками информация о длительности интервала, записанная в блок 17 памяти, поступает на первые входы умножителя 5 и изменяет величину напряжения на его выходе, при этом изменяется скорость заряда напряжения на выходе интегратора 6. Так как интервал между выборками увеличился, то за большее время компенсирующий сигнал с выхода ЦАП 12 изменит напряжение на выходе интегратора 6 больше допустимо1го, поэтому одновременно с изменением масштаба преобразования ЦАП 5 необходимо изменить масштаб преобразования ЦАП 12. Для обеспечения правиль11ой синхро низации всего устройства, т.е. увеличения интервала между выборками, сигнал свыхода запоминающего блока служебной информации одновременно изменяет коэффициент деления счетчика с переменным коэффициентом деления . Если этот новьй интервал сохраняется в течение времени формирования сигнала между несколькими ординатами то с целью экономии объема блока 17 памяти информа14ия об интервале между выборками считывается реже, чем информация о величине выборок считывается с выхода блока 1 памяти. Для |этого сигнал с выхода одновибратора 14, который переключает адрес бло ка 1 памяти, делится в делит.еле 20 частоты и поступает на адресные входы блока 17 памяти. Для правиль3 , работы всего устройства служит блок 18 синхронизации, который с помощью одновибраторов 14-16 вырабатывает последовательность импульсов, поступающих на соответствующие входы блока 1 памяти, регистров 2 и 3, триггера 11 и делителя 20. Одновременно запоминающий блок 17 памяти хранит информацию и о масщтабе амплитуд, которая изменяет коэффициент передачи управляемого аттенюатора 7, тем самым расширяется динамический диапазон устройства. Коэффициент передачи аттенюатора 7 постоянен в течение времени формирования нескольких ординат. Для уменьшения влияния помех от работы цифровой части устройства аттенюатор 7 должен быть конструктивно вьшесен за пределы устройства, а цифровые сигналы должны иметь оптронные развязки. Таким образом, в предлагаемом устройстве расширены частотньм и амплитудный динамические диапазоны.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство коррекции телевизионного сигнала | 1988 |

|

SU1628224A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Цифровой вольтметр | 1985 |

|

SU1337791A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| Цифровой регулятор температуры | 1986 |

|

SU1352470A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для дискретного преобразования Фурье | 1986 |

|

SU1361576A1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА, содержащий первый блок памяти, информационный.вход которого является информационным входом генератора, выход первого блока памяти соединен с информационным входом первого регистра памяти, выход которого соединен с входом уменьшаемого вычитателя, входом первого цифроаналогового преобразователя и с информационным входом второго регистра памяти, выход которого соединен с входом вычитаемого вычитателя, выход первого цифроаналогового преобразователя соединен с первым входом компаратора, выход которого соединен с единичным входом триггера, единичный и нулевой выходы которого соединены соответственно с первым и вторым знаковыми входами второго цифроаналоговога преобразователя, выход которого соединен с первым входом задания начальных условий интегратора, выход которого соединен с вторым входом компаратора, генератор тактовых импульсов, первый одно-, вибратор, выход которого соединен со считывающим входом первого блока памяти и входом второго одновибратора, выход которого соединен с синхронизирующими входами первого и второго регистров памяти и входом третьего одновибратора, выход которого соединен с нулевым входом триггера, о тличающийся тем, что, с целью расширения амплитудного и частот ного диапазонов формируемого процесса, он содержит второй блок памяти, умножитель, аттенюатор, делитель частоты и счетчик, счетньм вход и выход, которого соединены соответственно с выходом генератора тактовых импульсов и входом первого одновибратора, выход которого Через делитель частоты соединен со считывающим входом второго блока памяти, информационный вход которого подключен к информационному входу генератора, а выход jBToporo блока памяти соединен с управf ляющим входом счетчика, с информационным входом второго цифроаналогового преобразователя, с управляющим входом аттенюатора и с первым входом умножителя, второй вход и выход которого соединены соответственно с выходом вычитателя и вторым информационным входом интегратора, выход которого соединён с информационным входом аттенюатора, выход которого является выходом генератора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Наклонный судоподъемник | 1987 |

|

SU1404587A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для моделирования быстропротекающего случайного процесса | 1979 |

|

SU864305A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-04-20—Подача