(54) ПОСТОЯННОЕ ЗАПОМИНАКНЦЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| Ассоциативное запоминающее устройство | 1988 |

|

SU1520595A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Генератор случайного Марковского процесса | 1982 |

|

SU1070548A1 |

1

Изобретение относится к вычислительной технике, а именно к постоянным запоминающим устройствам (ПЗУ), работающим в специализированных и управляющих ЦВМ, в системах сбора и обработки информации, в цифровых системах контроля и управления.

Известны матричные ПЗУ, содержащие один запоминаю|дий элемент на каждый бит информации, в которых усовершенствования касаются либо повышения быстродействия ПЗУ, либо увеличения его помехоустойчивости, либо контроля ПЗУ D3 .

Недостатком их является ограничение информационной емкости числом запоминающих элементов (сердечников), отверстий в ферритовой пластине, диодов, используе а1х в накопителе.

Наиболее близким техническим решением к предлагаемому является матричное ПЗУ, например трансформаторного .типа с одним дешифратором адреса. ПЗУ содержит шину опроса, по которой сигнал опроса через формирователь поступает на все элементы памяти, с которых должен считываться единичный код. Выходы элементов памяти объединены по строкам. Таким образом, матрица состоит из п у. m элементов памяти и имеет п выходных шин, подключенных к выходному регистру числа. Адрес выбираемого числа записан в регистре адреса.

10

Сигнал опроса устанавливается в ноль выходной регистр, а затем через формирователь импульсов формирует импульс опроса элементов памяти. При этом в регистр числа по выходным нам поступает п-раэрядный код со столбца элементов памяти, возбужденных выбранной шиной дешифратора, управляемого регистром адреса. Описанное ПЗУ имеет емкость m х п бит t2.

20

Недостатком такого ПЗУ является необходимость увеличения числа запоминающих элементов для увеличения инормационной емкости ПЗУ за счет увеичения его выходной разрядности.

Цель изобретения - увеличение емкости ПЗУ без увеличения числа запоминающих элементов на один бит информации.

Поставленная цель достигается тем, что ПЗУ содержит матричный накопитель, подключенный к дешифратору адреса, соединенному с регистром адреса, шины опроса, регистр числа, группы вентилей, дополнительньй дешифратор адреса и счетчик тактовых импульсов, выходы которого соединены со входами дополнительного дешифратора адреса и первыми входами вентилей соответствующей группы, вторые входы которых соединены с соответствующими выходами матричного накопителя, а выходы - со входами регистра числа, выходы дополнительного дешифратора адреса соедичены с шинами опроса.

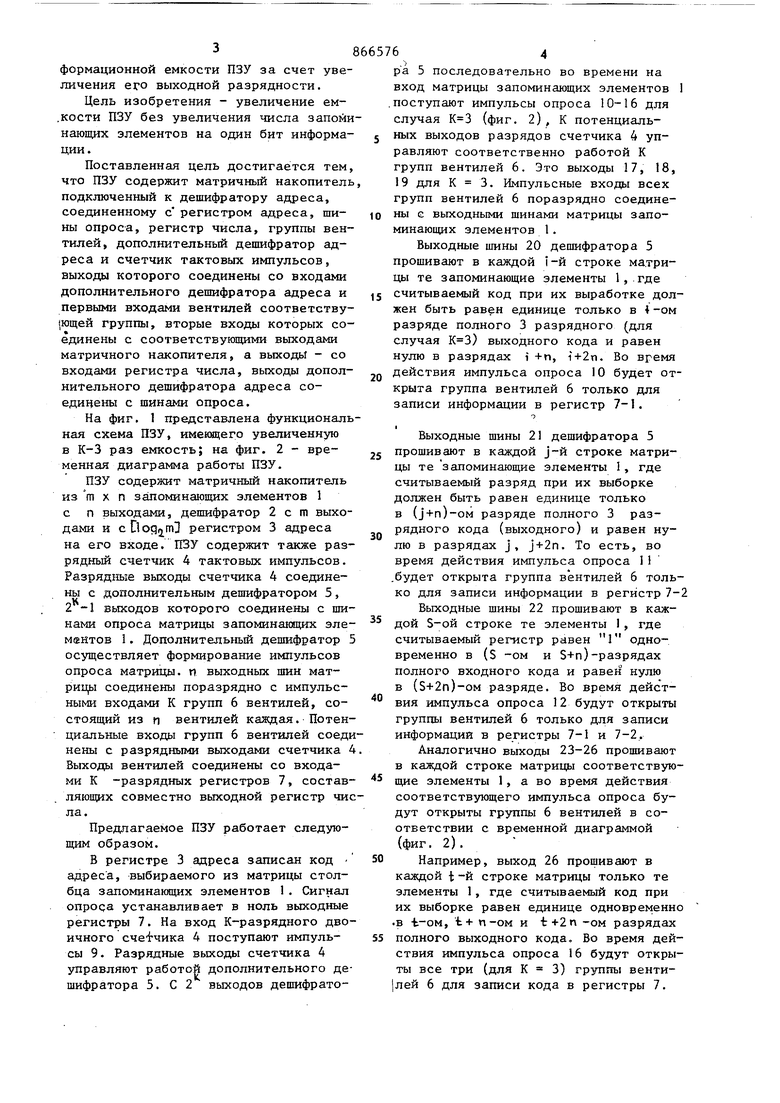

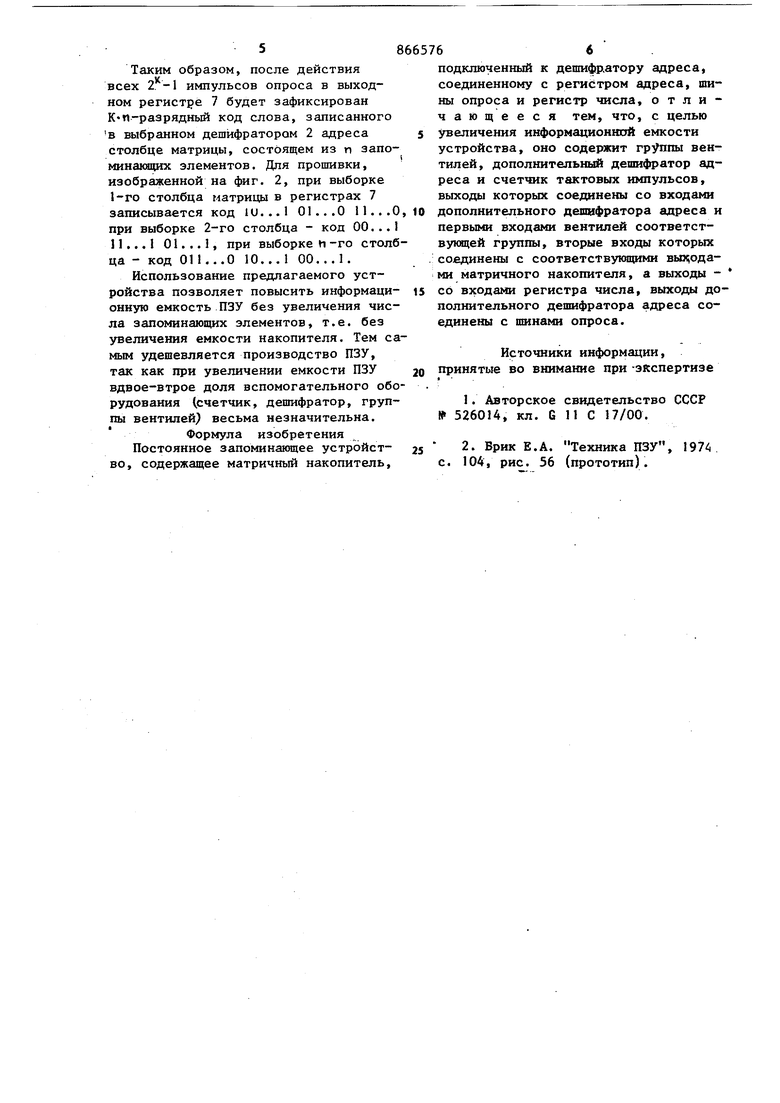

На фиг. 1 представлена функциональная схема ПЗУ, именщего увеличенную в К-3 раз емкость; на фиг. 2 - временная диаграмма работы ПЗУ.

ПЗУ содержит матричный накопитель из т X п заломинающих элементов 1 с п выходами, дешифратор 2cm выходами и cDoQi ml регистром 3 адреса на его входе. ПЗУ содержит также разрядный счетчик 4 тактовых импульсов. Разрядные выходы счетчика 4 соединены с дополнительным дешифратором 5, 2 -1 выходов которого соединены с шинами опроса матрицы запоминающих элементов 1. Дополнительный дешифратор 5 осуществляет формирование импульсов опроса матрицы, п выходных шин матpHu i соединены поразрядно с импульсными входами К групп 6 вентилей, состоящий из п вентилей каждая. Потенциапьные входы групп 6 вентилей соединены с разрядными выходами счетчика 4. Выходе вентилей соединены со входами К -разрядных регистров 7, составляющих совместно выходной регистр числа.

Предлагаемое ПЗУ работает следующим образом.

В регистре 3 адреса записан код адреса, выбираемого из матрицы столбца запоминающих элементов 1. Сигнал onpoqa устанавливает в ноль выходные регистры 7. На вход К-разрядного двоичного сче1гчика 4 поступают импульсы 9. Разрядные выходы счетчика 4 управляют работой дополнительного дешифратора 5. С 2 выходов дешифратора 5 последовательно во времени на вход матрицы запоминающих элементов 1 .поступают импульсы опроса 10-16 для случая (фиг, 2), К потенциальных выходов разрядов счетчика 4 управляют соответственно работой К групп вентилей 6. Это выходы 17, 18, 19 для К 3. Импульсные входы всех групп вентилей 6 поразрядно соединены с выходными шинами матрицы запоминающих элементов 1.

Выходные шины 20 дешифратора 5 прошивают в каждой I-и строке матрицы те запоминающие элементы 1, где 5 считываемый код при их выработке должен быть равен единице только в 4-ом разряде полного 3 разрядного (для случая ) выходного кода и равен нулю в разрядах i +г, i+2n. Во время Р действия импульса опроса IО будет открыта группа вентилей 6 только для записи информации в регистр 7-1.

о I

Выходные шины 21 дешифратора 5 5 прошивают в каждой j-й строке матрицы те запоминающие элементы 1, где считываемый разряд при их выборке должен быть равен единице только в (j+n)-OM разряде полного 3 разрядного кода (выходного) и равен нулю в разрядах J, j-f2n. То есть, во время действия импульса опроса 11 .будет открыта группа вентилей 6 только для записи информации в регистр 7-2

Выходные шины 22 прошивают в каждой S-ой строке те элементы 1, где считываемый регистр равен 1 одновременно в (S -ом и S+n)-разрядах полного входного кода и равен нулю в (S+2n)-OM разряде. Во время действия импульса опроса 12 будут открыты группы вентилей 6 только для записи информации в регистры 7-1 и 7-2.

Аналогично выходы 23-26 прошивают в каждой строке матрицы соответствующие элементы 1, а во время действия соответствующего импульса опроса будут открыты грзтпы 6 вентилей в соответствии с временной диаграммой (фиг. 2).

0 Например, выход 26 прошивают в каждой t-и строке матрицы только те элементы 1, где считываемый код при их выборке равен единице одновременно .в i-oM, t+ n-ом и Ь+2п -ом разрядах 5 полного выходного кода. Во время действия импульса опроса 16 будут открыты все три (для К 3) группы венти|лей 6 для записи кода в регистры 7. Таким образом, после действия всех 2 -1 импульсов опроса в выходном регистре 7 будет зафиксирован КП-разрядный код слова, записанного в выбранном дешифратором 2 адреса столбце матрицы, состоящем из п запо минахицих элементов. Для прошивки, изображенной на фиг. 2, при выборке 1-го столбца матрицы в регистрах 7 записывается код 1U...1 01...О П.. при выборке 2-го столбца - код 00... 11... 1 01... 1, при выборке и-го столб ца - код 011...О 10...1 00...1. Использование предлагаемого устройства позволяет повысить информационную емкость ПЗУ без увеличения числа запоминающих элементов, т.е. без увеличения емкости накопителя. Тем с мым удешевляется производство ПЗУ, так как при увеличении емкости ПЗУ вдвое-втрое доля вспомогательного обо рудования (счетчик, дешифратор, группы вентилей) весьма незначительна. Формула изобретения Постоянное запоминающее устройство, содержащее матричный накопитель. 66 подключенный к дешифратору адреса, соединенному с регистром адреса, шины опроса и регистр числа, отличающееся тем, что, с целью увеличения информационной емкости устройства, оно содержит группы вентилей, дополнительный дешифратор адреса и счетчик тактовых импульсов, выходы которых соединены со входами дополнительного дешифратора адреса и первыми входами вентилей соответствукяцей группы, вторые входы которых соединены с соответствующими выз ;одами матричного накопителя, а выходы - со входами регистра числа, выходы дополнительного дешифратора адреса соединены с шинами опроса. Источники информации, принятые во внимание при -экспертизе 1. Авторское свидетельство СССР 11 С 17/00. № 526014, кл. G 2. Брик Е.А. Техника ПЗУ, 197 104, рис. 56 (прототип).

Фиг.1

(Iflfljp

ni2}p -

(Zn.ti}p

KLAJv

Г

Я

и 0

ft

& IB

kJv

.

Рй&

Авторы

Даты

1981-09-23—Публикация

1978-05-04—Подача