(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ ЭЛЕКТРОННЫХ УСТРОЙСТВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для контроля параметров | 1986 |

|

SU1403074A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| Устройство для автоматического контроля блоков | 1984 |

|

SU1179348A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

1

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля электронных устройств и узлов различного назначения.

Известно устройство централизо- ванного контроля, содержащее датчики, сигнализаторы отклонений элементы И и ИЛИ, коммутаторы, узел внешнего запуска, цифровой измеритель, блок управления, цифровой регистратор, тёЛмер, дешифратор, счетчик. В устройстве реализуется регулярное ин- фармсоднонное обслуживание с управляемой длительностью опроса датчиков, которое необходимо для измерения параметров с заданной точностью, при этом управление осуществляется по сигналам, которые формируются на выходах сигнализаторов отклонений 1} .

Недостаток устройства - невысокое быстродействие, что ограничивает его .применение для контроля электронных устройств в динамике работы, кроме того, устройство не обеспечивает отработку отдельных узлов и устройства в целом.

Известно также устройство для контроля логических узлов, содержащее оперативное запоминающее устройство.

адресный коммутатор,, блок управления, блок генерации стимулирующих воздействий, блок коммутации стимулирующих воздействий, блок анализа неисправностей и логической обработки. Такое устройство обеспечивает отработку функциональных узлов электронных систем путем Формирования управ.Q ляювдего сигнала с последующим анализом реакции узла на управляющее воздействие 2 .

Недостаток устройства - не обеспечивает контроль устройства в динамике работы, кроме того, оно может

5 работать с устройством ограниченной конфигурации.

Наиболее близким к предлагаемому является устройство для программного контроля, содержгицее блок ввода,

20 блок выработки тестовых наборов, коммутатор, блок измерений, операционный блок, блок синхронизации, блоки управления, регистрации и контроля программ, блок сравнения и контролируемый блок, при этом блок выработки тестовых наборов через контролируемый блок и коммутатор соединен с блоком измерений и операционным блохом, а блрк ввода, к которому может

30 подключаться ЭЦВМ,через блок управления соединено блоками сравнения, контроля программ, выработки тестовых наборов, измерения, коммутатором и операционным блоком; второй вход блока контроля программ соедннен с сигнальными выходами этих блоков. Устройство обеспечивает проверку и отработку узлов (блоков) путем Формирования управлягаиих сигналов с последукчдим измере-нием реакции на управляющее воздействие З ,

Недостатки известного устройства блок выработки тестовых наборов может соединяться с контрольными блоками ограниченной конфигурации (т.е. имеющими строго ограниченные и идентичные координаты и число точек соединения) , не обеспечивается проведение оптимизации принятых решений для отдельных блоков и устройств, содержщих несколько блоков. Кроме того, не обеспечивается надежный (т.е. непрерывный) контроль устройства в динамике работы, особенно в тех случаях, когда сокраь ается длительность управляющих сигналов и возрастает частота их следования, что приводит к невысокой достоверности контроля проверяемого узла.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство, содержащее блок управления, блок генерации стимулирующих воздействий, блок преобразования измеряемых параметров во временной интервал, блок измерения времени , измеритель точного времени коммутатор и блок сопряжения, первый выход которого соединен с командным входом блока управления, выход управления сти1чулирующими воздействиями и первый выход следования операций которого подключен соответственн к первому и BTOpoiV входам блока генерации стимулирующих воздействий, первый выход которого является информационным выходом устройства, второй выход блока генерации стимулирующих воздействий соединен с первым сигнальным входом блока управления, измерительный выход которого подключен к первому управляющему входу блока преобразования измеряемых параметров во временной интервал, выход которого соединен с первым входом измерителя точного времени, третий Управляющий вход которого и второй сихнальный вход блока управления подключены к управлякяцему выходу блока преобразования измеряемых папаметров во временной интервал, перилй управляющий вход, сигнальный выход и второй вход измерителя точного времени соединены соответственно со вторым выходом следования операций и с третьим сигнальным входом блока управления и со вторым выходом коммутатора, первый управляющий вход

сигнальный выход и третий вход которого подключены соответственно к третьему выходу следования операций, к четвертом сигнальному входу и к выходу управления коммутатором блока управления, введены блок -масштабных преобразований, блок оптимизации блок выбора цепей, блок коммутации стимулирующих воздействий, блок датчиков,блок анализаторов активности, блок приоритетов,регистр адресов, блок адаптивного контроля, блок управления выдачей информации и элемен ИЛИ, причем первая группа выходов блока масштабных преобразований подключена к первой группе входов блока оптимизации, к первой группе входов блока коммутации стимулирующих воздействий и к группе входов блока датчиков , группа выходов которого подключена ко второй группе входов блок коммутации стимулирующих воздействий и к группе входов блока анализаторов активности, выход которого соединен с входом блока измерения и с первым входом коммутатора, первый выход которого соединен через блок приоритетов и регистр адресов с первым входоми непосредственно со вторым входом блока адаптивного контроля, выход которого подключен к третьему входу элемента ИЛИ, первый и второй входы которого соединены соответственно с информационным выходом блока -управления и с выходом измерителя точного времени, выход элемента ИЛИ подключен ко входу блока сопряжения, первый управляющий вход и третий выход которого соединены соответственно с выходом и входом обратной связи блока управления выдачей информации, первый, втдрой и третий управляющие выходы которого подключены ко входам обратной связи соответственно блока адаптивного контроля, измерителя точного времени и блока управления , а также ко второму , третьему и четвертому управляющим входам блока сопряжения, вход, обратной связи и второй выход которого соединены соответственно с управляющим выходом и входом блока выбора цепей, первый выход которого подключен ко второму входу коммутатора и к коммутирующему входу блока управления и к четвертому входу блока коммутации стимулирующих воздействий, первый выход и третий вход которого соединенысоответственно со входом блока преобразования измеряемых параметров во временной интервал и с третьим выходом блока генераций стимулирующих воздействий, второй, третий и сигнальный выходы блока коммутации стимулирующих воздействий подключены соответственно к адресному входу, ко входу контроля операций и к пятому сигнальному входу блока управления, четвертый выход

следования операций которого подключен к управляющему входу блока масштабных преобразований, второй выход иуправляющий выход которого соединены соответственно с пятым входом hi управляющим входом блока коммутации стимулирующих воздействий, первый,и третий управляющие входы которюго подключены соответственно к пятому и шестему выходам следования операций блока управления, выход принака окончания операции которого подключен к четвертому управляющему входу блока коммутации стимулирующих воздействий и второму управляющему входу блока выбора цепей, второй выход и первый управляющий вход которого соединены соответственно со вторым входом блока оптимизации и с седьмом выходом следования .операций блока управления, запросный выход которого подключен к третьему входу блока управления выдачей информации, первый и второй вход которого подключены соответственно к первому управляющему выходу блока адаптивного контроля и к управляющему.выходу измерителя точного времени , выход блока измерения времени подключен к третьи входам.измерителя точного времени и блока адаптивного контроля, выход командного сброса блока управления подключен к вторым управляющим входам коммутатора, измерителя точного времени и блока коммутации стимулирующих воздействий, при этом группа входов блока масштабных преобразований является входом устройства и служит для подключения к выходам объекта контроля.

Блок масштабных преобразований устройства содержит узел преобразования координат внешних цепей, узел делителей и узел проверки соединений при этом группа входов и первая группа выходов узла преобразования координат внешних цепей является соответственно группой входов и первой группкой выходов блока масштабных преобразований, вторая группа выходов, вторая группа входов и третья группа выходов узла преобразования координат внешних цепей соединены соответственно с группой входов, с группой выходов узла делителей и с группой входов узла проверки соединений, управляющий вход, управлямчий выход и группа выходов которого являются соответственно управляющим входом, управляющим выходом и вторым выходом блока масштабных преобразований.

Коммутатор устройства содержит регистр управления, первый и второй элемент И и п каналов вторю го выхода, каждый из которых содержит регистр, элемент и, элемент ИЛИ и формирователь контрольного сигнала, при этом группа входов элемента Л

является первым входом коммутатора, каждый из входов этой группы подключен соответственно к элементу И каждого из каналов, выходы каждого из которых подключены к соответствующим входам элемента ИЛИ своего канала, выходы элементов ИЛИ всех каналов являются вторым выходом коммутатора, группа входов второго элемент И является вторым входом коммутатора группа выходов второго элемента И подключена к группе входов регистра управления, группа выходов которого соединена с группой управляющих входов первого элемента И, группа выходов которого является первым выходом коммутатора, кроме того, группа выходов второго элемента И соединена с соответствующими разрядами регистров каждого из каналов, группа выходов из регистра каждого из каналов подключена к группе управлякчцих входов элемента И и к группе входов формирователя контрольного сигнала своего канала, выходы Лормирователеп контрольного сигнала всех каналов являются сигнальным выходом коммутатора, первый и второй управляющие входы которого подклр)чены соответственно к управляющему входу второго элемента И и ко входам сброса регистра управления и ко входам сброса регистров каждого из каналов, управляющие входы регистров каждого из каналов в совокупности явлпьлтся третьим входом коммутатора.

Блок управления устройства содержит узел коммутации, первый и второй элементы ИЛИ, дешифратор команд, дешифратор операций, регистр операций, накопитель чисел, ключевой элемент, передающий буфер, элемент И, узел приоритетов, формирователь признака окончания команды, узел контроля программных соединений, узел контрол выполнения операций и узел управления коммутатором, при этом первый вход узла коммутации является командным входом блока управления, первый второй и третий выходы узла коммутации соединены соответственно со входом дешифратора команд, со входом регистра операций и с первым входом накопителя чисел,первый и второй выходы ключевого элемента являются соответственно выходом управления стимулирующими воздействиями и измерительным выходом блока управления, третий и четвертый выходы ключевого элемента подключены соответственно ко входу кода числа передающего буфера и ко второму входу узла контроля выполнения операций, выход и управлякяций выход накопителя чисел соединены соответственно со входом ключевого элемента и с третьим управляющим входом узла коммутации, второй управля1.вдий вход которого соединен

с управляющим выходом регистра операций, вход кода команды передакяцего буфера соединен с первым выходом дешифратора команд и с первым входом дешифратора операций, первый управляющий выход которого является первым выходом следований операций блока управления, а также подключен к первому управлягацему входу узла контрол программных соединений и ко второму управляющему входу ключевого элемент второй, четвертый, шестой и седьмой управляющие выходы дешифратора операций являются соответствующими выходами следования операций блока управления, третий управляющий выход дешифратора операций является третьим выходом следования операций блока управления, а также подключен ко вто рому управляющему входу узла, контроля программных соединений и к первому управляющему входу узла управления коммутатором, пятый управляквдий выход дешифратора операций является пятым выходом следования операций блока управления, а также подключен к третьему управляющему входу узла контроля программных соединений, выходы дешифратора операций подключен следующим образом: первый - к управляющему входу регистра Огпераций и к nepBOiviy входу первого элемента ИЛИ второй - к первому входу узла контроля выполнения операций, ко входу признака начала операции передающего буфера и ко второму входу накопителя чисел, третий - к четвертому управляющему входу узла контроля программных соединений и к первому управляющему входу ключевого элемента, четвертый - к третьему входу узла контроля выполнения операций, первый управляющий выход дешифратора команд подключен к первому управляющему входу узла коммутации, второй управляющий выход дешифратора команд является выходом командного сброса блока управления, второй выход дешифратора команд подключен к третьему входу формирователя признака окончания команды, выход которого подклю.чен ко входу признака окончания операции передающего буфера и ко входам сброса накопителя чисел и регистра операций, выход котброгО соединен с первым входом элемента И и со входом узла приоритетов, первый и второй выходы которого подключены соответственно ко вторым входам формирователя признака окончания команды и дешифратора операций, второй вход и выход первого элемента ИЛИ соединены соответственно со вторым выходом узла коммутации и со вторым входом элемента И, выход которого подключен к входу кода операции передающего буАера, первый контрольный вход которого соединен с первым выходом узла контроля выполнения

операций, второй выход которого является выходом признака окончания операций блока управления, а также подключен к входу признака окончания операции передающего буфера, к первому входу формирователя признака окончания команды, к управляющему входу дешифратора операций и к пятому управляющему входу узла контроля программных соединений, первый, второй, третий, четвертый и пятый сигнальные входы которого являются соответствующими сигнальными входами блока управления, первый, второй и третий выходы узла контроля программных соединений подключены соответственно к пятому входу узла контроля выполнения операций, ко второму контрольному входу передающего буфера и к первому входу узла управления коммутатором, первый выход которого является выходом управления коммутатором блока управления, группа входов узла контроля программных соединений объединена с группой входов второго элемента ИЛИ и является коммутирующим входом блока управления,, вход контроля операций которого подключен к четвертому входу узла контроля выполнения операций, шестой и седьмой входы которого соединены соответственно со вторым и третьим выходами узла управления коммутатором, вход обратной связи, первый выход, второй выход и группа входов передающего буфера являются соответственно входом обратной связи, информационным выходом и запросным выходом и адресным входом блока 5 правления.

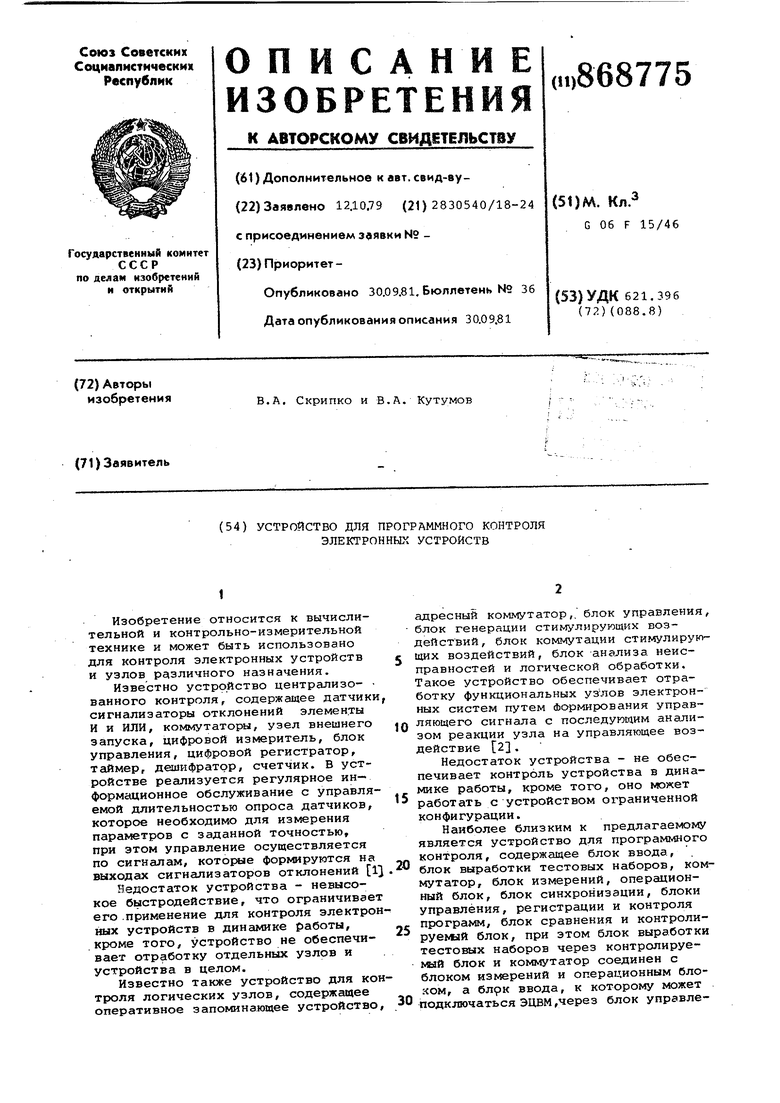

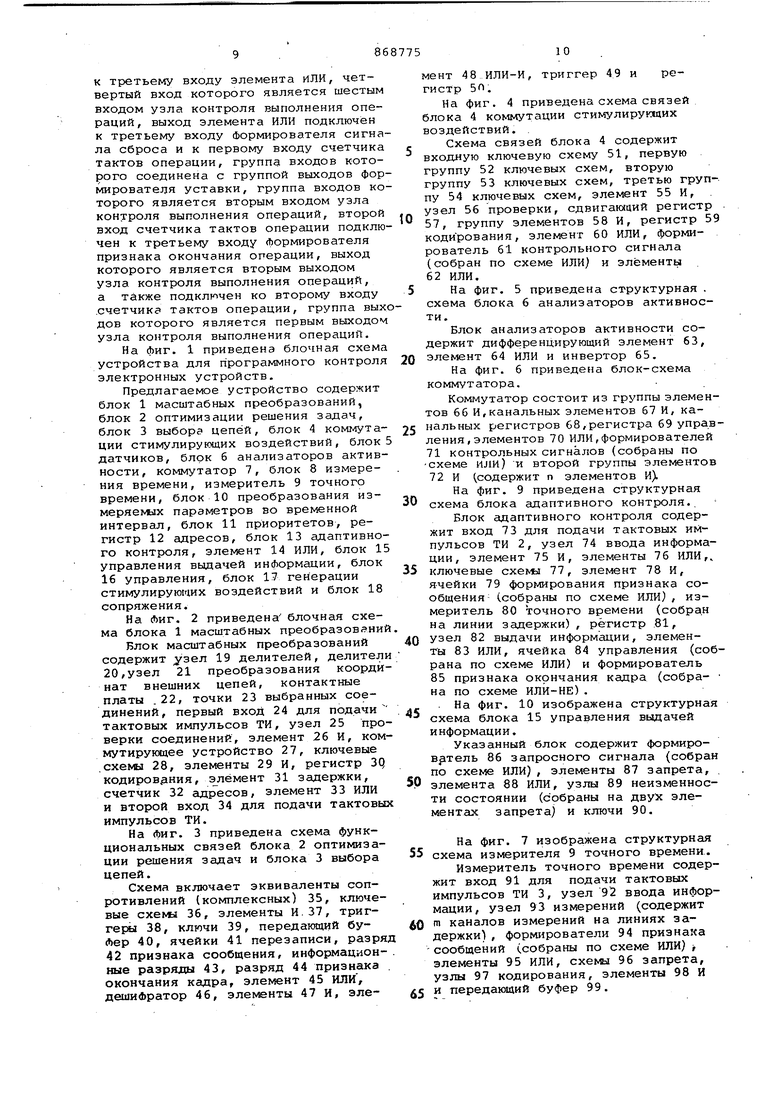

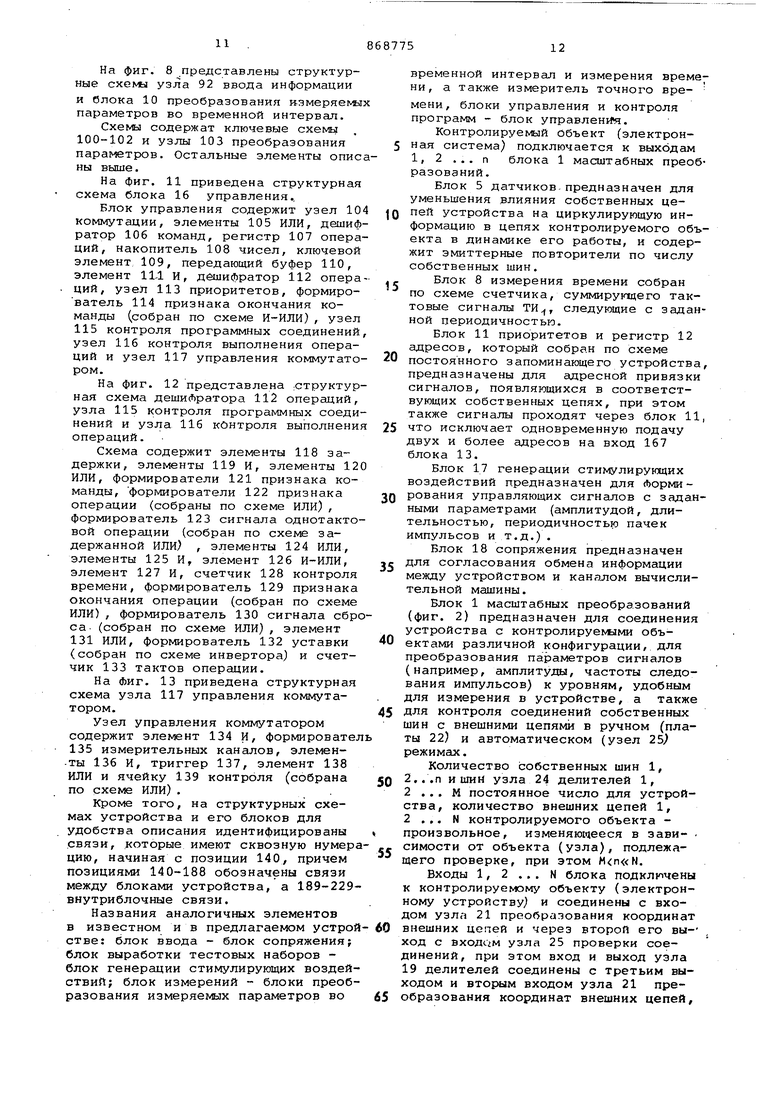

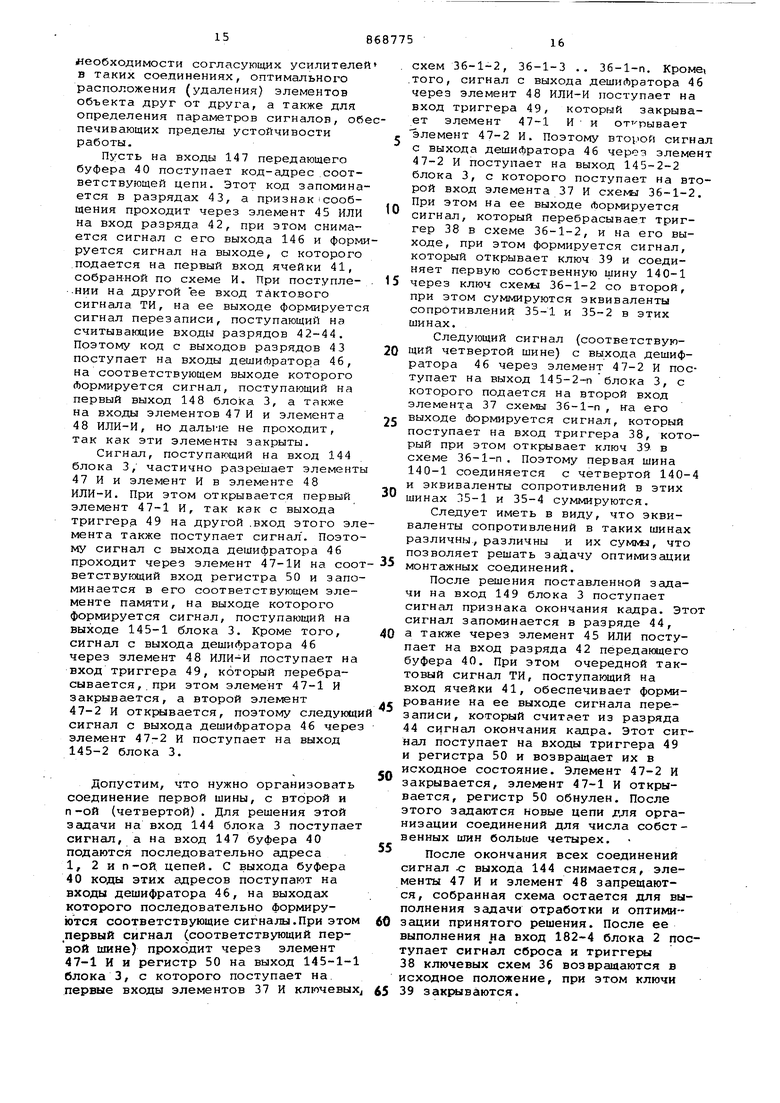

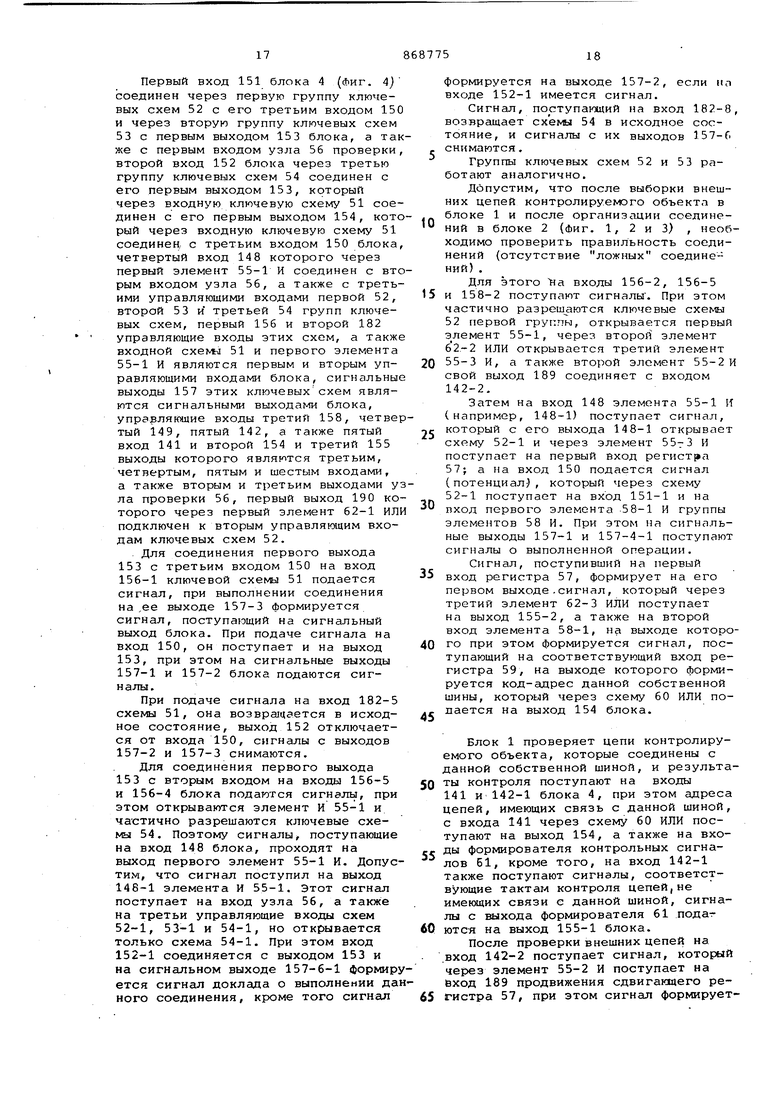

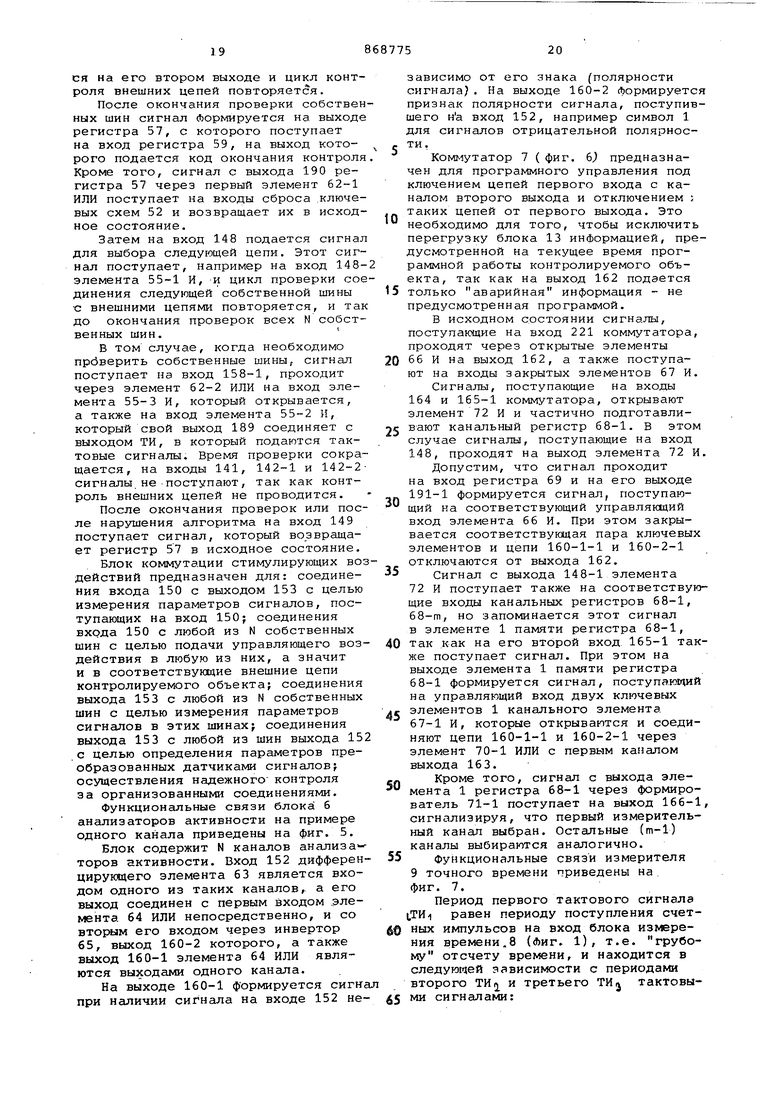

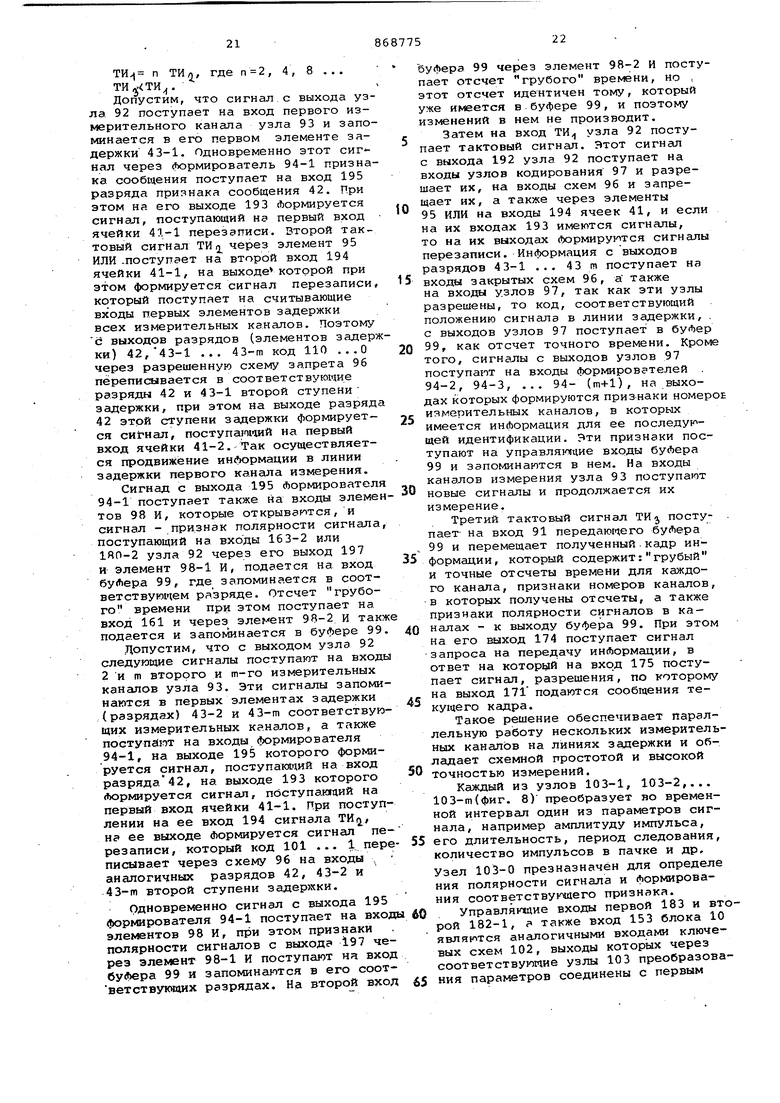

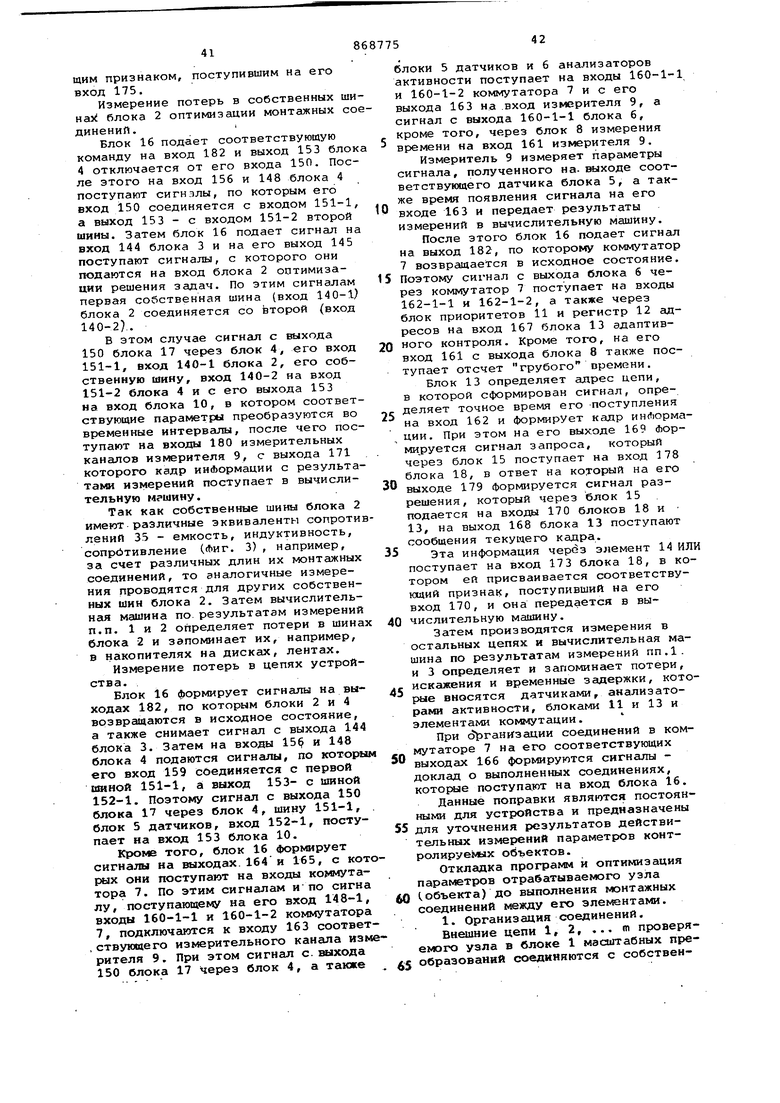

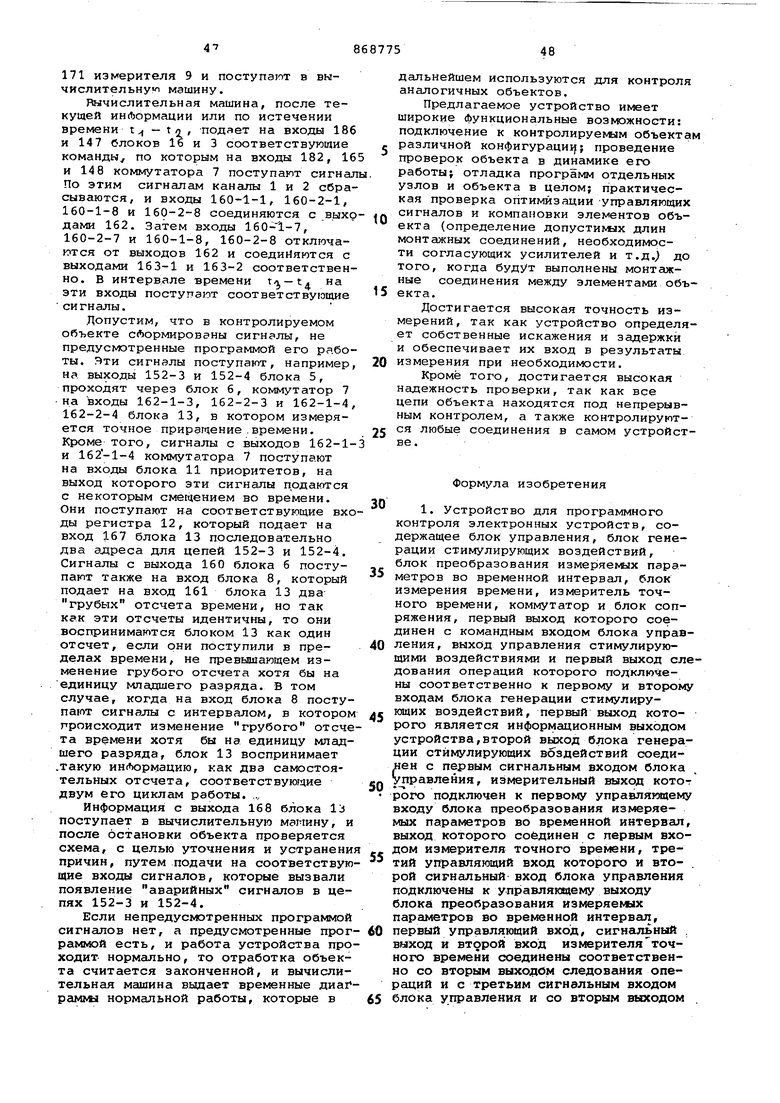

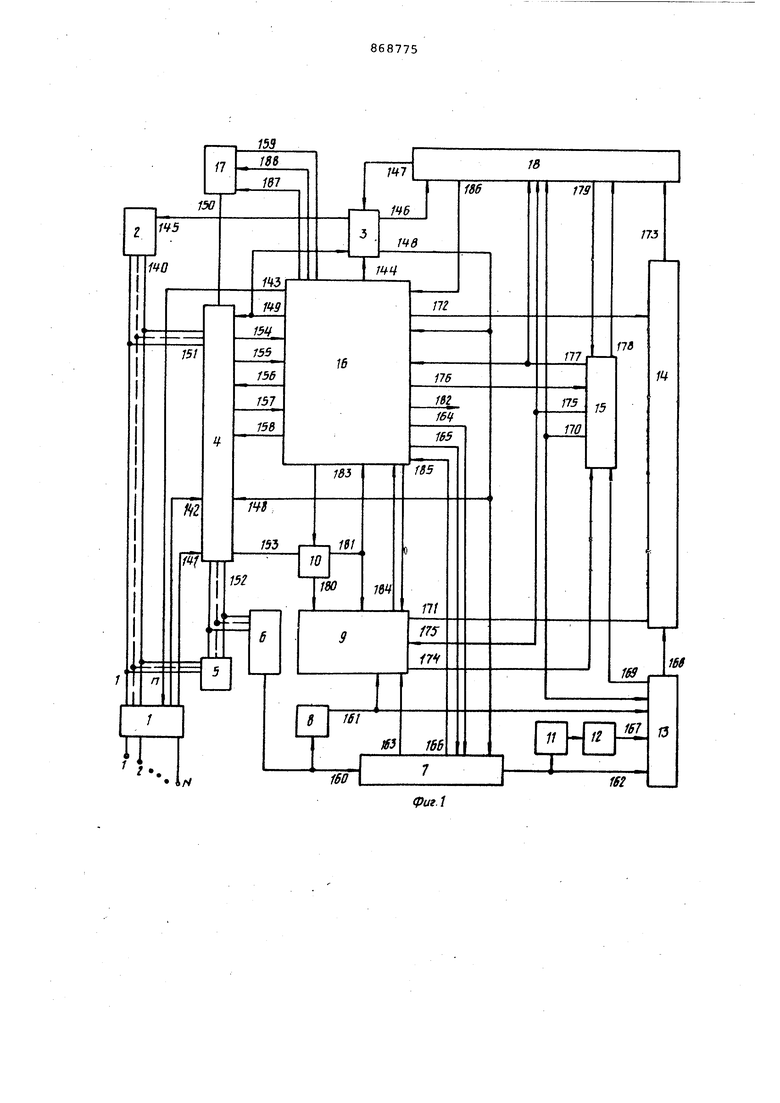

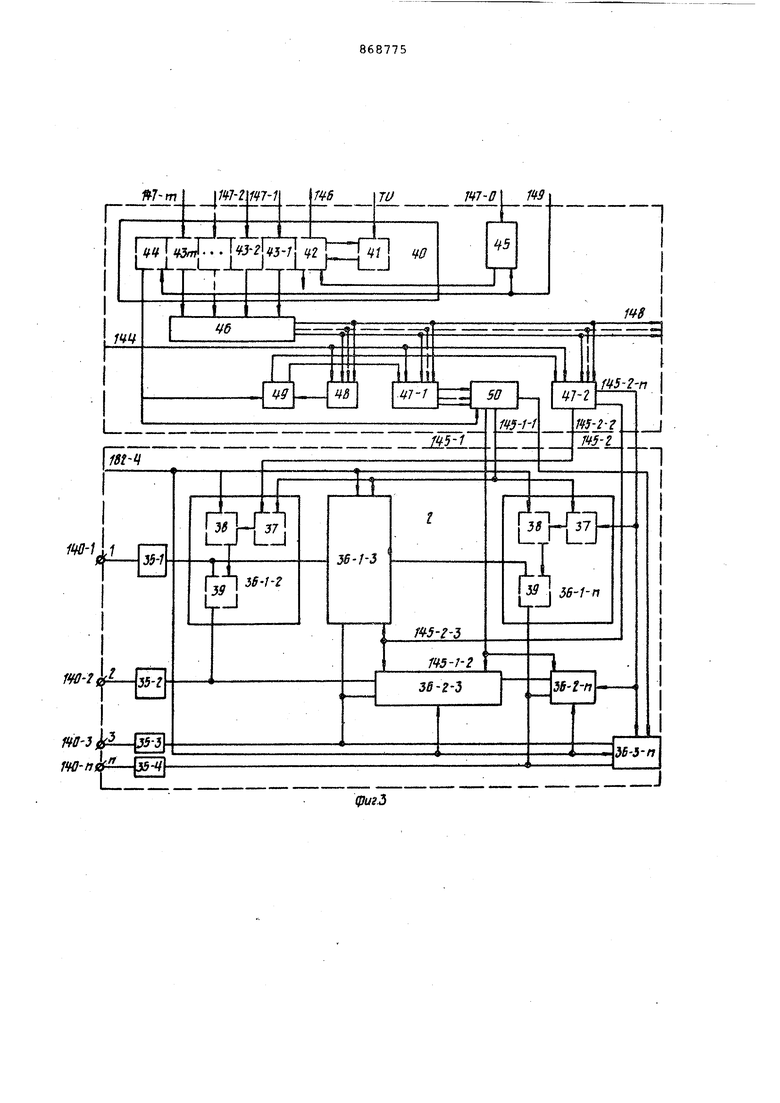

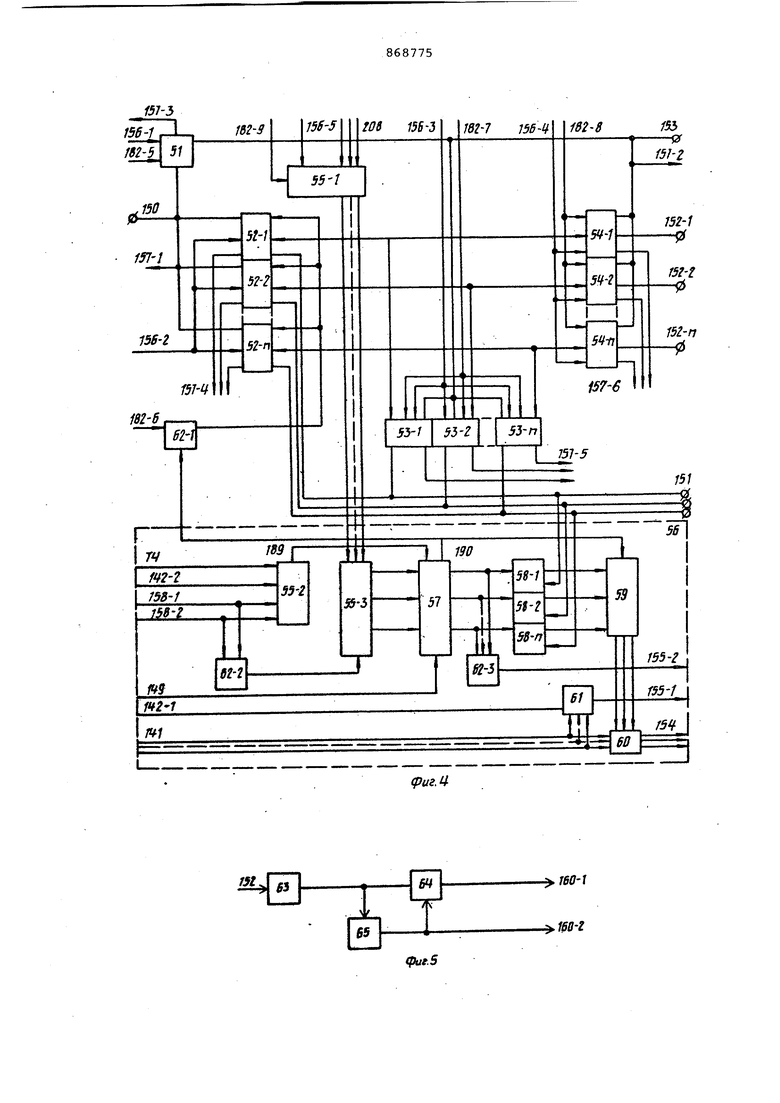

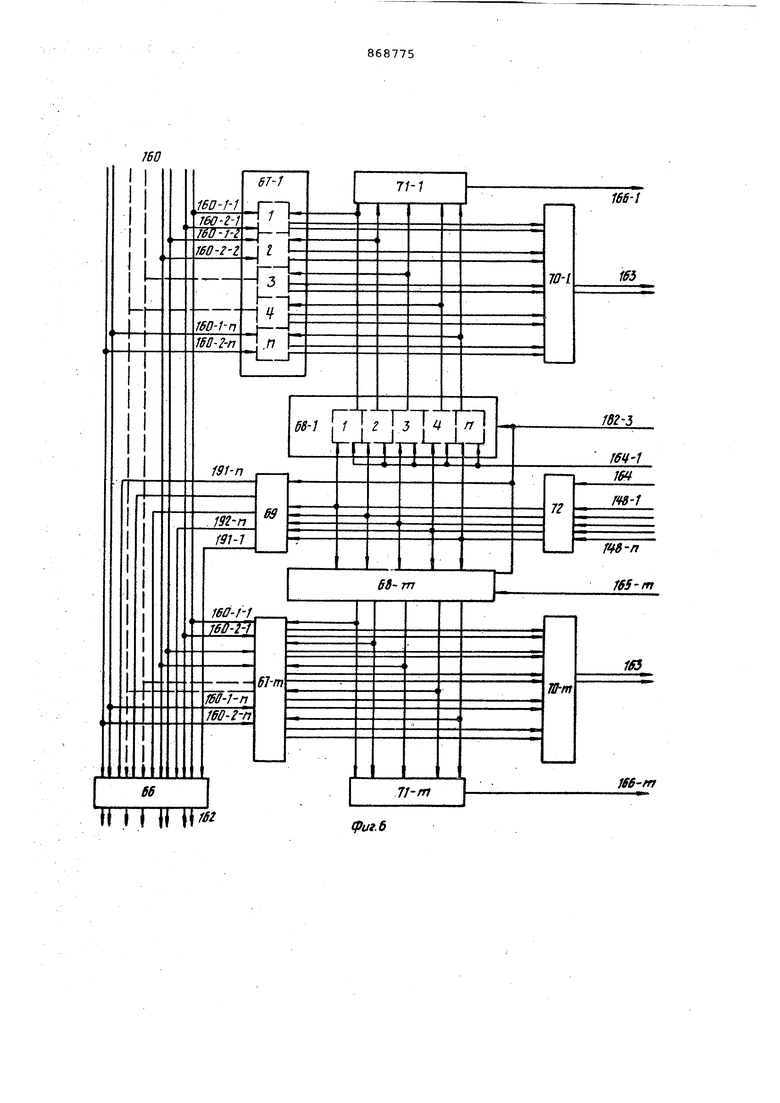

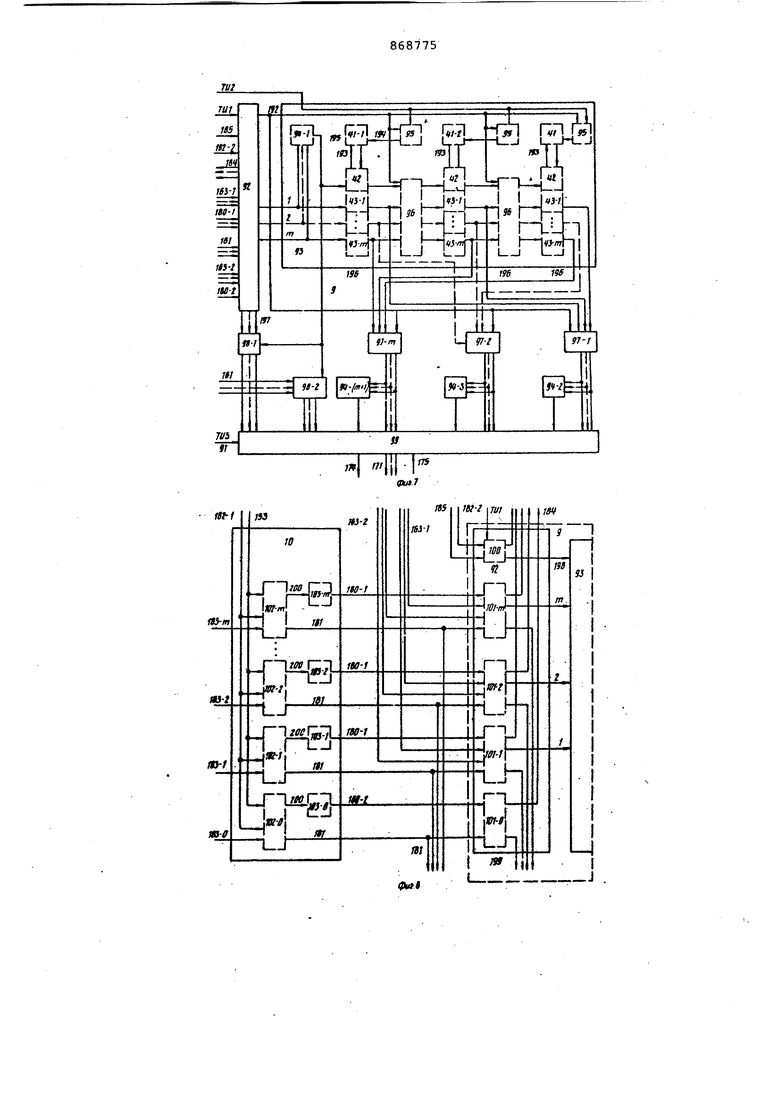

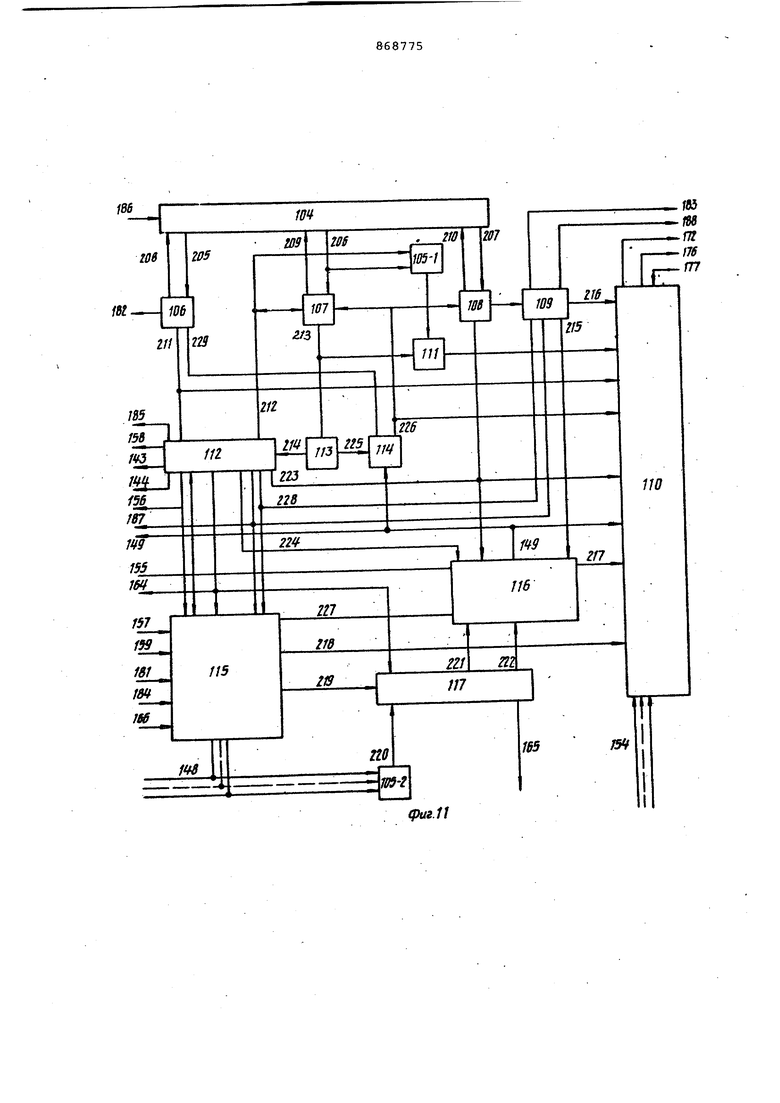

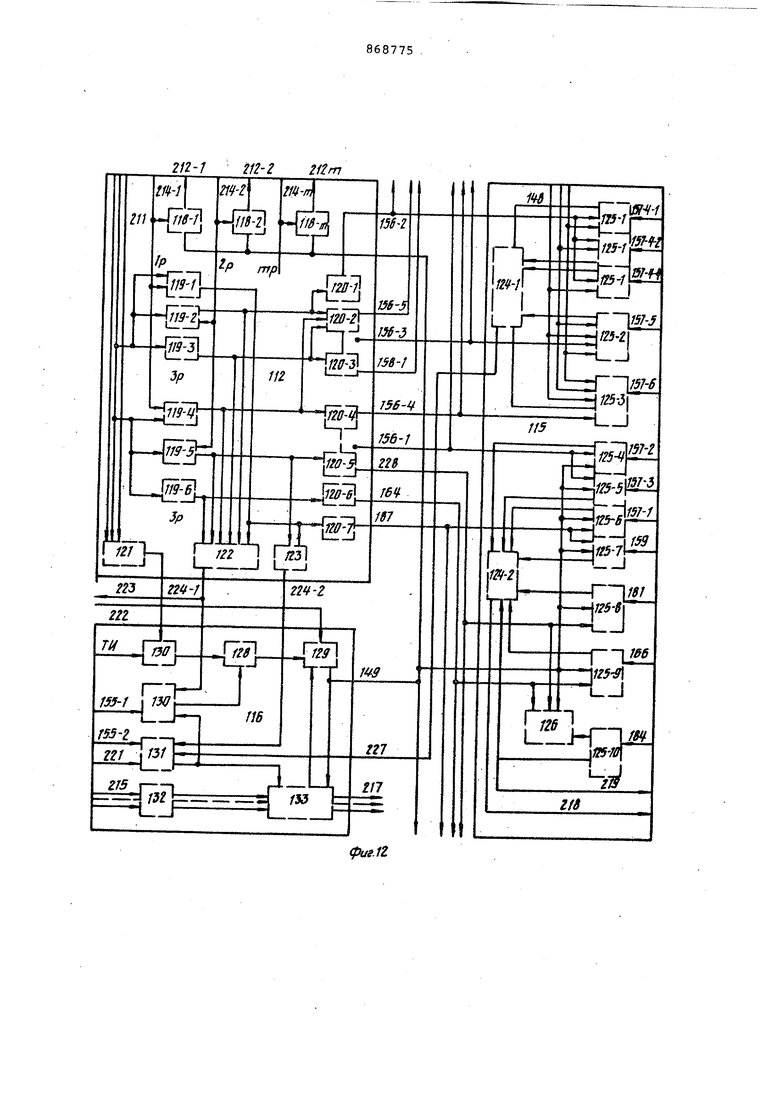

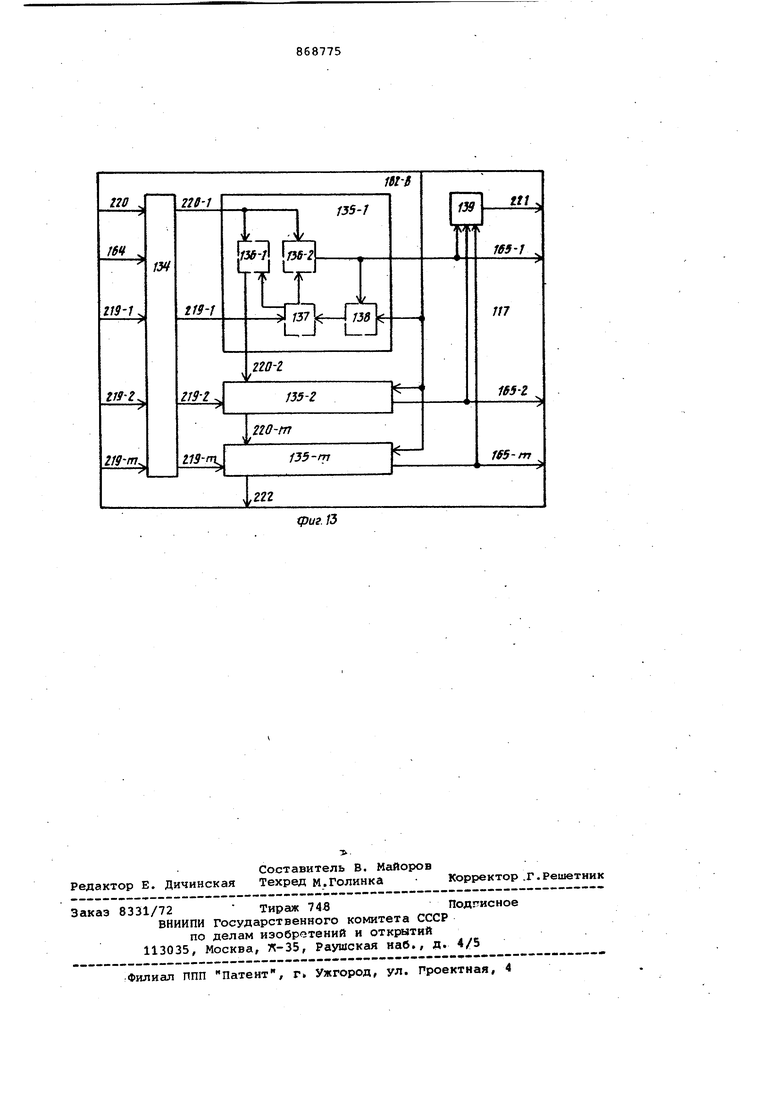

Кроме того, узел контроля выполнения операций устройства содержит элемент И, счетчик контроля времени, формирователь признака окончания операции, формирователь сигнала сброса, элемент ИЛИ, формирователь уставки и счетчик тактов операции, при этом на первый вход элемента И подаются тактовые импульсы, выход его подключен к первому входу счетчика контроля времени, выход которого соединен с первым входом формирователя признака окончания операции, второй вход которого является седьмым входом узла контроля выполнения операций, первый вход которого подключен к первому входу формирователя сигнала сброса, выход которого соединен со вторым входом счетчика контроля времени, пятый вход узла контроля выполнения операций является первым входом элемента ИЛИ, второй вход которого, а также второй вход элемента И являются соответственно второй и первой шинами третьего входа узла контроля выполнения операций, четвертый вход которого также разделен на две шины, первая из которых подключена к второму входу формирователя сигнала сброса, а вторая к третьему входу элемента ИЛИ, четвертый вход которого является шестым входом узла контроля выполнения операций, выход элемента ИЛИ подключён к третьему входу Формирователя сигна ла сброса и к первому входу счетчика тактов операции, группа входов которого соединена с группой выходов фор мирователя уставки, группа входов ко торого является вторым входом узла контроля выполнения операций, второй вход счетчика тактов операции подклю чен к третьему входу формирователя признака окончания операции, выход которого является вторым выходом уэла контроля выполнения операций, а также подключен ко второму входу счетчика тактов операции, группа вых дов которого является первым выходом узла контроля выполнения операций. На фиг. 1 приведена блочная схем устройства для программного контроля электронных устройств. Предлагаемое устройство содержит блок 1 масштабных преобразований, блок 2 оптимизации решения задач, блок 3 выбора цепей, блок 4 комг тации стимулирующих воздействий, блок датчиков, блок б анализаторов активности, коммутатор 7, блок 8 измерения времени, измеритель 9 точного времени, блок 10 преобразования измеряемых параметров во временной интервал, блок 11 приоритетов, регистр 12 адресов, блок 13 адаптивно го контроля, элемент 14 ИЛИ, блок 1 управления выдачей информации, блок 16 управления, блок 17 генерации стимулирующих воздействий и блок 18 сопряжения. На Лиг. 2 приведена блочная схема блока 1 масштабных преобразовани Блок масштабных преобразований содержит узел 19 делителей, делител 20,узел 21 преобразования коорди нат внешних цепей, контактные платы .22, точки 23 выбранных соединений, первый вход 24 для подачи тактовых импульсов ТИ, узел 25 про верки соединений, элемент 26 И, ком мутирующее устройство 27, ключевые .схемы 28, элементы 29 И, регистр 3Q кодировдния, элемент 31 задержки, счетчик 32 адресов, элемент 33 ИЛИ и второй вход 34 для подачи тактовы импульсов ТИ. На Лиг. 3 приведена схема функциональных связей блока 2 оптимизации решения задач и блока 3 выбора цепей. Схема включает эквиваленты сопротивлений (комплексных) 35, ключевые схемы 36, элементы И. 37, триггерл 38, ключи 39, передающий буЛер 40, ячейки 41 перезаписи, разряд 42 признака сообщения, информационные разряды 43, разряд 44 признака окончания кадра, элемент 45 ИЛИ, дешифратор 46, элементы 47 И, элемент 48 ИЛИ-И, триггер 49 и регисТр 5(1. На фиг. 4 приведена схема связей блока 4 коммутации стимулиругацих воздействий. Схема связей блока 4 содержит входную ключевую схему 51, первую группу 52 ключевых схем, вторую группу 53 ключевых схем, третью группу 54 ключевых схем, элемент 55 И, узел 56 проверки, сдвигаю(ций регистр 57, группу элементов 58 И, регистр 59 кодирования, элемент 60 ИЛИ, формирователь 61 контрольного сигнала (собран по схеме ИЛИ) и элементы 62 ИЛИ. На фиг. 5 приведена структурная . схема блока 6 анализаторов активности. Блок анализаторов активности содержит дифференцирующий элемент 63, элемент 64 ИЛИ и инвертор 65. На фиг. 6 приведена блок-схема коммутатора. Коммутатор состоит из группы элементов 66 И,канальных элементов 67 И, канальных регистров 68,регистра 69 управления, элементов 70 ИЛИ,формирователей 71контрольных сигналов (собраны по схеме или) и второй группы элементов 72И (содержит п элементов И). На фиг. 9 приведена структурная схема блока адаптивного контроля. Блок адаптивного контроля содержит вход 73 для подачи тактовых иМпульсов ТИ 2, узел 74 ввода информации, элемент 75 И, элементы 76 ИЛИ,, ключевые схемы 77, элемент 78 И, ячейки 79 формирования признака сообщения (собраны по схеме ИЛИ) , измеритель 80 точного времени (собран на линии задержки), регистр 81, узел 82 выдачи информации, элементы 83 ИЛИ, ячейка 84 управления (собрана по схеме ИЛИ) и формирователь 85 признака окончания кадра (собра- на по схеме ИЛЙ-НЕ). На фиг. 10 изображена структурная схема блока 15 управления выдачей информации. Указанный блок содержит формироВр1тель 86 запросного сигнала (собран по схеме ИЛИ), элементы 87 запрета, элемента 88 ИЛИ, узлы 89 неизменности состоянии (собраны на двух элементах запрета) и ключи 90. На фиг. 7 изображена структурная схема измерителя 9 точного времени. Измеритель точного времени содержит вход 91 для подачи тактовых импульсов ТИ 3, узел 92 ввода информации, узел 93 измерений (содержит m каналов измерений на линиях задержки) , формирователи 94 признака сообщений (собраны по схеме ИЛИ) элементы 95 ИЛИ, схеки 96 запрета, узлы 97 кодирования, элементы 98 И и передающий буфер 99. На фиг. 8 представлены структурные схемы узла 92 ввода информации и блока 10 преобразования измеряемых параметров во временной интервал. Схемы содержат ключевые схемы 100-102 и узлы 103 преобразования параметров. Остальные элементы опис ны выше. На фиг. 11 приведена структурная схема блока 16 управления., Блок управления содержит узел 10 коммутации, элементы 105 ИЛИ, дешифратор 106 команд, регистр 107 операций, накопитель 108 чисел, ключевой элемент 109, передающий буфер 110, элемент 11-1 И, дешифратор 112 опера ций, узел 113 приоритетов, формирователь 114 признака окончания команды (собран по схеме И-ИЛИ), узел 115 контроля программных соединений узел 116 контроля выполнения операций и узел 117 управления коммутатором. На фиг. 12 представлена :Структурная схема дешифратора 112 операций, узла 115 контроля программных соединений и узла 116 контроля выполнения операций. Схема содержит элементы 118 задержки, элементы 119 И, элементы 12 ИЛИ, формирователи 121 признака команды, формирователи 122 признака операции (собраны по схеме ИЛИ) , формирователь 123 сигнала однотактовой операции (собран по схеме задержанной или) , элементы 124 ИЛИ, элементы 125 И, элемент 126 И-ИЛИ, элемент 127 И, счетчик 128 контроля времени, формирователь 129 признака окончания операции (собран по схеме ИЛИ), формирователь 130 сигнала сбро са- (собран по схеме ИЛИ) , элемент 131 ИЛИ, формирователь 132 уставки (собран по схеме инвертора) и счетчик 133 тактов операции. На Фиг. 13 приведена структурная схема узла 117 управления коммутатором. Узел управления коммутатором содержит элемент 134 И, формировател 135 измерительных каналов, элемен-ты 136 И, триггер 137, элемент 138 ИЛИ и ячейку 139 контроля (собрана по схеме ИЛИ) .. Кроме того, на структурных схемах устройства и его блоков для удобства описания идентифицированы .связи, которые имеют сквозную нумера цию, начиная с позиции 140, причем позициями 140-188 обозначены связи между блоками устройства, а 189-229внутриблочные связи. Названия аналогичных элементов в известном и в предлагаемом устрой стве; блок ввода - блок сопряжения; блок выработки тестовых наборов блок генерации стимулирующих воздействий; блок измерений - блоки преобразования измеряемых параметров во временной интервал и измерения времени, а также измеритель точного времени, блоки управления и контроля программ - блок управление. Контролируемый объект (электронная система) подключается к выходам 1, 2 ... п блока 1 масштабных преобразований. Блок 5 датчиков.предназначен для уменьшения влияния собственных цепей устройства на циркулирующую информадию в цепях контролируемого объекта в динамике его работы, и содержит эмиттерные повторители по числу собственных шин. Блок 8 измерения времени собран по схеме счетчика, суммирующего тактовые сигналы ТИ, следующие с заданной периодичностью. Блок 11 приоритетов и регистр 12 адресов, который собран по схеме постоянного запоминающего устройства, предназначены для адресной привязки сигналов, появляющихся в соответствующих собственных цепях, при этом также сигналы проходят через блок 11, что исключает одновременную подачу двух и более адресов на вход 167 блока 13. Блок 17 генерации стимулирующих воздействий предназначен для Формирования управляющих сигналов с заданными параметрами (амплитудой, длительностью, периодичностью пачек импульсов и т.д.). Блок 18 сопряжения предназначен для согласования обмена информации между устройством и каналом вычислительной машины. Блок 1 масштабных преобразований (фиг. 2) предназначен для соединения устройства с контролируемыми объектами различной конфигурации, для преобразования па эаметров сигналов (например, амплитуды, частоты следования импульсов) к уровням, удобным для измерения в устройстве, а также для контроля соединений собственных шин с внешними цепями в ручном (платы 22) и автоматическом (узел 25 режимах. Количество собственных шин 1, 2,..п и шим узла 24 делителей 1, 2 ... М постоянное число для устройства, количество внешних цепей 1, 2 ... N контролируемого объекта произвольное, изменяющееся в зави- симости от объекта (узла), подлежащего проверке, при этом . Входы 1, 2 ... N блока подключены к контролируемому объекту (электронному устройству) и соединены с входом узла 21 преобразования координат внешних цепей и через второй его вы- , ход с входсгм узла 25 проверки соединений, при этом вход и выход узла 19 делителей соединены с третьим выходом и вторым входом узла 21 преобразования координат внешних цепей.

(Первый выход которого является первы выходом 140-1, 140-2 ... 140-п блока второй выход 141, управляющий выход 142 и управлянвдий вход 143 которого являются соответствукяцикм выходагди и входом узла 25 проверки соединений.

В узле 21 преобразования координат внешних цепей собственные шины 140-1, 140-2,...140-п первого выхода соединяются с внешними цепями i, 2 ... N первого входа вручную, например, с помощью контзктных штырей или кнопочных переключателей, установленных в точках пересечения внешних цепей с собственными шинами устройства..

На фиг. 2 выполнены следующие соединения: первая собственная шина 140-1 соединена точками 23 с второй (2) внешней цепью через узел 19 делителей, вторая собственная шина 140-2 соединена точками 23 с первой (1) и М-ой (N)внешними цепями непосредственно. Поэтому сигналы с внешних цепей (1 и М) подаются на выход в собственную шину 140-2 (или, наоборот - из шины 140-2 в цепи 1 и N) а сигнал с внешней цепи (2) проходит через узел 19 и его делитель 20-2 на выход в собственную шину 140-1. Кроме того, сигналы внешних цепей 1, 2...N блока поступает также на вход коммутирующего устройства 27, которое обеспечивает автоматический контроль соединений.

Для проведения контроля соединений в собственную шину 140-х подается потенциал, который поступает через узел 21 во внешнюю цепь х контролируемого объекта. После этого на управляющий вход 143 узла 25 подается сигнал, который разрешает работу коммутирующего устройства 27 и открывает элемент 26 И. Тактовые сигналы ТИ проходят через элемент И 26 и ключевые схелвл 28 транзистом на выходе 142-1, а также на входы коммутирующего устройства 27, счетчика 32 и элемента задержки 31. При этом в счетчике 32 запоминается единица, которая сигналом с выхода элемента задержки 31 через схему 33 ИЛИ подается на второй выход 141 блока, как первый адрес группы внешний цепей. Одновременно коммутирующее устройство 27 подключает первую группу из m внешних цепей к своим выходам, которые соединены с первыми управляющими входами соответствующих ключевых схем 28 и первыми входами элементов 29 И. При этом ключевые схемы 28 осевого состояния не измеНЯ1ПТ, если на их первые управляющие входы сигнал не поступает(т.е. в соответствукией внешней цепи нет потенциала), и ключевая схема 28 изменяет свое состояние, если на ее первый управляющий вход поступа-

ВТ сигнал. В этом случае ее вход соединяется с другими входами, каждый из которых подключен к второму входу каждого элемента 29 И, поэтому второй тактовый сигнал ТИ проходит через элемент 26 И на вход ключевой схемы 28 и, например, через схему 28-1 на второй вход элемента 29-1 И, при этом на его выходе формируется сигнал, поступающий на соответствующий вход регистра 30, на выход которого

0 подается код соответствующий цепи в данной группе из m внешних цепей. Этот код через элемент 33 ИЛИ подается на выход 141.

Кроме того, сигнал с выхода элеsмента 29-1 И поступает также на второй управляющий вход схемы 28-1, которая возвращается в исходное состояние. Поэтом третий тактовый сигнал ТИ проходит исходное состояние

0 через элемент 26 И, схему 28-1, а также 28-2 .,. 28-п, если они остались в исходном состоянии, на выход 142-1 блока, на входы счетчика 32 и элемента 31 задержки, при этом на выход счетчика 32 подается код 2,

5 соответствующий второй группе из m внешних цепей. Кроме того, сигнал с выхода схемы 28-т поступает на вход устройства 27, которое подключает к своим выходам вторую (очередную

0 группу из m внешних цепей.

После подключения последней группы сигнал подается на выход 142-2 коммутирующего устройства 27. После этого потенциал подается в следующую

5 собственную шину, например 140 (х+1) , и повторяется контроль соединений .

Произвольный выбор внешних цепей выполняется вручную.

0

Кроме того, сигналы в цепях,контг. ролируемого объекта имеют различные параметры, что налагает различные требования на ;-собственные шины устройства. Такие требования часто противоречивые и трудно совместимые,

5 так как комплексное сопротивление (реактивное и активное соединений приводит к искажению и потере слабых сигналов, поэтому наличие узла делителей в блоке позволяет частично

0 компенсировать это противоречие, а свободный выбор внешних цепей позволяет сигналы с разными параметрами подключать к собственным шинам с различными характеристиками.

5

Блок 3 выбора цепей (фиг.З) реализует функции адресного коммутатора с последующим распределением сигналов между выходами 148, 145-1 и 145-2 по заданному алгоритму.

Блок 2 оптимизации решения задач предназначен для организации заданных соединений в контролируемом объекте, до выполнения монтажных соединений на объекте, с целью оптимизации длины таких соединений.

5 необходимости согласующих усилителе в таких соединениях, оптимального расположения (удаления) элементов объекта друг от друга, а также для определения параметров сигналов, об печивающих пределы устойчивости работы. Пусть на входы 147 передающего буфера 40 поступает код-адрес соответствующей цепи. Этот код запомина ется в разрядах 43, а признак сообщения проходит через элемент 45 ИЛИ на вход разряда 42, при этом снимается сигнал с его выхода 146 и форм руется сигнал на выходе, с которого подается на первый вход ячейки 41, собранной по схеме И. При поступле.НИИ на другой ее вход тйктового сигнала ТИ, на ее выходе формируетс сигнал перезаписи, поступающий на считывающие входы разрядов 42-44. Поэтому код с выходов разрядов 43 поступает на входы дешиЛратора 46, на соответствующем выходе которого Нормируется сигнал, поступающий на первый выход 148 блока 3, а также на входы элементов 47 И и элемента 48 ИЛИ-И, но дальпе не проходит, так как эти элементы закрыты. Сигнал, поступающий на вход 144 блока 3, частично разрешает элемент 47 И и элемент И в элементе 48 ИЛИ-И. При этом открывается первый элемент 47-1 И, так как с выхода триггер.а 49 на другой .вход этого эл мента также поступает сигнал . Поэто му сигнал с выхода дешифратора 46 проходит через элемент 47-1И на соо ветствующий вход регистра 50 и запо минается в его соответствующем элементе памяти, на выходе которого формируется сигнал, поступающий на выходе 145-1 блока 3. Кроме того, сигнал с выхода дешифратора 46 через элемент 48 ИЛИ-И поступает на вход триггера 49, который перебрасывается, . при этом элемент 47-1 И закрывается, а второй элемент 47-2 И открывается, поэтому следующ сигнал с выхода дешифратора 46 чере элемент 47-2 И поступает на выход 145-2 блока 3. Допустим, что нужно организовать соединение первой шины, с второй и п-ой (четвертой). Для решения этой задачи на вход 144 блока 3 поступае сигнал, а на вход 147 буфера 40 подаются последовательно адреса 1, 2 и п-ой. цепей. С выхода буфера 40 коды этих адресов поступают на входы дешифратора 46, на выходах которого последовательно формируются соответствующие сигналы.При это первый сигнал (соответствующий первой шине) проходит через элемент 47-1 И и регистр 50 на выход 145-1блока 3, с которого поступает на первые входы элементов 37 И ключевы схем 36-1-2, 36-1-3 .. 36-1-п. Кроме, .того, сигнал с выхода дещиЛратора 46 через элемент 48 ИЛИ-И поступает на вход триггера 49, который закрывает элемент 47-1 И и от рывает элемент 47-2 И. Поэтому второй сигнал с выхода дешифратора 46 через элемент 47-2 И поступает на выход 145-2-2 блока 3, с которого поступает на второй вход элемента 37 и cxeNtj 36-1-2. При этом на ее выходе Нормируется сигнал, который перебрасывает триггер 38 в схеме 36-1-2, и на его выходе, при этом формируется сигнал, который открывает ключ 39 и соединяет первую собственную шину 140-1 через ключ схемы 36-1-2 со второй, при этом суммируются эквиваленты сопротивлений 35-1 и 35-2 в этих шинах. Следующий сигнал (соответствующий четвертой шине) с выхода дешифратора 46 через элемент 47-2 И поступает на выход 145-2-п блока 3, с которого подается на второй вход элемента 37 схемы 36-1-п , на его выходе Формируется сигнал, который поступает на вход триггера 38, который при этом открывает ключ 39 в схеме 36-1-п. Поэтому первая шина 140-1 соединяется с четвертой 140-4 и эквиваленты сопротивлений в этих шинах 35-1 и 35-4 сум1 мруются. Следует иметь в виду, что эквиваленты сопротивлений в таких шинах различны, различны и их суммл, что позволяет решать задачу оптимизации монтажных соединений. После решения поставленной задачи на вход 149 блока 3 поступает сигнал признака окончания кадра. Этот сигнал запоминается в разряде 44, а также через элемент 45 ИЛИ поступает на вход разряда 42 передающего буфера 40. При этом очередной тактовый сигнал ТИ, поступающий на вход ячейки 41, обеспечивает формирование на ее выходе сигнала перезаписи, который считает из разряда 44 сигнал окончания кадра. Этот сигнал поступает на входы триггера 49 и регистра 50 и возвращает их в исходное состояние. Элемент 47-2 И закрывается, элемент 47-1 И открывается, регистр 50 обнулен. После этого задаются новые цепи для организации соединений для числа собственных шин больше четырех. После окончания всех соединений сигнал -с выхода 144 снимается, элементы 47 И и элемент 48 запрещаются, собранная схема остается для выполнения задачи отработки и оптимизации принятого решения. После ее выполнения на вход 182-4 блока 2 поступает сигнал сброса и триггеры 38ключевых схем 36 возвращаются в исходное положение, при этом ключи 39закрывс1ются.

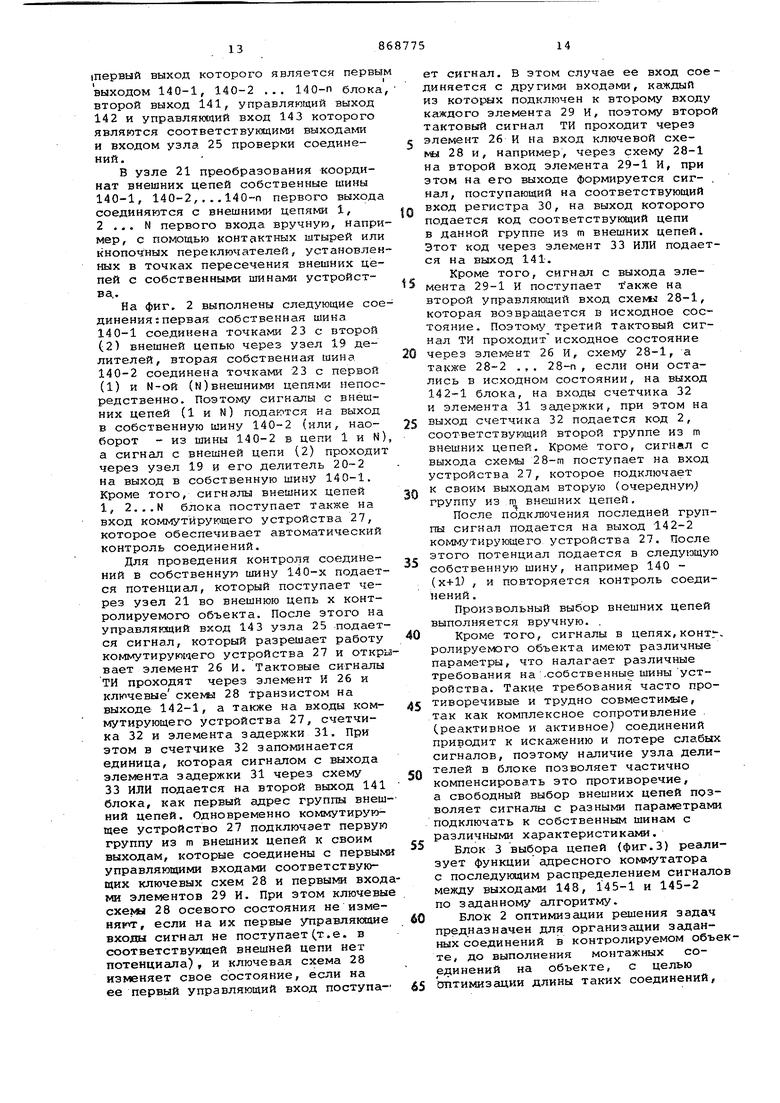

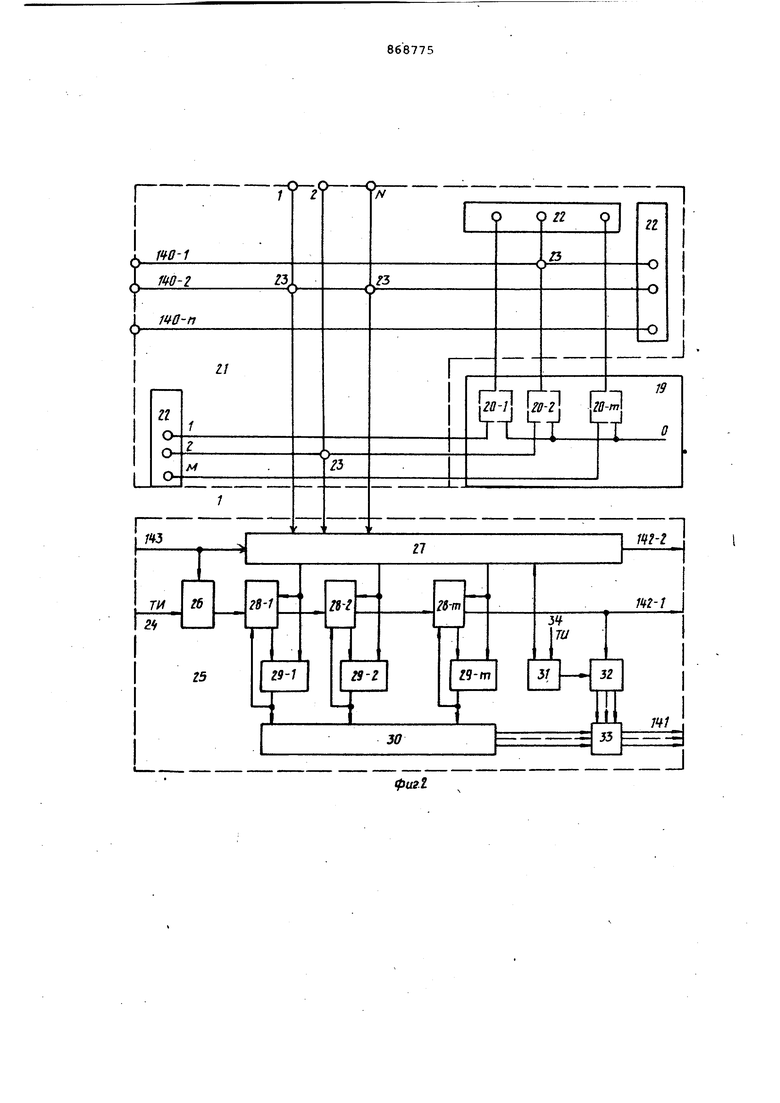

Первый вход 151 блока 4 (Фиг. 4) соединен через первую группу ключевых схем 52 с его третьим входом 150 и через вторую группу ключевых схем 53 с первым выходом 153 блока, а также с первым входом узла 56 проверки, второй вход 152 блока через третью группу ключевых схем 54 соединен с его первым выходом 153, который через входную ключевую схему 51 соединен с его первым выходом 154, который через входную ключевую схему 51 соединен с третьим входом 150 блока, четвертый вход 148 которого через первый элемент 55-1 И соединен с вторым входом узла 56, а также с третьими управляющими входами первой 52, второй 53 и третьей 54 групп ключевых схем, первый 156 и второй 182 управляющие входы этих схем, а также входной схекы 51 и первого элемента 55-1 И являются первым и вторым управляющими входами блока, сигнальные выходы 157 этих ключевых схем являются сигнальными выходат ш блока, управляющие входы третий 158, четвертый 149, пятый 142, а также пятый вход 141 и второй 154 и третий 155 выходы которого являются третьим, четвертым, пятым и шестым входами, а также вторым и третьим выходами узла проверки 56, первый выход 190 которого через первый элемент 62-1 ИЛИ подключен к вторым управляющим входам ключевых схем 52.

Для соединения первого выхода 153 с третьим входом 150 на вход 156-1 ключевой схемы 51 подается сигнал, при выполнении соединения на ,ее выходе 157-3 формируется сигнал, поступающий на сигнальный выход блока. При подаче сигнала на вход 150, он поступает и на выход 153, при этом на сигнальные выходы 157-1 и 157-2 блока подаются сигн алы.

При подаче сигнала на вход 182-5 схемы 51, она возвра1цается в исходное состояние, выход 152 отключается от входа 150, сигналы с выходов 157-2 и 157-3 снимаются.

Для соединения первого выхода 153 с вторым входом на входы 156-5 и 156-4 блока подаются сигналы, при этом открываются элемент И 55-1 и частично разрешаются ключевые схемы 54. Поэтому сигналы, поступающие на вход 148 блока, проходят на выход первого элемент 55-1 И. Допустим, что сигнал поступил на выкод 148-1 элемента И 55-1. Этот сигнал поступает на вход узла 56, а также на третьи управляющие входы схем 52-1, 53-1 и 54-1, но открывается только схема 54-1. При этом вход 152-1 соединяется с выходом 153 и на сигнальном выходе 157-6-1 формируется сигнал доклада о выполнении данного соединения, кроме того сигнал

формируется на выходе 157-2, если пп входе 152-1 имеется сигнал.

Сигнал, поступающий на вход 182-8, возвращает схемы 54 в исходное состояние, и сигналы с их выходов 157-f. снимаются.

Группы ключевых схем 52 и 53 работают аналогично.

Допустим, что после выборки внешних цепей контролируемого объекта в блоке 1 и после Организгщии соедине0ний в блоке 2 (фиг. 1, 2 и 3) , необходимо проверить правильность соединений (отсутствие ложных соединений) .

Для этого Ja входы 156-2, 156-5

5 и 158-2 поступают сигналы . При этом частично разреш аются ключевые схемы 52 первой группы, открывается первый э лемент 55-1, через второй элемент 62-2 ИЛИ открывается третий элемент 55-3 И, а также второй элемент 55-2 И

0 свой выход 189 соединяет с входом 142-2.

Затем на вход 148 элемента 55-1 И (например, 148-1) поступает сигнал, который с его выхода 148-1 открывает

5 схему 52-1 и через элемент И поступает на первый вход регист а 57; а на вход 150 подается сигнал (потенциал, который через схему 52-1 поступает на вход 151-1 и на

D вход первого элемента 58-1 И группы элементов 58 И. При этом на сигнальные выходы 157-1 и 157-4-1 поступают сигналы о выполненной операции.

Сигнал, поступивший на первый

5 вход регистра 57, формирует на его первом выходе .сигнал, который через третий элемент 62-3 ИЛИ поступает на выход 155-2, а также на второй вход элемента 58-1, на выходе которо0го при этом формируется сигнал, поступающий на соответствующий вход регистра 59, на выходе которого формируется код-адрес данной собственной шины, который через схему 60 ИЛИ подается на выход 154 блока.

5

Блок 1 проверяет цепи контролируемого объекта, которые соединены с данной собственной шиноп, и результаты контроля поступают на входы

141 и 142-1 блока 4, при этом адреса цепей, имеющих связь с данной шиной, с входа 141 через схему 60 ИЛИ поступают на выход 154, а также на входы формирователя контрольных сигналов 61, кроме того, на вход 142-1 также поступают сигналы, соответствующие тактам контроля цепей,не имеющих связи с данной шиной, сигналы с выхода формирователя 61 подагются на выход 155-1 блока.

После проверки внешних цепей на .вход 142-2 поступает сигнал, который через элемент 55-2 И поступает на Вход 189 продвижения сдвигающего регистра 57, при этом сигнал формируется на его втором выходе и цикл контроля внешних цепей повторяется.

После окончания проверки собственных шин сигнал Нормируется на выходе регистра 57, с которого поступает на вход регистра 59, на выход которого подается код окончания контроля Кроме того, сигнал с выхода 190 регистра 57 через первый элемент 62-1 ИЛИ поступает на входы сброса ключевых схем 52 и возвращает их в исходное состояние.

Затем на вход 148 подается сигнал для выбора следующей цепи. Этот сигнал поступает, например на вход 148элемента 55-1 И, и цикл проверки соединения следующей собственной шины -с внешними цепями повторяется, и так до окончания проверок всех N собственных шин.

В том случае, когда нео бходимо прбверить собственные шины, сигнал поступает на вход 158-1, проходит через элемент 62-2 ИЛИ на вход элемента 55-3 И, который открывается, а также на вход элемента 55-2 И, который свой выход 189 соединяет с выходом ТИ, в который подаются тактовые сигналы. Время проверки сокращается, на входы 141, 142-1 и 142-2сигналы не-поступают, так как контроль внешних цепей не проводится.

После окончания проверок или после нарушения алгоритма на вход 149 поступает сигнал, который возвращает регистр 57 в исходное состояние.

Блок коммутации стимулирующих воздействий предназначен для: соединения входа 150 с выходом 153 с целью измерения параметров сигналов, поступающих на вход 150; соединения входа 150 с любой из N собственных шин с целью подачи управляющего воздействия в любую из них, а значит и в соответствующие внешние цепи контролируемого объекта; соединения выхода 153 с любой из N собственных шин с целью измерения параметров сигналов в этих шинах; соединения выхода 153 с любой из шин выхода 152 с целью определения параметров преобразованных датчиками сигналов; осуществления надежного- контроля за организованными соединениями.

Функциональные связи блока б анализаторов активности на примере одного канала приведены на фиг. 5.

Блок содержит N каналов анализа-торов активности. Вход 152 дифференцирукядего элемента 63 является входом одного из таких каналов, а его выход соединен с первым входом элемента. 64 ИЛИ непосредственно, и со вторым его входом через инвертор 65, выход 160-2 которого, а также выход 160-1 элемента 64 ИЛИ являются выходами одного канала.

На выходе 160-1 формируется сигка при наличии сигнала на входе 152 независимо от его знака (полярности сигнала). На выходе 160-2 формируется признак полярности сигнала, поступившего на вход 152, например символ 1 для сигналов отрицательной полярности.

Коммутатор 7 ( фиг. d) предназначен для программного управления под ключением цепей первого входа с каналом второго выхода и отключением ; таких цепей от первого выхода. Это необходимо для того, чтобы исключить перегрузку блока 13 информацией, предусмотренной на текущее время программной работы контролируемого объекта, так как на выход 162 подается только аварийная информация - не предусмотренная программой.

В исходном состоянии сигналы, поступающие на вход 221 коммутатора, проходят через открытые элементы 66 И на выход 162, а также поступают на входы закрытых элементов 67 И.

Сигналы, поступающие на входы 164 и 165-1 коммутатора, открывают элемент 72 И и частично подготавливают канальный регистр 68-1. В этом случае сигналы, поступающие на вход 148, проходят на выход элемента 72 И.

Допустим, что сигнал проходит на вход регистра 69 и на его выходе 191-1 формируется сигнал, поступающий на соответствующий управляющий вход элемента 66 И. При этом закрывается соответствукхцая пара ключевых элементов и цепи 160-1-1 и 160-2-1 отключаются от выхода 162.

Сигнал с выхода 148-1 элемента 72 И поступает также на соответствующие входы канальных регистров 68-1, 68-т, но запоминается этот сигнал в элементе 1 памяти регистра 68-1, так как на его второй вход 165-1 также поступает сигнал. При этом на выходе элемента 1 памяти регистра 68-1 формируется сигнал, поступающий на управляющий вход двух ключевых элементов 1 канального элемента 67-1 И, которые открываются и соединяют цепи 160-1-1 и 160-2-1 через элемент 70-1 ИЛИ с первым каналом выхода 163.

Кроме того, сигнал с выхода элемента 1 регистра 68-1 через формирователь 71-1 поступает на выход 166-1, сигнализируя, что первый измерительный канал выбран. Остальные (т-1) каналы выбираются аналогично.

Функциональные связи измерителя 9 точного времени приведены на фиг. 7.

Период первого тактового сигнала СТИ равен периоду поступления счетных импульсов на вход блока измерения времени.8 (Лиг. 1), т.е. грубому отсчету времени, и находится в следуюрдей зависимости с периодами второго ТИ и третьего ТИ тактовыми сигналами:

ТИ n ТИл, где , 4, 8 ...

TH,j.TH.

Допустим, что сигнал с выхода узла 92 поступает на вход первого измерительного канала узла 93 и запоютнается в его первом элементе задержки 43-1. Одновременно этот сигнал через (формирователь 94-1 признака сообщения поступает на вход 195 разряда признака сообщения 42. При этом на его выходе 193 Лормируется сигнал, поступающий на первый вход ячейки 41-1 перезаписи. Второй тактовый сигнал ТИ ij через элемент 95 ИЛИ .поступает на второй вход 194 ячейки 41-1, на выходе которой при этом формируется сигнал перезаписи, который поступает на считывающие входы первых элементов задержки всех измерительных каналов. Поэтому е выходов разрядов (элементов задержки) 42,43-1 ... 43-т код 110 ...О через разрешенную схему запрета 96 переписывается в соответствующие разряды 42 и 43-1 второй ступени задержки, при этом на выходе разряда 42 этой ступени задержки формируется сигнал, поступашадй на первый вход ячейки 41-2. Так осуществляется продвижение информации в линии задержки первого канала измерения.

Сигнад с выхода 195 йормирователя 94-1 поступает также на входы элементов 98 И, которые открываются, и сигнал - признак полярности сигнала, поступающий на входы 163-2 или 1RO-2 узла 92 через его выход 197 и элемент 98-1 И, подается на вход буЛера 99, где запоминается в соответствующем разряде. Отсчет грубого времени при этом поступает на вход 161 и через элемент 98-2 И такж подается и запоминается в буфере 99.

Допустим, что с выходом узла 92 следующие сигналы поступают на входы 2 и m второго и т-го измерительных каналов узла 93. Эти сигналы запоминаются в первых элементах задержки (разрядах) 43-2 и 43-т соответствующих измерительных каналов, а также поступают на входы формирователя 94-1, на выходе 195 которого формируется сигнал, поступакядий на вход разряда42, на. выходе 193 которого Лормируется сигнал, поступающий на первый вход ячейки 41-1. При поступлении на ее вход 194 сигнала ТИ,, на ее выходе Формируется сигнал перезаписи, который код 101 ... 1 переписывает через схему 96 на входы аналогичных разрядов 42, 43-2 и 43-т второй ступени задержки.

Одновременно сигнал с выхода 195 формирователя 94-1 поступает на вход элементов 98 И, при этом признаки полярности сигналов с выхода 197 через элемент 98-1 И поступают на вход буЛера 99 и запоминаются в его соответствующих разрядах. На второй вход

буфера 99 через элемент 9Й-2 И поступает отсчет грубого времени, но , этот отсчет идентичен тому, который уже имеется в буфере 99, и поэтому изменений в нем не производит.

Затем на вход ТИ узла 92 поступает тактовый сигнал. Этот сигнал с выхода 192 узла 92 поступает на входы узлов кодирования 97 и разрешает их, на входы схем 96 и запрещает их, а также через элементы 95 ИЛИ на входы 194 ячеек 41, и если на их входах 193 имеются сигналы, то на их выходах формируются сигналы перезаписи. Информация с выходов разрядов 43-1 ... 43 m поступает на

5 входы закрытых схем 96, а также на входы узлов 97, так как эти узлы разрешены, то код, соответствующий положению сигнала в линии задержки, , с выходов узлов 97 поступает в 6yii)ep 99, как отсчет точного времени. Кроме

0 того, сигналы с выходов узлов 97 поступают на входы формирователей . 94-2, 94-3, ... 94- (т+1), на .выходах которых формируются признаки номеров измерительных каналов, в которых

5 имеется информация для ее последующей идентификации. Эти признаки поступают на управлякчцие входы буЛера 99 и запоминаются в нем. На входы каналов измерения узла 93 поступают

0 новые сигналы и продолжается их измерение.

Третий тактовый сигнал ТИ посту- . пает- на вход 91 передающего буЛера 99 и перемещает полученный.кадр ин5формации, который содержит: грубый и точные отсчеты времени для каждого канала, признаки номеров каналов, в которых получены отсчеты, а также признаки полярности сигналов в каналах - к выходу буфера 99. При этом

0 на его выход 174 поступает сигнал запроса на передачу инАормадии, в ответ на которой на вход 175 поступает сигнал, разрешения, по которому на выход 171 подаются сообщения те5кущего кадра.

Такое решение обеспечивает параллельную работу нескольких измерительных каналов на линиях задержки и обладает схемной простотой и высокой

0 точностью измерений.

Каждый из узлов 103-1, 103-2,... 103-т(фиг. 8) преобразует во временной интервал один из параметров сигнала, например амплитуду импульса,

5 его длительность, период следования, количество импульсов в пачке и др, Узел 103-0 презназначён для определе ния полярности сигнала и формирования соответствующего признака.

Управлякщие входы первой 183 и вто0рой 182-1, с также вход 153 блока 10 являются аналогичными входами ключевых схем 102, выходы которых через соответствующие узлы 103 преобразования параметров соединены с первым

5 входом 180 измерителя 9 точного времени, а управляющие выходы 181 чевых схем 102 соединены с третьим управляющим входом измерителя 9, который соединен с управляющими вх дами ключевых схем 101, первый 180 второй 163-1 и третий 163-2 входы которых являются первым и вторым вх дами измерителя 9, первый 185 и вто рой 182-2 управляющие входы, и первы синхронизирукщий вход ТИ которого являются аналогичными входами ключе вой схемы 100, а его сигнальные выходы 184 - аналогичными выходами кл чевых схем 100 и 101, при этом вых 198 ключевой схемы 100 и первые вы ходы 1, 2 ... m ключевых схем 101 соединены с входами узла измерений 93, а вторые выходы 199 - с входом 197 элемента 98-1 И (фиг. 7). В исходном состоянии ключевые схемл 102 закрыты и на их выходах 181 сигналов нет. в исходном состоя нии ключевая схема 100 закрыта и н ее выходе 184 сигнала нет. Ключевые схемы 101 в исходном состоянии соед няют свои первый и второй выходы соответственно с выходами 163-1 и 163-2 и на их выходах 184 имеются сигналы. Сигн, поступакн:дай на вход 185 открывает ключевую схему 100 и тактовые сигналы ТИ проходят на ее выход 198, сигнал, поступающий на вход 182-2, возврашает ее в и.сходное состояние и тактовые сигналы ТИ на выход не поступают. Допустим, что на вход 183 блока 10поступает код 100 ... 1, при это ключевые cxeMii 102-0 и 102-т открываются, и сигналы, поступаю1иие на вход 153, проходят через эти ключев схемы на входы узлов 103-0 и 103-т. Одновременно на выходах 181 схем 102-0 и 102-т формируются управляющие сигналы, поступалогтще на входы ключевых схем 101-0 и 101-т, при этом ключевая схема 101-0 соединяет свой выход 199 с входом 180-2, а ключевая схема 101-т соединяет свой выход m с входом 180-1, отключая входы 163-1 и 163-2 и выход 199 Сигналы с выходов 184 ключевых схем 101-0 и 101-т снимаются. В этом слу чае сигналы с выходов узлов 103-0 и 103-т проходят через схемы 101-0 и 101 на выходы 199 и m узла 92. Так как на входы 163 ключевых схем 102-1 и 102-2 поступили символы нулей, то они своего состояния не изменяют, поэтому не изменяют св его состояния и ключевые схемы 101и 101-2 узла 92, и сигналы, поступающие на их входы 163-1 и 163-2, проходят на первый и второй входы узлов 93, а также на выход 199 узла Сигнал, поступающий на вход 182возвращает ключевые схегиы 102-0 и 102-т блока 10 в исходное состояние при этом снимаются сигналы с их выходов 181, что возвращает в исходное состояние ключевые схемы 101-0 и 101-т и на их выходах 184 формируются сигналы, а также отключаются их входы 180-1 и 180-2, и, кроме того, схема 101-т подключает свои входы 163-1 и 163-2 ко входу m узла 93 и к выходу 199 узла 92. Такое решение позволяет использовать один и тот же измеритель 9 точного времени как для детального контроля параметров сигнала в процессе отладки отдельных узлов контролируемого объекта, так и для измерений временных характеристик контролируемого объекта в динамике его работы. Блок адаптивного контроля (1иг. 9) предназначен для непрерывного контроля цепей, которые не выбраны программой для измерений в данный момент времени, определения адресов этих цепей при изменении не предусмотренного программой состояния в них (т.е. проявления активности) и точного измерения времени такого измерения. Первый вход 167 блока соединен с первыми входами ключевых схем 77, вторые входы которых соединены с выходом второго элемента 76-2 ИЛИ, а выходы - с входами регистра 81 и входами соответствующих ячеек 79 формирования признака сообщения, выходы которых соединены с входом регистра 81, а выходы первой 78-1 и второй 79-2 ячеек кроме того - с входами управления ключевых схем 77-1, 77-2, 77-т, а первой ячейки 79-1 также и с входами управления элемента 78 И и элемента 75 И, вход кЬторого является первым синхронизируквдим входом ТИ блока, а его выход соединен с входами сброса ячеек 79 и входами управления регистра 81 и измерителя точного времени 80, первый вход которого соединен с выходом первого элемента 76-1 ИЛИ, второй является вторым синхронизирующим входом ТИг2 блока, цепи второго входа 162 которого соединены с входами первого 76-1 и второго 76-2 элементов ИЛИ соответственно, а его третий вход 161 через элемент 76 И соединен с входом регистра 81, выходы которого, а также выход измерителя 80, соединены с входами передающего буфера 40, выходы которого и вход обратной связи 203 соединены соответственно с входами и вторым управляющим выходом узла 82, выход 168, первый управляющий выход 169 и вход обратной связи 170 которого являются аналогичными выходами и входами блока, третий синхронизируюгпий .вход ТИ которого является управляющими входами буфера 40 и узла 82. При этом период первого синхронизирующего сигнала ТИ равен периоду

поступления счетных импульсов на вход блока 8 (лиг. 1) и находится в следующей зависимости с сигналом TH,j и ТИ 3 :

ТИ . nTHj;

ТИ THj.

Допустим, что сигналы поступают н входы 162-1-1 и 162-2-1, что свидетельствует о нгшичии отрицательного сигнала в контролируемой (первой цепи. Сигнал с выхода элемента 76-1 ИЛИ поступает на вход измерителя во и тактовыми сигналами ТИ,, поступающими на другой его вход, продвигается Между разрядами Сэлементами задержки) в линии задержки ;аналогично описанному выше (Лиг. 1).

Сигнал с выхода элемента 76-2 ИЛ поступает на входы схем 77, но открыта только схема 77-1. Здрес данной цепи (первой) поступает на вход 167 и через открытую ключевую схему 77-1 поступает на соответствующий вход регистра 81, а также на вход ячейки 79-i, на выходе 204 которой формируется сигнал. Этот сигнал поступает на входы ключевых схем 77-1 и 77-2 при этом схема 77-1 закрывается, а схема 77-2 открывается, на входы элемента 78 И и элемента 75 И, которые открываются, а также на вход регистра 81, где запоминается как признак наличия сообщения в соответствующих элементах памяти регистра 81. .

Отсчет грубого времени поступает на вход 161 и проходит через элемент 78 И на вход регистра 81.

Пусть на вход 162-1-15 поступает следуюгпий сигнал; что свидетельствует о наличии положительного сигнала в контролируемой (пятнадцатой) цепи. Этот сигнал через элемент 76поступает на вход измерителя 80 и тактовыми сигналами ТИ .j. продвигается между его элементами задержки с некоторым смешением относительно первого сигнала.

Адрес данного сигнала поступает на вход 167, переходит через открытую схему 77-2 на вход регистра 81 и на вход ячейки 79-2, на выходе которой .Лормируется сигнал, котордяй закрывает ключевую схему и открывает ключевую схему 77-т, а также на вход регистра 81 и в нем запоминается признак второго соойцения.

Первый тактовый сигнал, поступающий на вход ТИ, через элемент 75 И поступает на входы. 79 сброса ячеек, которые возвращаются в исходное положение, при этом закрывается элемен 78 И и ключевая схема 77-, сигнал с управляющего входа элемента 75 И снимается и очередные тактовые сигналы ТИ на его выход не подаются, ключевая схема 77-1 открывается, а схема 77-2 остается в закрытом состоянии.

Сигнаш с выхода элемента 75 И поступает также на входы измерителя 80 и регистра 81. При этом на выход измерителя 80 поступают два кода точного времени для двух сигналов, а на вы-. 5 ход регистра 81 два адреса цепей этих сигналов, грубый отсчет времени, а также на выходы 201-1, 201-2 сигналы признаков первого и второго сообщений, содержеидихся в данном Q кадре (группе сообщений), которые необходимы для идентификации сооб- . щений в кадре, после его сжатия для передачи в канал связи. Кроме того, на выход 201-0 поступает признак передаваемого кадра.

5 Вся эта информация записывается в информационных разрядах 43 первого регистра передающего буфера 40, а признак кадра записывается в разряде 42, на выходе 202 которого формируется сигнал, поступающий на вход ячейки 41, и если на второй ее вход 203 поступает сигнал - признак свот бодного следующего регистра, то при поступлении на ее третий вход тактового сигнала ТИ, на ее выходе Формируется сигнал перезаписи, который переписывает кадр инлормадии в еле- , дущий регистр буфера 40.

С выходов передающего буфера 40 Q сообщения принятого Формата поступают на входы соответствупщих элементов 83 ИЛИ узла 82, с выходов которых сообщения поступают на входы разрядов 43 и 42 соответствующих реC гистров. При этом нэ выходах 202 соответствую(дих разрядов 42 Лорнируются сигналы, которые поступают на первые входы ячеек 41, но так как на их входы 203 сигналы не поступают потому, что следующие регистры с 0 разрядом 43 и 42 заняты, то продвижение сообщений на выходе узла 82 не происходит.

Сигналы с выходов 202 поступают также на входы формирователя 85 и 5 ячейки управления 84, при этом снимается сигнал с ее инверсного выходя 203 и форг руется сигнал на ее прямом выходе 169, который поступает на выход блока, как сигнал запроса 0 на передачу информации. В ответ на который на вход 170 поступают сигналы разрешения, которые подаются на второй вход ячейки 41-1. Поэтому при (поступлении тактового сигнала ТИ на е ее третий вход, на ее выходе фop в pyется сигнал перезаписи, который rie реписывает сообщение из первого регистра (разряды 43-1 и 42-1) на выход 1€8. При этом в разряде 42-1 снимается сигнал с выхода 202 и формируется на выходе 203, с которого подается на второй вход ячейки 41 пред.шествукедего регистра. Поэтому в первый регистр поступает с выхода npej;.вюствукйцего через элемент 83 ИЛИ второе сообщение, которое аналогично

описанному поступает на выход 168 блока.

После того, когда остается последнеее сообщение данного кадра в первом регистре (разряды и 42-1 , на входы формирователя 85 с выходов 202 разрядов 42 сигналы не поступают, в этот момент с инвертированного выхода 203 ячейки 84 также еще не поступает-сигнал, поэтому на ее выходе Лормируется сигнал - признак окончания кадра, который поступает на вход соответствующего разряда 43-1. первого регистра. Поэтому последнее сообщение содержит призйаки окончани кадра. После передачи последнего сообщения сигналы на вход ячейки 84 не поступают, при этом снимается сигнал с выхода 169 и Формируется сигнал на ее инверсном выходе 203.

Блок управления выдачей информации (Фиг, 10) предназначен для оперативного перераспределения канала вычислительной мешины между потокгиии информации, накопленной в передающих буферах блоков 13 и 16 и измерителя 9 , с заданным приоритетом. При этом приоритет должен разрешаться только после передачи всех сообщений текущего кадра, так как в кадре объединяется группа сообщений, имеюадах общие признаки адресной и временной привязки.

Входы первый 169, второй 174 и третий 176 через элементы запрета

87и ключи. 90 соединены с управлятими выхода1Уи первым 170, вторым 175 и третьим 177 блока соответственно, а также через, формирователь 86 запросного сигнала - с его выходом 178, вход обратной связи 179 блока соединен со вторими входагли ключей 90, выходы которых, кроме того, соединены с переыми входами соответствующих узлов 89 неизменности состояния и элементов 88 ИЛИ. йлходы элементов

88ИЛИ соединены с вторыми входами узлов 89, третьи входы которых соединены со вторым 174-2 и третьим 176-2 входами блока соответственно, кроме того, первый 169 и второй 174-1 входы блока соединены с входами элементов ИЛИ 88-2 и 88-3, а выход первого элемента 88-1 ИЛИ соединен с выходом запрета первого элемента запрета 87-1, входы запрета других элементов запрета 87-2 и 87-3 соединены с выходами соответствующих узлов 89.

Допустим, что на вход 176-1 поступает сигнал, который через разрешенный элемент запрета 87-3 поступает на вход ключа 90-3, а также через формирователь 86 на выход 178, как запрос на разрешение-передачи информации, в ответ на который поступает сигнал на входы 179 ключей 90, при .этом на выходе 177 ключа 90-3 Лормируется сигнал, поступающий на выход блока, а также на выходы элементов

88-1 ИЛИ И 88-2. При этом запрещаются элементы запрета 87-1 и 87-2. Кроме того, сигнал с выхода 177 ключа 90-3 поступает также на вход узла 89-2, который запрещает изменять состояние элемента запрета 87-3 до окончания передачи сообщений текущего кадра.

Допустим, что на вход 169 также поступает сигнал, поступает на вход запрещенного элемента 87-1 и через элементы 88-2 и 88-3 ИЛИ на входы узлов 89-1 и 89-2, но изменений в них не производит, так как на втором входе узла 89-1 уже имеется сигнал с выхода 177 ключа, 90-3, которым запрещен элемент 87-2, узел 89-2 также не может изменять своего состояния и состояния элемента 87-3, .так как имеется сигнал на его первом входе, поступающий с выхода 177 ключа 90-3.

Поэтому продолжается передача информации по выбранному канашу до поступления на вход 176-2 сигнала окончания данного кадра, который поступает на третий вход узла 89-2, разрешая изменять состояние элемента 87-3 запрета. Поэтому сигнал с выход элемента 88-3 ИЛИ через узел 89-2 поступает на вход запрета элемента 87-3 и запрещает его,сигнал с его выхода и выхода 177 ключа 90-3 снимается, элемент 87-1 запрета разрешается и на его выход поступает сигнгш при этом сигнал управления формируется на выходе 170 ключа 90-1 и управление передачей информации передается другому каналу.

После окончания передачи информации по всем каналам, сигналы снимаются с входов 169, 174 и 176, что приводит к снятию запроса с выхода 178 блока, а это приводит к снятию сигнала с его входа 179 и с управляющих выходов 170, 175 и 177. Канал вычислительной машины отключается от устройства.

функциональные связи блока 16 управления приведены на фиг. 11.

Командной вход 186 -блока является входом узла .коммутации 104, первый 205, второй 206 и третий 207 выходы которого, а также его входы управления соединены с входами и управляющими выходами 208-210 дешифратора 106 команд, регистра 107 операций и накопителя 108 соответственно, первый выход 211 дешифратора 106 соединен с входом передакнцего буфера 110 и первым входом дешифратора 112 операций, второй вход 214 которого через узел приоритетов 113 соединен с выходом 213 регистра 107, который соединен также с входом буфера 110 через элемент 111 И, при этом выходы 143, 144, 156, 158, 164, 185 и 187 дешифратора 112 являются соответствено четвертым., седьмым, пятым, шестым третим, вторым и первым выходами следования операций блока, второй вы ход 212 соединен с управляющим входо регистра операций 107 и первым входом первого элемента 105-1 ИЛИ, второй вход которого соединен с вторым выходом 206 узла 104, а выход соединен с вторым входом элемента 111 И, третий выход 223 соединен с входом буЛера 110, вюрым входом накопителя 108 и первым входом узла 116, четвер тый выход 228 соединен с первым управляющим входом ключевого элемента 109, а также с управляющим входом узла 115, другие управляющие входы которого соединены с соответствующими выходами 156, 164, 187 следоваНИН операций дешиЛратора 112 one раций, а также с первым управляющим входом 164 узла 117 управления комму татором и вторым управляющим входом ключевого элемента 109, вход которого соединен с выходом накопителя 108, а ее выходы 183 и 188 являются измерительным и выходом управления стимулирующими воздействиями блока, третий 216 соединен с буфером 110 ,четв тый - с вторым входом 215 узла 116 контроля выполнения операций, третий вход которого соединен с пятым выходом 224 дешифратора 112 операций, четвертый 155 является входом контроля операций блока, пятый 227 соединен с первым выходом узла 115, шестой и седьмой входы соединены с вторым 221 и третьим 222 выходами узла 117, а его выходы первый 217 и второй 149 соединены с входами передающего 110, а второй 149 кроме того, является выходом признака окончания операции блока и соединен с управляющими входами дешифратора 112 узла 115, а также с входом (Формирователя 114 признака окончания команды, второй вход 225 которого соединен с вторым выходом узла 113 приоритетов, третий 229 с третьим выходом дешифратора 106 команд, а выход соединен с входом буфера 110 и входами сброса регистра 107 операций и накопителя чисел 108, при этом второй выход 182 дешифратора 106 является выходом командного сброса блока, сигнальные входы 157, 159, 166, 181 и 184 которого являются аналогичными входами узла 115 контроля программных соединений, второй вход 218 которого соединен с входом булера 110, третий 219 с первым входом узла 117 управления коммутатором, а его вход 148 является коммутируквдим входом блока, который через второй элемент 105-2 ИЛИ соединен с вторым входом 220 узла 11 .управления коммутатором, первый выход которого является выходом 165 управления коммутатором, третий вход 154 которого является входом .передающего буфера 110 и является адресным входом блока. Командная информация, определяющая назначение и порядок выполнения операций, поступает на вход 186 узла 104 коммутации и первое слово этой информации проходит на вход 205 дешифратора 106 команд. При этом на выходе 208 формируется управляющий сигнал в том случае, если командная, информация состоит из нескольких слов, при этом в соответствующем разряде первого слова содержится соответствуквдий признак, например символ I в нулевом разряде. По этому сигналу второе слово поступает на выход 206 узла 104 и на вход регистра one раций 107, если при этом на выходе 209 формируется сигнал, то следующие слова подаются на вход 207 накопителя 108, в котором накапливаются числа (слова). Последнее слово командной информации признака продолисения командаа не содержит, (содержит признак окончания команды) , поэтому снимается сигнал с выхода 210 накопителя 108 и узел 104 возвращается в исходное состояние,при котором его вход 186 соединяется с выходом 205. Дешифратор 106 дешифрует первое слово командной информации и Формирует на выходе 211 управляющую команду (сигналы на соответствующих шинах выхода 211) , которая поступает навход буфера 110 и на первый вход дешифратора 112 операций. Слово, поступающее на вход регист ра 107, поступает также на вход первого элемента 105-1 ИЛИ, на выходе которого формируется сигнал, поступающий на вход элемента 111 И, который открывается. Поэтому код операций, подлежащих выполнению в данной команде, поступает на вход буЛера 110 через элемент 11 И и на вход узла приоритетов-113 с выхода 213 регистра 107. При этом на вход 214 дешифратора 112 поступает сигнал (бит единицы) старшего разряда этого кода. Дешифратор 112 операций по сигналам, поступакадим на его первый 211 и второй 214 входы, определяет по-рядок выполнения операций и Формирует соответствующие сигналы. Сигналы с выходов 185, 158, 143, 144, .156, 187 и 164 поступают на выход блока, на управляющие входы 156, 164, 187 и 228 узла 115, на входа 187 и 228 ключевого элемента 109, на вход 224 узла 116, на вход 164. узла 117, а признак начала любой из выполняемых операций поступает на выход 223, с которого поступает на входы буфера 110 и узла 116, а также на второй вход накопителя 108, который подает первое число на вход ключевого элемента 109. Это число поступает на вход 216 буЛера 110 и вход 215 узла 116 контроля выполнения опергщий, В том случае, когда на входах 228 или 187 ключевого элемента 109 имеются.сигналы, на выход 215 поступает только признак опергщий, число равное единице, а действительные зна чения чисел поступают на выходы 183 и 188 блока соответственно, а также на выход 216 ключевого элемента 109 Сигнал с выхода 164 дешифратора 112 поступает на вход узла 117, разрешая управление коммутатором, а так же на вход узла 115,контроля-програм мных соединений, на выход 218 которого поступает код, определякчпий состояние ( номера выбранных и свобод ных) измерительных каналов;- кроме того этот код поступает и на выход 219,, с которого подается на вход узла 117, как маска, для распределения оставшихся свободными измерительных каналов между цепями через коммутатор 7 (фиг. 1, 6, 7 и 8). Сигналы,, поступающие на вход 148 блока, через узел 115 поступают на вход 227 узла 116, а также через второй элемент 105-2 ИЛИ на вход 220 узла 117 управления коммутатором 7 (.Лиг. 1) . При этом на его выходах 165, 221 и 222 Аормируются соответствующие сигналы. Работа узла 117 и его Функциональные связи приведены на фиг. 13. . Узел 116 контроля выполнения операций анализирует сигналы, поступающие на его входы, и при выполнении операции или нарушении временного интервала между тактами операций, на его выходе 217 Нормируется признак выполнения операции (код-число тактов, выполненных в данной операции) , поступа Чг1Щй на вход буЛера 110, а На выходе 149 признак окончания операции, который поступает на выход 149 блока, на управлякмций вход узла 115 контроля программных соединений. При этом на выходы 218 и 227 передается состояние необходимых соединений, которые иьюются на сигнальных входах 159, 157, 166, 181, 184 узла 115, которые сигнализируют о выполнении заданных программой соединениях. Кроме того, сигнал с выхода 149 узла 116 поступает на вход формирователя 114 признака окончания команды, и если при этом на ее втором входе 225 имеется сигнал последней выполненной операции, то на выходе 2 ячейки 114 формируется сигнал, который поступает на вход буфера 110, ка признак окончания команды, а также на входы сброса регистра 107 и нако питель 108, которые обнуляются. Сигнал на выходе 226 ячейки 114 формиру ется так же, если на ее вход 229 пос тупает команда сброса с выхода деши ратора 106. На выходе 182 дешиЛрато- ра 106 формируются команды сброса выполняемых команд, которые поступают на выход .блока. сигнал с выхода 149 узла 116 поступает на вход передающего буЛера 110, как признак окончания текущего ка,цра. При этом на выходе 176 Лормируется сигнал запроса на передачу кадра информации, в ответ- поступает сигнал разрешения на входе 177 и на выход 172 подаются сообщения текущего кадра. Сигнал с выхода 149 узла 116 поступает на управляющий вход дешифратора 112 операций, при этом на его выходе 212 формируется сигнал, который через элемент 105-1 ИЛИ открывает элемент 111 и, а также поступает ;ia вход регистра 107 и сбрасывает (обнуляет} старший разряд (разряд операции, которая выполнялась , и на вход 213 узла приоритета 113 поступает код операция которые еще необходимо выполнить. Этот же код через элемент 111 И поступает на вход буфера 110. На выход узла приоритетов 113 поступает сигнал с выхода старшего из оставшихся в коде операций разряда, который поступает на вход 214 дешифратора 112, который с учетом команды, поступающей на вход 211, формирует управляющий сигнал следующей операции. На вход 154 подаются адреса цепей и шин при проверке соединений собственных шин и внешних цепей, которые также составляют отдельные сообщения текущего кадра. Управляющая команда содержит одну или несколько операций, число их определяется кодом, который хранится в регистре 107. Каждая операция содержит один или несколько тактов,число их определяется кодами, которые хранятся в накопителе 108 чисел. Кадр информации, который формируется в буфере 110, содержит коды команды (вход 211), операции вход 213 ), чисел (вход 216), результата выполнения операции (вход 217), признаки начала операций (вход 223) и ее окончания (вход 149), а также окончания команды (вход 226) и служебные признаки , необходимые для идентификации сообщений, автоматического продвижения сообщений в. буфере 110 и сжатия кадров, т.е. исключения пустых сообщений, которые формируются в передающем буфере 110, аналогично описанному выше Сфиг. 7 и 9) . Пример 1. Проверка соединений собственных шин. Эта команда содержит три операции: подача питания необходимого номинала на вход 150 блока 4 (фиг, 1) ,соединение собственных шин в блоке 4

и проведение опроса собственных шин в блоке 4 (Лиг, 4) .

Задача р« шается следующим образом.

На вход 211-х (фиг. 11 и 12) поступает соответствующая команда, которая поступает на первые входы элементов 119-1, 119-2 и 119-3, а также на вход формирователя 121, на выходе 224-1 которого формируется признак команды, поетупаксций на вход элемента 127 И, который открывается. Поэтому тактовые СИГНЕШЫ ТИ поступают на сигнальный вход счетчика 128 контроля времени. Если счетчик 128 отсчитывает число тактовых сигналов больше Зсщанного интервала времени, то на его выходе Формируется сигнал, поступающий на вход формирователя 129 признака окончания операции.

Первая операция в команде - подача питания - представлена символом единицы в первом разряде кода операций. Поэтому на вход 214-1 поступает сигнал, который запоминается в элементе 118-1 задержки и поступает на вторые входы 1р элементов 119-1 и 119-4 И, при этом на выходе элемента 119-1 И «Нормируется сигнал, поступающий на входы Лормирователей 122 и 123 и на вход элемента 120-7 ИЛИ. При этом сигнал с выхода 187 элемента 120-7 ИЛИ поступает на первые входы элементов И групп 125-6 и 125-7, а также на выход блока 16 и на вход блока 17 (фиг. 1),- и на вход ключевой схемы 109 (Лиг. 11) . Сигнал с выхода Формирователя 122 поступает на выход 223 и запоминается в буфере 110 (фиг. 11) , как признак начала выполнения операции, на вход узла 116 и через его формирователь 130 (фиг. 12) на вход сброса счетчика 128, который сбрасывается и начинает счет сначала, а также на вход накопителя 108 (фиг.11 на выход которого подается число. Это число через ключевую схему 109 поступает на вход 216 буфера 110, на олход 188 блока 16, а на вход 215 узла 116 поступает код единицы, который проходит через формирователь 132 на вход счетчика 133 как уставка.

При этом на вход 159 элемента 125-7 И поступает сигнал (Фиг. 1 и 12) , что блок 17 принял и выполняет команду, в результате которой на вход 150 блока 4 поступает сиг- . нал, соответствующий числу, поступавшему на вход 188 блока 17, а на вхо 157-1 элемента 125-6 И (фиг. 12) поступает признак наличия сигналов на входе 150 блока 4 {фиг. 4.

Сигнал с выхода формирователя 123 через элемент 131 ИЛИ поступает на счетньй вход счетчика 133 тактов опе рации, суммируетсд с уставкой, что приводит к его переполйению,и на ег

выходе формируется сигнал, который поступает на вход формирователя 129. На этом первая операция заканчивается, и на выходе 149 формирователя 129 формируется сигнал, который поступает на вход считывания счетчика 133, на выход 217 которого подается код-остаток (в данном случае такой остаток нулевой) , который запоминается в буфере 110 (фиг. 11 .

Кроме того, сигнал .с выхода 149

О узла 116 поступает на входы групп 125, при этом сигналы с выходов элементов 125-6 и 125-7 И через элемент 124-2 ИЛИ поступают на выход 218 узла 115 и запоминаются в буфере 110 (фиг. ПК

Сигнал с выхода узла 116 поступает на вход 149 дешифратора 112, на входы элементов задержки 118, при этом на выход 212-1 (фиг. 11 и 12)

0 поступает сигнал с выхода элемента 118-1, который поступает на вход регистра 107 и сбрасывает первый (старший) разряд. Поэтому сигнал второго разряда - код второй операции - поступает на вход 214-2, запоминается в

5 элементе 118-2 и поступает на входы 2р элементов 119-2 и 119-5, при этом на выходе.элемента 119-2 И формируется сигнал, который поступает на входы элементов 120-1 и 120-2 ИЛИ

0 и формирователь 122, на выход 223 которого поступает сигнал второй операции. Кроме того, этот сигнал через формирователь130 сбрасывает счетчик 128, а также по это5му сигналу на вход 215 узла 116 поступает код - уставка, которая через формирователь 132 записывается в счетчике 133.

Сигналы с выходов 156-2 и 156-5 элементов 120-1 и 120-2 ИЛИ подают0ся на вход блока 4 (фиг. 1 и 4) , . с выхода 156-2 также и на входы схемл 125-1. Так уак решается задача проверки соединений собственных шин, то выбирается первая собственная

5 шина и сигнал формируется на выходе 148-1 блока 3 (фиг. 1), который поступает на вход блока 4 (Фиг. 4 и на вход элемента 125-1, на вход 157-4-1 которого также поступает

0 сигнал доклада о выполнении соответствующего соединения в блоке 4 (фиг. 4) . Поэтому на его выходе формируется сигнал, который через элемент 124-1 ИЛИ поступает на вход

5 227 уэла 116 и подается на вход элемента 131 ИЛИ и с его выхода через Формирователь 130 на вход.сброса счетчика 128, а также на вход счетчика 133, где суммируется с уставкой и на его выходе формируется сиг0нал, поступающий на вход формирователя 129, на выход 149 которого, подается признак окончания операции. Этот признак поступает на вход 149 счетчика 133 и на его клход 217 подается

остаток - признак количества тактов, выполненных в данной операции, и на входы элементов 118 дешифратора 112, на выходе 212-2 элемента 118-2 формируется сигнал. Поэтому сигнал подается на следующий вход 21.4 (214-3) который запоминается в соответствующем элементе 118 задержки и подается на входы Зр элементов 119-3 и 119-6 при этом сигнал Формируется на выходе элемента 119-3, с которого чере формирователь 122 поступает на выход 223, счетчик 128 при этом сбрасывается, а на вход 215 поступает число, которое через Лормирователь 132 поступает на вход счетчика 133, как уставка, а также с выхода элемента 119-3 И через элементы 120-2 и 120-3 ИЛИ сигналы поступают на выходы 156-5 и 158-1. По этим сигналам блока 4 (фиг. 4) проверяют соединения собственных шин, о резуль татах такой проверки сообщают сигналы, поступающие на вход 155-2 элемента 131 ИЛИ, и через формирователь 130 сбрасывающие счетчик 128, а также поступают сигналы на счетный вход счетчика 133, где суммируются с сигналами уставки.

После проверки собственных шин счетчик 113 переполняется и на его выходе формируется сигнал, поступающий на вход (Формирователя 129, на выходе 149 которого формируется . сигнал - признак окончания операции. При этом на выход 217 счетчика 133 поступает код - остаток, а на выход 212 соответствующего элемента задерж ки 118 - сигнал для сброса текущей операции.

После выполнения всех операций текущей команды снимается сигнал с выхода 211-х дешифратора 112 и элемент 127 И закрывается.