1

Изобретение относится к импульсной технике и используется в систе-. мах обработки информации.

Известен параллельный аналого-цифровой преобразователь, содержащий группу компараторов старших разрядов и группу компараторов младших разрядов, первые входы которых подключены к источникам опорных напряжений, сигнальные входы группы компараторов старших разрядов подключены к источнику преобразуемого сигнала, а выходы компараторов в кгикдой группе, кроме компараторов старших разрядов, объединены попарно и подключены к управляющим ;входам элементов памяти, и резистивные усилители, первые входы которых подключены к источникам токов смещения, вторые через повторитель и инвертор подключены к источнику преобразуемого сигна.г1а, а выходы попарно со сдвигом на один подключены ко входам элемента И, выходы которых через элемент ИЛИ соединены с сигнальными входами компаратрров млс1дших разрядов, входы стробирования элементов памяти подключены к выходу источника стробируюjuero сигнала { . Недостатками данного преобразователя является низкая точность и Нсщежность преобразования.

Цель изобретения-повыиение надежности и точности преобразования.

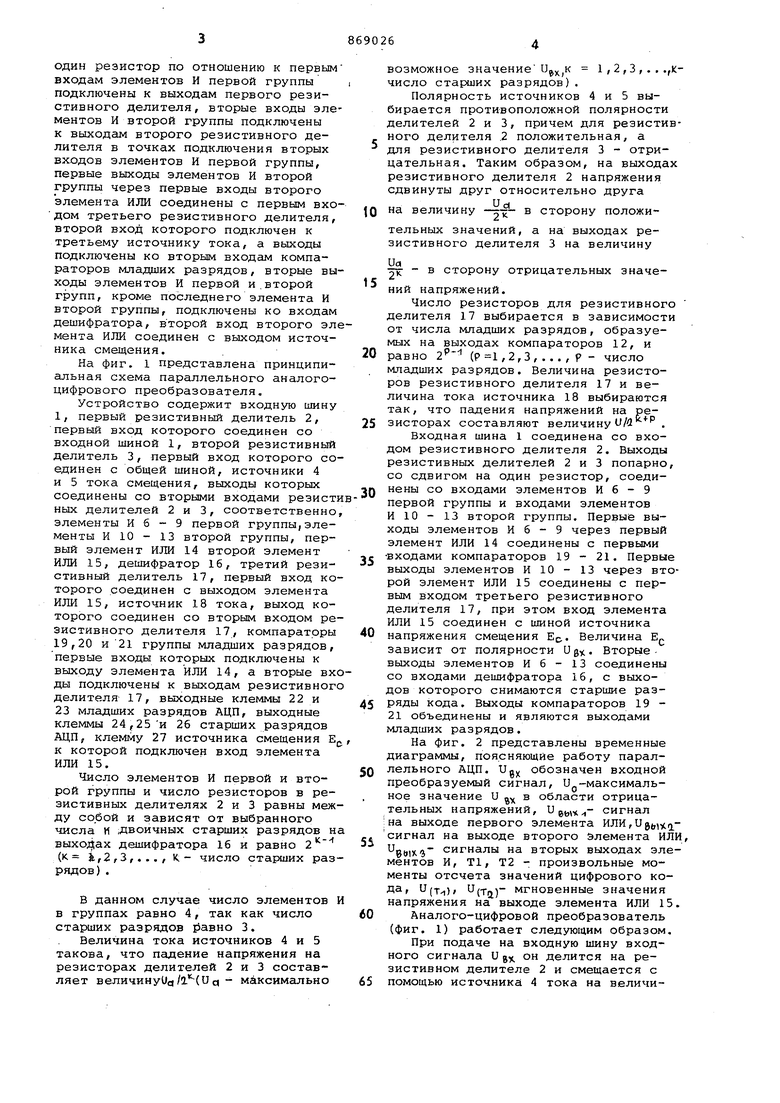

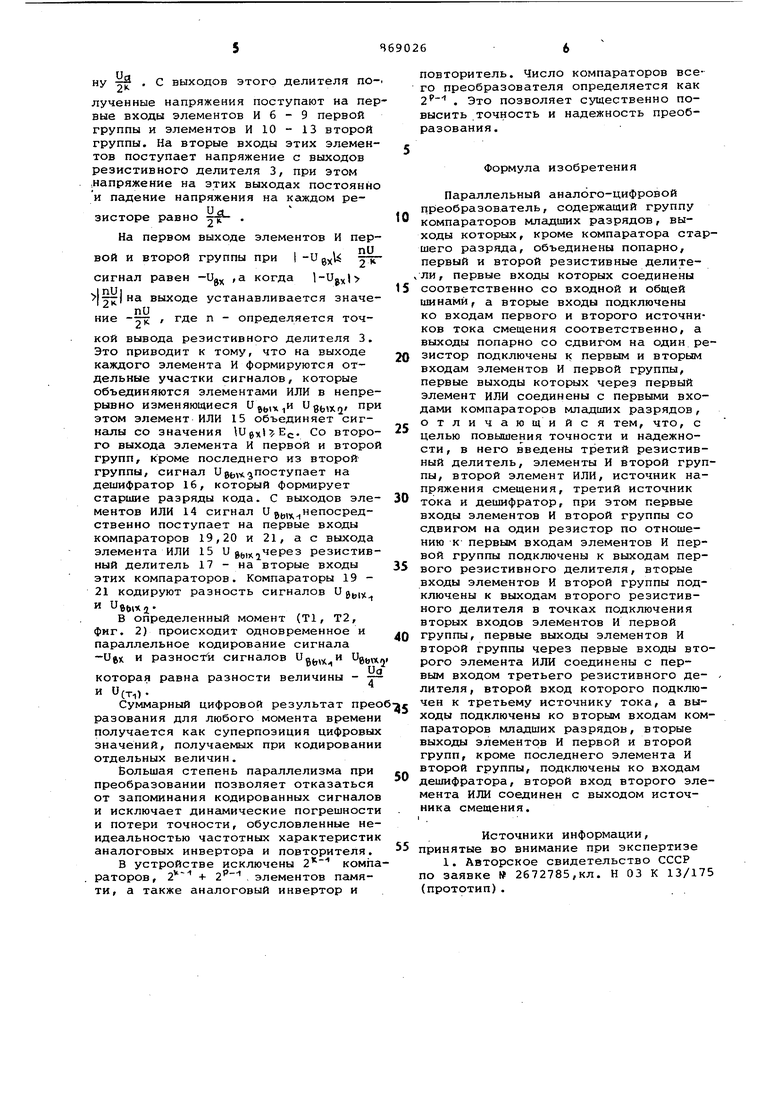

Поставленная цель достигается тем, что в параллельный аналого-цифровой преобразователь, содержащий группу компараторов младших разрядов, выходы которых, кроме компаратора старшего разряда, объединены попарно, первый и второй резистивные делители , первые входы которых соединены соответственно со входной и общей шинами, а вторые входы подключены ко входам первого и второго источников тока смещения соответственно, а выходы попарно со сдвигом на одии резистор подключены к первым и вто1«м входам элементов И первой группы, первые выходы которых через первый элемент ИЛИ соединены с первыми входами компараторов младших разрядов, дополнительно введены третий резистивиый делитель, элементы И второй группы, второй элемент ИЛИ, источник напряжения смещения, дешифратор и третий источник тока, при этом первые входы элементов И второй группы со сдвигом на один резистор по отношению к первым входам элементов И первой группы подключены к выходам первого резистивного делителя, вторые входы эле ментов И второй группы подключены к выходам второго резистивного делителя в точках подключения вторых входов элементов И первой группы, первые выходы элементов И второй группы через первые входы второго элемента ИЛИ соединены с первым вхо дом третьего резистивного делителя второй вход которого подключен к третьему источнику тока, а выходы подключены ко вторым входам компараторов младших разрядов, вторые вы ходы элементов И первой и.второй групп, кроме последнего элемента И второй группы, подключены ко входам дешифратора, второй вход второго эл мента ИЛИ соединен с выходом источника смещения. На фиг. 1 представлена принципиальная схема параллельного аналогоцифрового преобразователя. Устройство содержит входную шину 1, первый резистивный делитель 2, первый вход которого соединен со входной шиной 1, второй резистивный делитель 3, первый вход которого со единен с общей шиной, источники 4 и 5 тока смещения, выходы которых соединены со вторыми входами резист ных делителей 2 и 3, соответственно элементы И 6 - 9 первой группы,элементы И 10 - 13 второй группы, первый элемент ИЛИ 14 второй элемент ИЛИ 15, дешифратор 16, третий резистивный делитель 17, первый вход ко торого соединен с выходом элемента ИЛИ 15, источник 18 тока, выход ко торого соединен со вторым входом р эистивного делителя 17, компараторы 19,20 и 21 группы младших разрядов первые входы которых подключены к выходу элемента ИЛИ 14, а вторые вх ды подключены к выходам резистивно делителя 17, выходные клеммы 22 и 23 младших разрядов АЦП, выходные клеммы 24,25и 26 старших разрядов АЦП, клемму 27 источника смещения к которой подключен вход элемента ИЛИ 15. Число элементов И первой и второй группы и число резисторов в ре зистивных делителях 2 и 3 равны меж ду собой и зависят от выбранного числа Н двоичных старших разрядов выходах дешифратора 16 и равно 2 (к i,2,3,..., К- число старших ра рядов) . В данном случае число элементов в группах равно 4, так как число старших разрядов равно 3. Величина тока источников 4 и 5 такова, что падение напряжения на резисторах делителей 2 и 3 составляет величинуис|/1(иа - максимально возможное значениеUj,к 1,2,3,...,Кчисло старших разрядов). Полярность источников 4 и 5 выбирается противоположной полярности делителей 2 и 3, причем для резистивного делителя .2 положительная, а для резистивного делителя 3 - отрицательная. Таким образом, на выходах резистивного делителя 2 напряжения сдвинуты друг относительно друга на величину в сторону положительных значений, а на выходах резистивного делителя 3 на величину - в сторону отрицательных значений напряжений. Число резисторов для резистивного делителя 17 выбирается в зависимости от числа младших разрядов, образуемых на выходах компараторов 12, и равно 2 (р 1, 2,3 , ... , р - число младших разрядов. Величина резисторов резистивного делителя 17 и величина тока источника 18 выбираются так, что падения напряжений на резисторах составляют величину . Входная шина 1 соединена со входом резистивного делителя 2. Выходы резистивных делителей 2 и 3 попарно, со сдвигом на один резистор, соединены со входами элементов И 6 - 9 первой группы и входами элементов И 10 - 13 второй группы. Первые выходы элементов И 6 - 9 через первый элемент ИЛИ 14 соединены с первыми -входами компараторов 19 - 21. Первые выходы элементов И 10 - 13 через второй элемент ИЛИ 15 соединены с первым входом третьего резистивного делителя 17, при этом вход элемента ИЛИ 15 соединен с шиной источника напряжения смещения ЕС,. Величина Е, зависит от полярности Ug-.. Вторыевыходы элементов И 6 - 13 соединены со входами дешифратора 16, с выходов которого снимаются старшие разряды кода. Выходы компараторов 19 21 объединены и являются выходами младших разрядов. На фиг. 2 представлены временные диаграммы, поясняющие работу параллельного АЦП. Ug обозначен входной преобразуемый сигнал, и -максимальное значение U в области отрицательных напряжений, Ugj,,- сигнал ; на выходе первого элемента ИЛИ,и5ь1иа сигнал на выходе второго Элемента ИЛИ, Btiixj сигналы на вторых выходах элементов И, Т1, Т2 - произвольные моменты отсчета значений цифрового кода, U(T-i)j (Тп мгновенные значения напряжения на выходе элемента ИЛИ 15. Аналого-цифровой преобразователь (фиг. 1) работает следующим образом. При подаче на входную шину входного сигнала U jx, он делится на резистивном делителе 2 и смещается с помощью источника 4 тока на величиС выходов этого делителя полученные напряжения поступают на пер вые входы элементов И б - 9 первой группы и элементов И 10 - 13 второй группы. На вторые входы этих элементов поступает напряжение с выходов резистивного делителя 3, при этом ..напряжение на этих выходах постоянно и падение напряжения на каждом резисторе равно 2 . На первом выходе элементов И первой и второй группы при сигнал равен -U ,а когда чТк выходе устанавливается значение --r-jj , где п - определяется точкой вывода реэистивного делителя 3. Это приводит к тому, что на выходе каждого элемента И формируются отдельные участки сигналов, которые объединяются элементами ИЛИ в непрерывно изменяющиеся и, Ug(,(xn/ при этом элемент ИЛИ 15 объединяет сигналы со значения Ugxl E, Со второго выхода элемента И первой и второй групп, кроме последнего из второй группы, сигнал ир(,,,(.5поступает на дешифратор 16, который формирует старшие разряды кода. С выходов элементов ИЛИ 14 сигнал и р(„ непосредственно поступает на первые входы компараторов 19,20 и 21, а с выхода элемента ИЛИ 15 U ,через резистивный делитель 17 - на вторые входы этих компараторов. Компараторы 19 21 кодируют разность сигналов U gj,,y и . В определенный момент (Т1, Т2, фиг. 2) происходит одновременное и параллельное кодирование сигнала -UjK и разност сигналов Ug и Ug,x которая равна разности величины - -г- и U(T,): Суммарный цифровой результат прео разования для любого момента времени получается как суперпозиция цифровых значений, получаемых при кодировании отдельных величин. Большая степень параллелизма при преобразовании позволяет отказаться от запоминания кодированных сигналов и исключает динамические погрешности и потери точности, обусловленные неидеальностью частотных характеристик аналоговых инвертора и повторителя. в устройстве исключены компа раторов , элементов памяти, а также аналоговый инвертор и Uo повторитель. Число компараторов всего преобразователя определяется как . Это позволяет существенно повысить точность и надежность преобразования. Формула изобретения Параллельный аналого-цифровой преобразователь, содержащий группу компараторов младших разрядов, выходы которых, кроме компаратора старшего разряда, объединены попарно, первый и второй резистивные делитеЛИ, первые входы которых соединены соответственно со входной и общей шинами, а вторые входы подключены ко входам первого и второго источников тока смещения соответственно, а выходы попарно со сдвигом на один резистор подключены к первым и вторым входам элементов И первой группы, первые выходы которых через первый элемент ИЛИ соединены с первыми входами компараторов младших разрядов, отличающийся тем, что, с целью повышения точности и надежности , в него введены третий резистивный делитель, элементы И второй группы, второй элемент ИЛИ, источник напряжения смещения, третий источник тока и дешифратор, при этом первые входы элементов И второй группы со сдвигом на один резистор по отношению к первым входам элементов И первой группы подключены к выходам первого резистивного делителя, вторые входы элементов И второй группы подключены к выходам второго резистивного делителя в точках подключения вторых входов элементов И первой группы, первые выходы элементов И второй группы через первые входы второго элемента ИЛИ соединены с первым входом третьего резистивного де- . лителя, второй вход которого подключен к третьему источнику тока, а выходы подключены ко вторым входам компараторов млсщших разрядов, вторые выходы элементов И первой и второй групп, кроме последнего элемента И второй группы, подключены ко входам дешифратора, второй вход второго элемента ИЛИ соединен с выходом источника смещения. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2672785,кл. Н 03 К 13/175 (прототип).. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1019623A1 |

| Параллельный аналого-цифровой преобразователь | 1978 |

|

SU769731A1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1035795A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Параллельный аналого-цифровой преобразователь | 1977 |

|

SU934574A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1991 |

|

RU2019031C1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Параллельный аналого-цифровой преобразователь | 1989 |

|

SU1762409A2 |

Авторы

Даты

1981-09-30—Публикация

1980-01-25—Подача