j КреобразоЕштель по п.1. о т л и ч а ю и; и и с fi тем; что блок устранения нео июяначноотн кодз Bbmojufet; иа 1 элементах 21:|-ППИ 1П., первые входы которых объединены и являются первым входом блока устранения неоцнозначностр кода, выходы которого являются элементов 2Н-НЛИ-11Е, вторые входь KOTOpbix обп-,единень к являются пто-рым входом блока устраиенпя неод-нозначности кода, входы первой групгп 1 которого являются третьими входами соответствующих эле 5ентов 2H- J1H-HE; ):й вход второй груглп, ягзляется г5е-;вертым входом

193808

П-го элемента 2И-ИЛН- ;Е, ,гй 1 -и вход второй группы, где -i 2,jj,.,n-|,. яиляетоя четно ;vr:,e-i вход,э;ч cooTBeTCT;iy;i}ii(ej-o и вес к г|ред:иествую:цих элеме 1тов 211-И:Ц1-1ЕЕ, а 1-1 -и вход второй группы Я ляется пятьм входом всех П1ед111ествую 1их здеме1гто;з 2И-ИЛИ-ИК, при этом каж 1 -и вход червой i pynnb; блока ycTjiaiiesiH;: неодиоизачностп --пп; Д- 2, 3, . , .л-1 J является иестым входом всех предшествующих элементов 2Н-ИЛИ-НК,, а первый вход первой руппы являетс:я шестым хол,ом ка:-л7и)го последукхдсгс юроме п -Г/ -;лс мс;нта 2}:-ИЛИ-Hi: .

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Биполярный цифровой амплитудный анализатор | 1983 |

|

SU1208605A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Способ преобразования напряжения в код и устройство для его реализации | 1980 |

|

SU892706A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок компараторов, выполненный на п компараторах, первые входы которого объединены с первым входом дополнительного компаратора и являются входной шиной, источник опорньк напряжений, выходы которого соответственно подключены к второму входу дополнительного компаратора и вторым входам блока компараторов, и шифратор, отличающийся тем, что, с пелью порьпиения точности, в него введены цифровой ампли.тудный анализатор, блок устранения неоднозначности кода, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент задержки и коммутатор, управляющий вход которого объединен с входом старшего разряда первой группы информационных входов коммутатора и подключен к выходу дополнительного компаратора, выходы являются выходньми шинами младших разрядов, -информационные входы младших разрядов первой группы соединены с соответствуюси ми выходами шифратора, а информационные входы второй группы с соответствующими вькодалад .младших разрядов цифрового амплитудного анализатора, вход которого является в одной шиной, прямой выход старшего разряда объединен с первым входом блока устранения неоднозначности кода, входом источника , опорных напряжений, первым входом элемента ИСКЛЮЧА

Из(Н)/егсние отпооггся к вычнс.аительной и лзмерител;-.но15 технике и може-.- оыт.ь iicriOJibscniaiio в автомати3npoaaiiHb x информа:-:ион из--измерительных Ci5cтe ax,

лзооретения - iioBiiWieHne точности ,

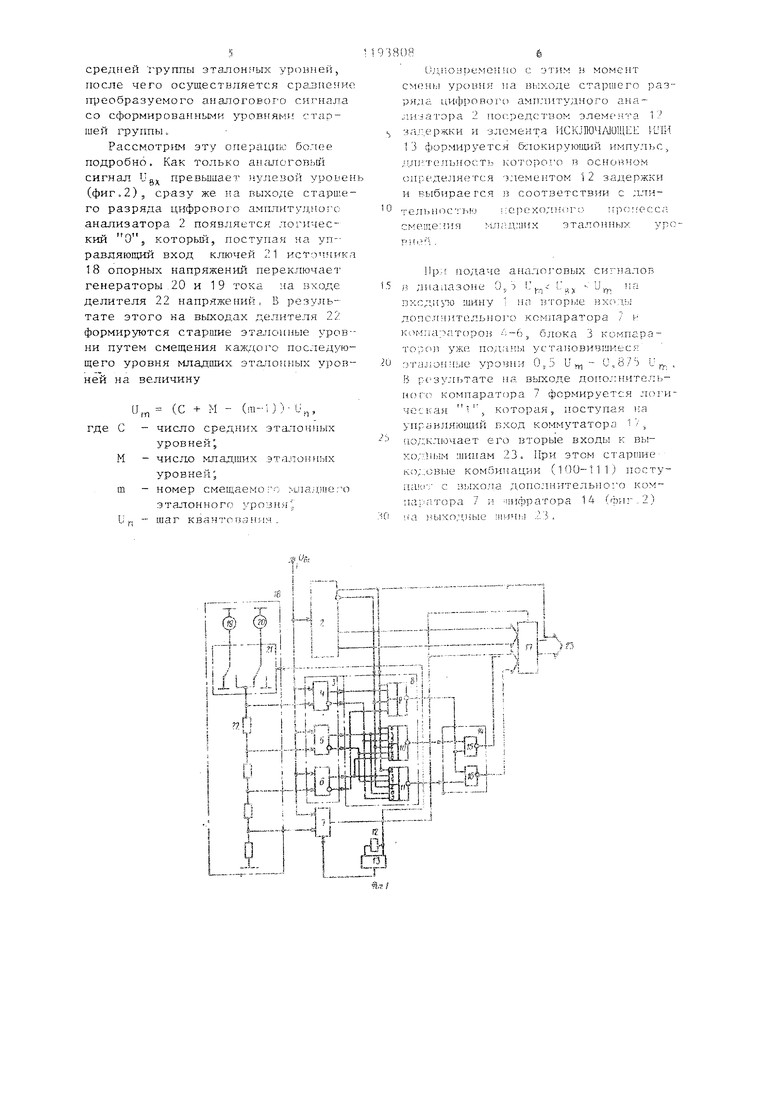

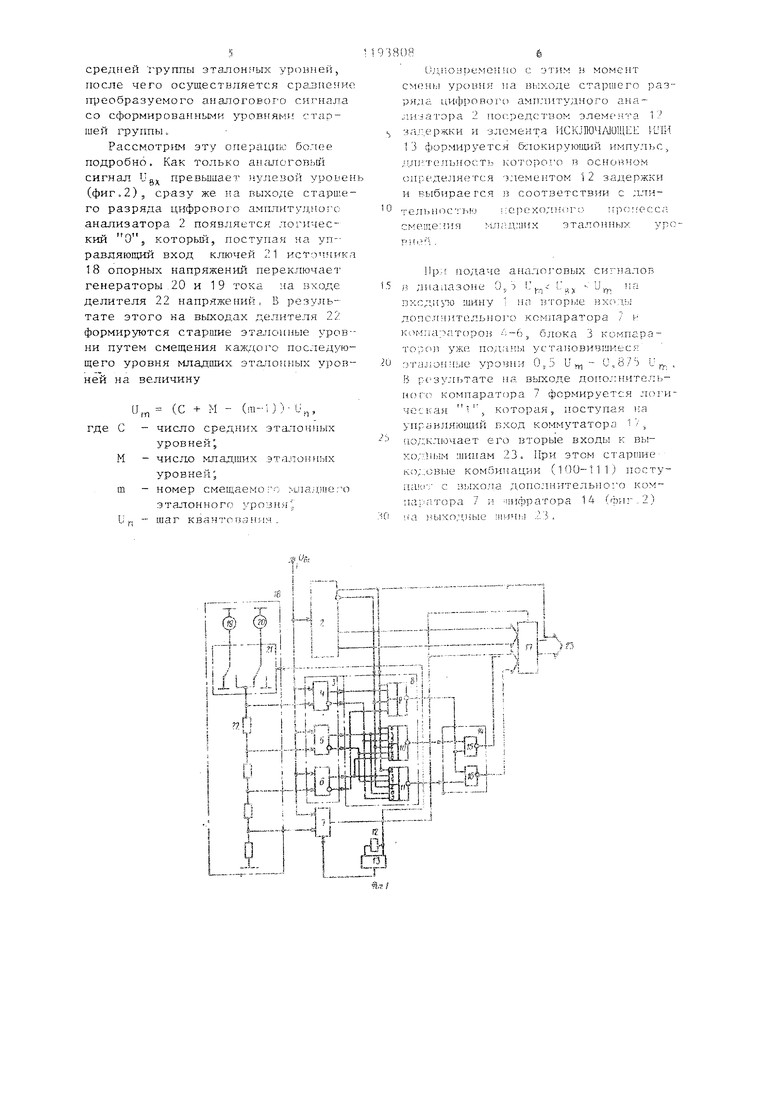

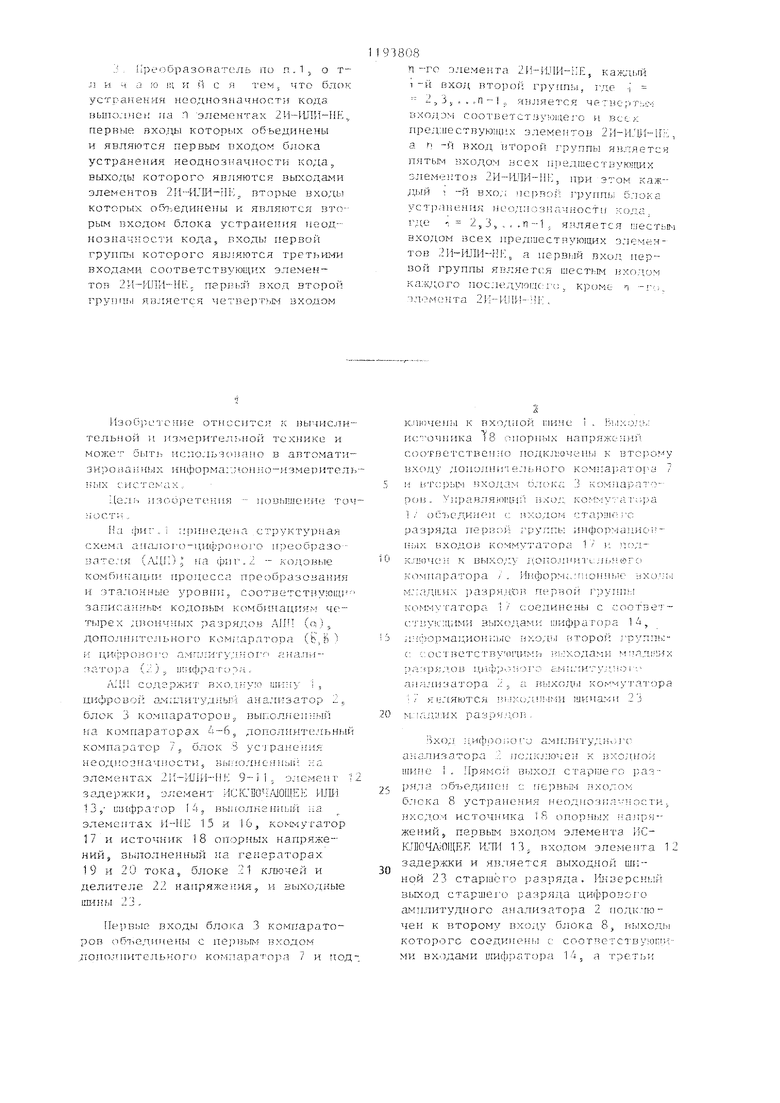

На (|)иг, 1;г)иве;,ена структурная схема апалтог(1-ци(рроного 1реобразовател (Л1{11) 5 на фпг.2 - кодовые комблкацли процесса, преобразования и 3Ta:io iHbie уровни, соответсткуящ)записа;П г-тм кодопы 1 комбилац -; четырех двоичн1 1х 1)азря;;(мз АИП (о), дополнительногс комгара1чтра (Ь,Ь )

и ЦИ(ЬрОВОГО аМГУ;ИТуД ;ОГГ1 f:Ha.nsi; ато1 а (/.)., liiHcbpaTOTa,

цифрово ; а:п;1литуд;1ыи анализатор ,, блок 3 компараторов 5 выполне1 ; ый на компараторах ii-b дополнительный компаратор / ,, блок S ycj ране;-:И.я неод 0зпапюст15, вь лод1 енный :а элементах 2И-Ш1И-11К 9-i 1 , элемент 1 згщержки, элемент ИСЛСПОЧЛЮШЕЕ ИШ 13,- шифратор 14, вы; олкениый ;;а элементах И--НЕ 15 и 16, комму гатор 17 и источн-ик 18 опорных напряжений, зьптолненный на генераторах 19 и 20 тока, блоке 21 ключей и делителе 22 напряжания, и зыход;гЬ е ШИ11Ы 23 ,

Первые входы бло)-са 3 компараторов обттединены с пej)зь тзходом доподн ггель -:огг.) KO niapaTop-a / и подKJTii/чепы к вхо/июи шине i . ,: ис:оч1И1ка f8 онорных напряжений соответственно лодкл очены к вто15ому входу ДОПОЛНИ e.:it:Horo компаратора / ; BTopbiM входам б:к)ка 3 комларат)ров. 1;) , KOM-- v;-a 1Ч;ра 1/ о1-П)едине с нходог-; старше Io разряда лерв;)й гру;:пь: инфо :-маиио ных входов коммутатора 1 . я n();iклочс;}; к выходу дfono4HirrL.Льнвгci

KO niapaTOiia / . И 1форма; ; он Н)е lixo;;: мла/ииих ;к13ряд тв первой соммх сатора I/ соединены с соответствунлцлми выходами пифрагора 14,

лч(;юрмад15онные входы второй j-pyrini,:с Соетветствуопи 51 И);;ходами М11ад )х pa3p};;i.oi 1.1,ифр.а5ОГО ь.мнлитудмо : ана:п1затора 2 , а въходы коммуТатора :7 Я ;:1яются iuviHa:.;n 23

м. ;ад;.1.их разрч.3,от5 .

Вход ;1ифро:;о1о амплитудн1ич анализатора 1 JIOд;CJ; oчeн к входной iiitHe 1 . Прямой старшего раз; ря;1а объединен с; nejJBhiM входом

8 устранения неодиозна- ости:, ,ом источн.-гка iB onopFihix налря-жений, первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, входом элемента 12 задержки и является выходной шиной 23 старшего разряда, Идзерсный выход ста ршего разряда цифрового амплитудного анализатора 2 подключен к второму вход,у блока 8, выход которого соединен, с соответствуюп Mii вх)дами тисрратора 1-4, а треты; и четвертые входы - с соответствую щими прямыми и инверсными выходами блока 3 компараторов. Выход элемента 12 задержки подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛ 13, выход которого соединен с трет им входом дополнительного компаратора 7. При этом вход источника 18 опор ных напряжений является входом блока 21 ключей, входы которого че рез соответствующие генераторы 19 и 20 тока подключены к общей шине, а выход через резисторный дели.тель 22 напряжения соединен также с шиной нулевого потенциала. Выходы делителя 22 напряжения являются выходами источника 18. Первые входы элементов 9-11 (на фиг.1 показан пример выполнения блока 8 на трех элементах 2И-ИЛИ-НЕ) объединены и являются первым входом блока 8, выходы кото рого являются выходами элементов 9-11, вторые входы которых объединены и являются вторым входом блока 8, входы третьей группы которог являются третьимивходами соответствующих элементов 9-11, первьм вход четвертой группы является четвертым входом элемента 9, второ вход четвертой группы является четвертым входом элементов 10 и 11 при этом третий вход четвертой гру пы является пятым входом элементов 10 и 11, второй вход третьей группы блока 8 является шестым входом элемента 11, а первый вход третьей группы - шестым входом элемента 10. АДП работает следующим образом. При подаче преобразуемого анало гового сигнала , -0,5 U где и - максимальная величина эталонного напряжения, на входную шину 1 он поступает на первые вход компараторов 4-6, блока 3 компарат ров и первый вход дополнительного компаратора 7, на вторые входы которых с выходов источника 18 опорных напряжений поступают младшие эталонные уровни в пределах -0,875 - 0,5 и (фиг.2) . В результате этого осуществляется срав нение преобразуемого аналогового сигнала с младшими эталонными уров нями, по результатам которого определяются младшие кодовые комбина 84 ции 111-100 (фиг.2В), которые формируются на выходе шифратора 14 после логического преобразования в блоке 8, где сформированный унитарньм код на выходе блока 3 компараторов преобразуется в позиционный код, при наличии уровня логического нуля на инверсном старшем разрядном выходе цифрового амплитудного анализатора 2, а следовательно, и на втором входе блока 8. На первый вход блока 8 со старшего разрядного выхода цифрового амплитудного анализатора 2 поступает уровень логической единицы, который проходит на выходную шину. Учитывая, что для этого интервала сигналов -и Ug, -0,5 U на выходе дополнительного компаратора 7 (фиг.25) присутствует логическая 1, на выход коммутатора 17 подаются кодовые комбинации с выхода шифратора 14 (фиг.If) и с выхода дополр ительного компаратора 7, логическая 1 на выходе которого в данном случае соответствует кодовым комбинациям разряда 2 АЦП. При подаче на вход аналоговых сигналов в диапазоне -0,375 11 ,1 и,5 Ufj осуществляется сравнение преобразуемого сигнала со средними эталонными уровнями, которые сформированы в цифровом амплитудном анализаторе 2. Полученные средние кодовые комбинации (1011OU11) поступают через первые входы коммутатора 17 (исключением старшего разряда) на выходны.е шины 23 ,П, так как в интервале 0,5 Um (фиг. 2) на выходе дополнительного компаратора 7 присутствует сигнал логического нуля, который подключает средние кодовые комбинации с выхода цифрового амплитудного анализатора 2 на выходные шины 23 АЦП. При этом для преобразуемых аналоговых сиг 1алов, пропорциональных кодовым комбинациям, которые превышают половину средних кодовых комбинаций (1000), формирование старшей группы эта юнных уровней осуществляется посредством смещения каждого последующего уровня группы младших эталонных уровней на величину Urn в момент времени, когда преобразуемый аналоговый сигнал превьш1ает средний эталонньш уровень

средней Труппы ЭТЗЛОНЕГЫХ yprjHuef, после чего осуществляется сралзиенке преобразуемого аналогового сигнала со сформированньми уровнями старшей группы.

Рассмотрим эту операцию бо.лее подробно. Как только аналоговьш сигнал Ug превьшает з-уленой уровен (фиг.2), ср-азу же i-a выходе старшего разряда цифропо1-о амплитудногч; анализатора 2 появляется логический О, который, поступая на уп-равляющий вход ключей 21 источника 18 опорных напряжений переключает генераторы 20 и 19 тока на входе делителя 22 напряжений, В 1 эзультате этого на выходах делителя 22 формируются старшие эта.г1оиные уров-ни путем смещения каж:;о о последующего уровня младших эта.лонных уровней на величину

М - (га-1 ) )

(J,

m - п

де

-число средних эталонных уровней;

М

-число млад,ших эталониь х уровней;

-номер смещае;чого Li aij;iue.o

m э тал о н ног о у р о у н и ,

V . шаг квантования .

938086

1Дповременно с этим н момент смены уровня на выходе старшего разряда L;n(ljpoBor4) амгтлитудного анали-атэра 2 посредством элемента 1 за-ержки и элемента НСЮЮЧЛЮЩ ;: :; ШШ 13 формируется блокирующий импульс д;т тельность которого в основном слг-еделяется элементом 12 задержки и выбирается соответствии с длительностью ;;ерехо;п-(го ггрсугесса смеи1е: 1я мп;;д:мих этало1П1ых урс

Пр;; подаче анало1овых сигналов в Д1 а;1азоне L Г,,. ь,., гр входиVTO шину 1 на вторые i xcvibi допстс-пггельного компаратора 7 и компараторов --Ь блока 3 компарато; о)1 уже подан)) установивииеся этал;о 5ные уровни 0„5 U ,т - С,В/) В результате на выходе допо.гн-ительвого компаратора 7 формируется л(5гическая которая, поступая на упранляющий вход коммутатора (1о/;кл1очает его вторые входы к выxo;:-:HjiM тинам 23. При этом старшие ко;.овые комби ации {100-111) постуiUlKi; с ДОПОЛНИТе ЛЫЮ ГО КОМпа :Птора 7 ;i чифратора 14 (Ьи- 2) иа ; ыход1;ые iiiJJHhi 23 ,

| Патент США № 3611350, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU651475A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-23—Публикация

1983-11-11—Подача