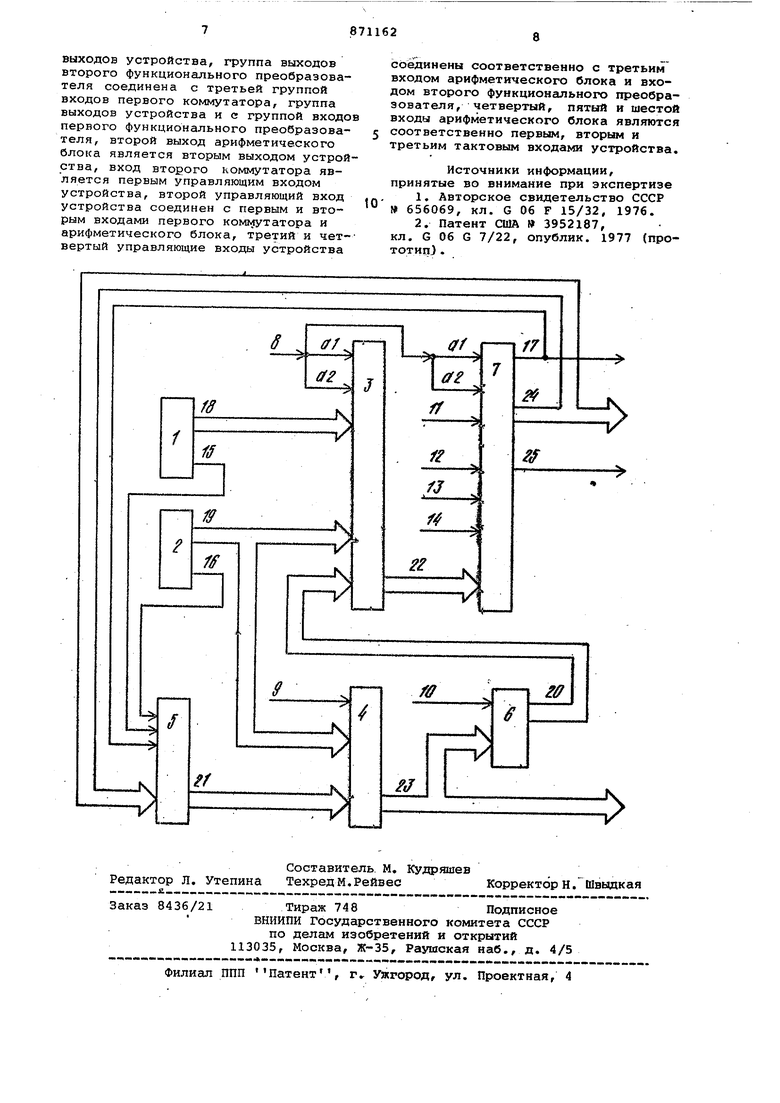

Изобретение относится к вычислит тельной технике и предназначено для вычисления по известным, кодам поляриых координат и измеряемой величины кодов ее прямоугольных координат X и у и наоборот. Известно устройство 11, функционирование которого связано с числоимпульсной обработкой информации. Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство для преобразования прямоугольных координат в полярные 12, содержащее регистры, коммутаторы, цифровой преобразователь, умножитель, сумматор и блок управления. Недостатком этих устройств являет ся низкое быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в цифровой преобразователь координат, содержащий два регистра, два коммутатора и первый функциональ ный преобразователь, введены второй функциональный преобразователь и арифметический блок. Группы разрядных выходов первого и второго регист ров соединены соответственно с перво и второй группами входов первого коммутатора. Группа выходов первого коммутатора соединена с группой входов арифметического блока. Вьсходы первого и второго регистров соединены соответственно с первым и;вторымвходами первого функционального преобразователя, третий вход которого соединен с первым выходом арифметического блока и с первым выходом устройства. Группа разрядных выходов второго регистра и группа выходов первого функционёшьного преобразователя соединены соответственно с пер.- вой и второй группами входов второго коммутатора. Группа выходов второго коммутатора соединена с группой входов второго функционального ире« образователя и с первой группой выходов устройства. Группа выходов второго функционального преобразователя соединена с третьей группой входов первого коммутатора. Группа выходов арифметического блока соединена с второй группой выходов устройства и с группой входов первого функционального преобразователя. Второй выход арифметического блоке является вторым выходом устройства, Вход второго коммутатора являетса первым управляющим входом устройства Второй управляющий вход устройства соединен с первым и вторым входами первого коммутатора и арифметического блока. Третий и четвертый управля ющие входы устройства соединены соот ветственно с третьим входом арифметического блока и входом второго функционального преобразователя. Четвертый, пятый и шестой входы ариф метического блока являются соответл стренно первым, вторым и третьим тактовыми входами устройства. Структурная схема устройства при . ведена на чертеже. Устройство содержит регистры 1, 2, коммутаторы 3, 4, функциональные преобразователи 5, б, арифметический блок 7, На чертеже обозначены управляющи входы 8-11 устройства, тактовые входы 12 - 14 устройства, выход 15 регистра 1, выход 16 регистра 2, выход 17 устройства, группа выходов 18 регистра 1, группа выходов 19 регистра 2, группа выходов 20 функционального преобразователя 6, груп па выходов 21 функционального преоб разователя 5, группа выходов 22 ком мУтатора 3, группа выходов 23 устро ства, группа выходов 24 устройства, выход 25 устройства. При выполнении вычислительной оп рации умножения и деления выполняют ся арифметическим блоком 7, вычисление по аргументу (углу Ц ) функци синуса или кооинуса - функциональным преобразователем 6, а вычислени по аргументу (tg М функции, (т.е. Угла ,Ф ) - функциональным преобразо вателем 5. Каждое из. вычислений выполняется за цикл по содержимому регистров 1, 2 по сигналам, вырабатываемым на выходах 17, 24 и 25 арифметического блока 7 (на выходе 17 вырабатывается информационный сигнал С17, а выходе 25 - управляющий сигнал ,П2.5 такой, что если арифметический. блок 7 занят вычислением, то , а если - свободен,, то ) и по входным управляющим и синхронизирую щим сигналам:сигналам.управляющего двухразряд кода .а и 2 (al и а2 | азрядные цифры кода) , поступающим с входов 8 на управляющие входы ком мутатора 3 и арифметического блока управляющим сигналам П9/ П10 И nil соответственно поступающим с входов 9, 10 и 11 на управляющие входа коммутатора 4,. функциональног преобразователя б и на управляющий вход арифметического блока 7; импульсу ИВ12 ввода, импульсу И313 запуска и тактовым импульсам , ТИ14 соответственно, поступающим с входов 12, 13 и 14 на соответствующ входы арифметического блока 7. В каждом цикле выполнения прямого преобразования или обратного преобразования можно выделить два временных такта, в каждом из которых в установившемся состоянии с выхода 15 и с выходов 18 регистра 1 снимается информационный сигнал С15 и код ФУНКЦИЙ Ф18, с выхода 16 и с выходов 19 регистра 2 - информационный сигнал С16 и код функции Ф19, с выходов 20 функционального преобразователя 6 - код функции Ф20, с выходов 21 функционального преобразователя 5 - код функции Ф21, с выходов 22 и 23 коммутаторов 3 и 4 - код функции Ф22 и код функции Ф23,с выхода 17, выходов 24 и выхода 25 арифметического блока 7 - информационный сигнал С17,. код функции Ф24 и выходной управляющий сигнал П25. При выполнении в преобразователе координат прямого преобразования и обратного преобразования есть некоторые аналогии. С связи с этим описание работы при выполнении прямого и обратного преобразований будем проводить по возможности парсшлельно, в круглых скобках информация, относящаяся к описанию работы при обратном преобразовании). Преобразователь координатпо jcoдам Ч и V (кодам X и V )за время каждого цикла прямого (обратного) преобразования осуществляет вычисление в первом такте кода X (кода V ), а во втором - кода V (кода Y) , Перед началом:некоторого очередного цикла прямого (обратного) преобразования арифметический блок 7 занят (вырабатывает сигнал ), в регистрах 1 и 2 .содержатся коды и Ф19 М (коды и вырабатываются сигналы С15 и ,.., на входы 8 поступает код 00, а на входа 9 и 10 сигналь и (сигналы и ). С помощью сигналов П9 функциональный преобразователь б вырабатывает код (код Ф20 при и ). с помощью кода к&ммутатор 3 выдает на арифметический блок 7 кол (код ). Цикл прямого (обратного) преобразования начинается в момент выработки арифметическим блоком 7 сигнеша , по которому на выходы 17 и 24 арифметического блока 7 вьщается результат вычисления. По сигналу код Ф24 снимается с арифметического блока 7, поступают сигнал (сигнал ) и первый импульс ИВ12. По сигналу () арифметический блок активизируется на выполнение операции умножения (деления) , а по первому ИВ 12 в память арифметического блока 7 заносится код Ф22 (код Ф22 X). После окончания первого ИВ12 на входы 8 подается код 10 (код ), на входах арифметического блока 7 устанавливается код Cos f (код V ) и на арифме тический блок 7 проходят второй ИВ и первый импульс запуска ИЗ13. По второму ИВ12 в память арифметическо го блок а заносится код Ф22 СозЧ (код Ф22). После окончания первог ИВ13 на вход 10 поступает сигнал ., на входы 8 - код 00 (код ОС17) преобразователь 6 занят вычислением кода по сигналу и коду (кода Ф20 по сигналам , ,С15 , и кодам Ф24, , а арифметический блок 7 запускается на выполнение операции умножения по кодам и Cos (операции деления по кодам X и V ) . Прсле окончания каждого ИЗ13 арифметический блок 7 выполняет (при ) операцию умножения за длительность времени -t v, (при . ) операцию деления за длительность времени t дел Помощью тактовых импульсов ТИ14. При выполнении прямого преобразования через время преобразования (.У. преобразователь 6 вырабатывает код Н, а через время .и.эрифметический блок 7 вырабатывает сигнал и код Ф24 СозЧ По сигналу с арифметическо го блока 7 снимается код , и начинается второй такт преобразсвания, который аналогичен первому такту, за исключением того, что во втором такте в памяти арифметическо го блока 7 заносятся коды V- и sin Поэтому в конце цикла прямого преобразования арифметический блок 7 вырабатывает сигнал и код Ф24 Sin. По данному сигналу производятся съем с арифметического блока 7 кода Ф24 V и запуск преобразователя координат для последующего цикла либо прямого, либо обратного преобразования. Если длительностью времени ввода информа ции в арифметический блок 7 пренебречь, то длительность Тц выполнения прямого преобразования можно оценить выражением В первом такте при выполнении обратного преобразования через время -fc дед арифметический блок 7 вырабатывает сигнал , код Ф24 (С-(4)и сигнал , где , k 1, если IXKIv/ Так Kak , ,, С1б(,, а входной управляющий код ОК, то через некоторое время после выполнения первой операции деления на входах арифметического, блока 7 устанавливается код Ф22 КЧ+К-У, преобразователь 5 вырабатывает код , коммутатор 4 - код . а преобразователь 6 - код +KSin4. После установления кодов на арифметический блок 7 Приходит третий ИВ12, после окончания которого На входы В Подается код 10,, на входах арифметического.блока 7 устанавливается код Ф22 Ф20 КСозЧ j-KSinf и поступает четвертый ИВ12 и второй ИВ13. По третьему и четвертому ИВ12 в арифметический блок 7 заносится код Ф22 КХ+к- ; и код Ф22 КСойЦ- KSinV а по второму импульсу ИЗ13 заканчивается первый такт и начинается второй такт обратного преобразователя; т.е. производится съем кода Ф23 -и запуск арифметического блока 7 на выполнение операции деления по коду (JCX+KV) и коду (KC(f+ + KsiM4). Поэтому в конце цикла обратного преобразования арифметический блок 7 вырабатывает сигнал и код N/М , Ф24 К со5Т lyuT По данному сигналу производится съем с арифметического блока 7 кода и запуск преобразователя координат для последующего цикла либо обратного, либо прямого преобразования. Применение изобретения позволяет повысить быстродействие устройства. Формула итобретения Цифровой преобразователь координат, содержащий два регистра, два коммутатора и первый функциональный преобразователь, отличающийс я тем, что, с целью повышения его быстродействия, он содержит второй функциональный преобразователь и арифметический блок, причем г-пуппы разрядных выходов первого и второго регистров соединены соответственно с первой и второй группами входов первого коммутатора, группа выходов . первого коммутатора соединена с группой входов арифметического блока, выходы первого и второго регистров соединены соответственно с первым и вторым входами первого функционального преобразователя, третий вход которого соединен с первым выходом арифметического блока и с первым выходом устройства, группа разрядных выходов второго регистра и группа выходов первого функционального преобразователя Соединены соответственно с первой и второй группами входов второго коммутатора, группа выходов второго коммутатора соединена с групой входов второго функционального реобразователя и с первой группой

выходов устройства, группа выходов второго функционального преобразователя соединена с третьей группой входов первого коммутатора, группа выходов устройства и с группой входо первого функционального преобразователя, второй выход арифметического блока является вторым выходом устройства, вход второго коммутатора является первым управляющим входом устройства, второй управляющий вход устройства соединен с первым и вторым входами первого коммутатора и арифметического блока, третий и четвертый управляющие входы устройства

сЬединены соответственно с третьим входом арифметического блока и входом второго функционального преобразователя, четвертый, пятый и шестой входы арифметического блока являются соответственно первым, вторым и третьим тактовым входами устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 656069, кл. G 06 F 15/32, 1976.

2.Патент США 3952187,

кл. G 06 G 7/22, опублик, 1977 (прототиоЗ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Генератор напряжений | 1982 |

|

SU1129718A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь полярных координат в прямоугольные координаты | 1987 |

|

SU1441390A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

Авторы

Даты

1981-10-07—Публикация

1980-01-28—Подача