также преобразования прямого кода аргумента в дополнительный и дополнительного в прямой код с обнаружением переполнения и его исправлением. Цель изобретения - повышение точности. Преобразователь содержит входы (2+п)- разрядного кода аргумента, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов ИЛИ, блок памяти т-разряд- ного кода синуса угла от О до (I-Z j к я/2 рад, где п - число адресных входов блока памяти, причем m 7 п, и первый блок элементов ИСКЛЮЧАЮЩЕЕ И.ПИ. Новым в преобразователе является то, что он содержит второй блок 6

1

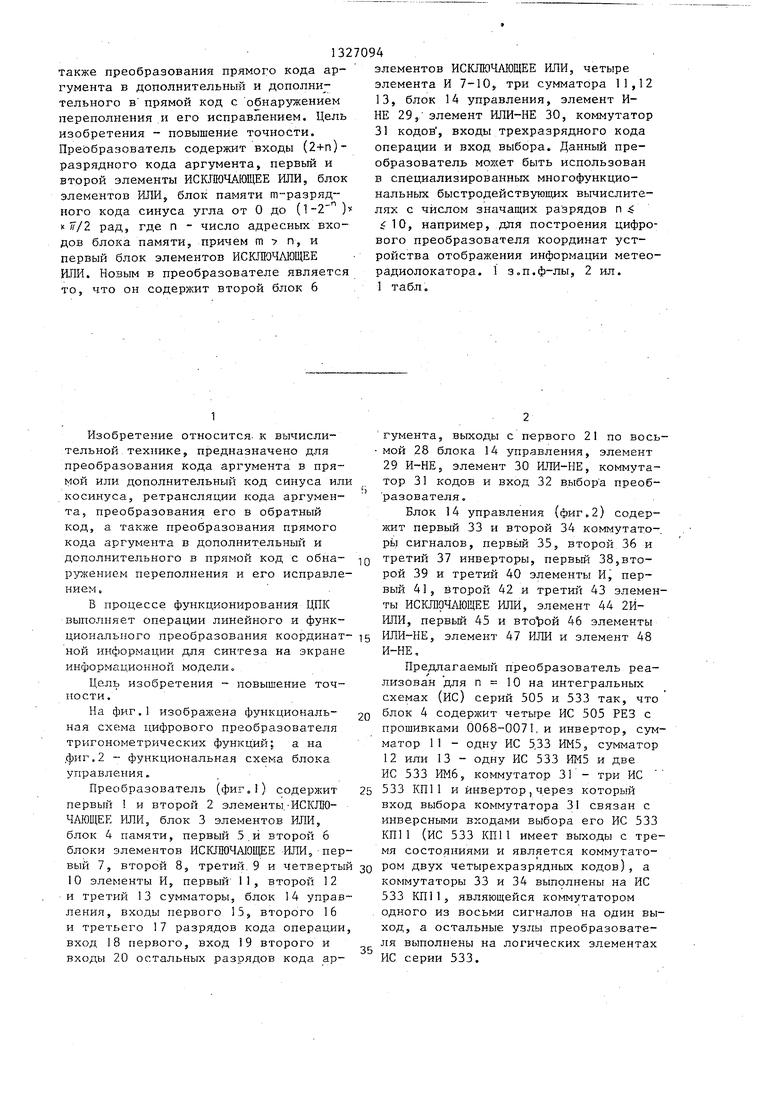

Изобретение относится, к вычислительной технике, предназначено для преобразования кода аргумента в прямой или дополнительный код синуса ил косинуса, ретрансляции кода аргумента, преобразования его в обратный коя, а также преобразования прямого кода аргумента в дополнительный и

дополнительного в прямой код с Обна-

ружением переполнения и его исправлением ,

В процессе функционирования ЦПК выполняет операции линейного и функционального преобразования координат ной информации для синтеза на экране информационной модели.

Цель изобретения - повышение точности.

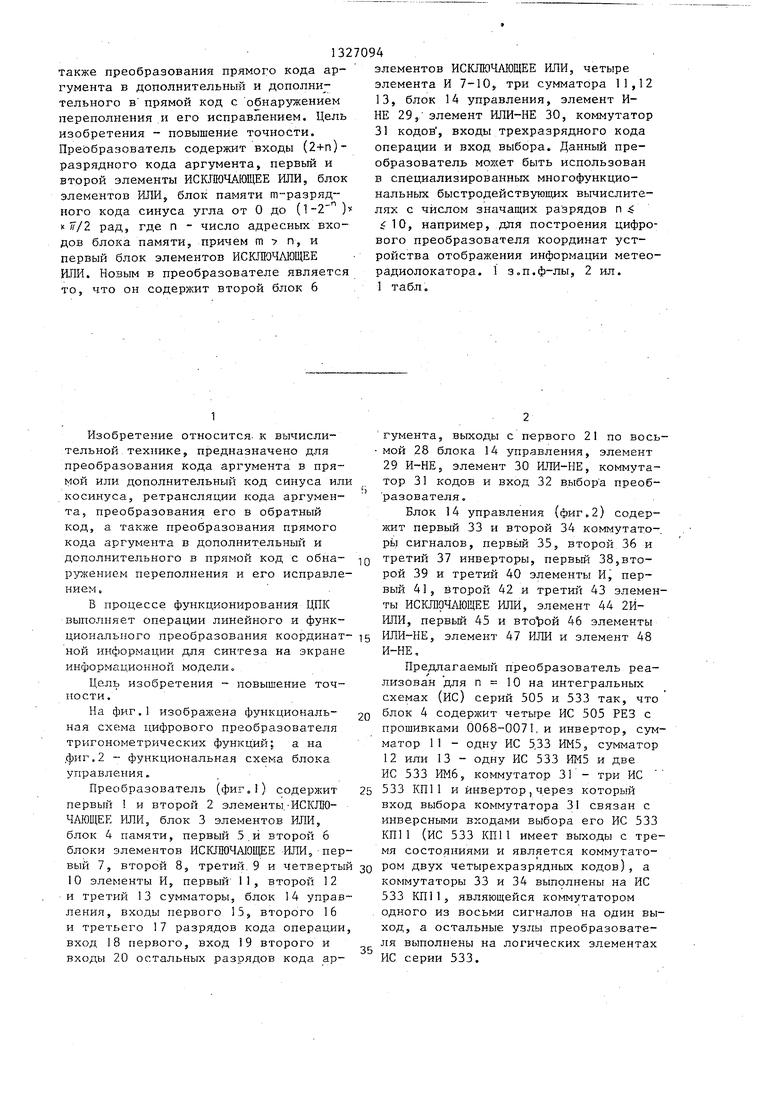

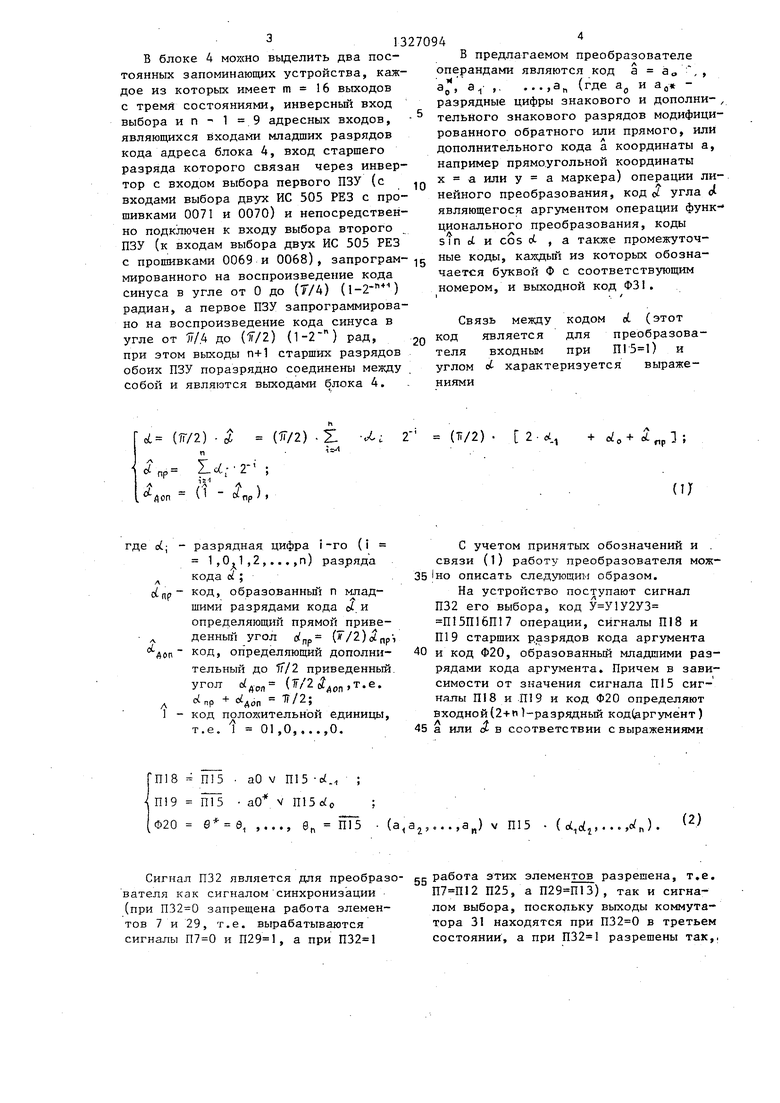

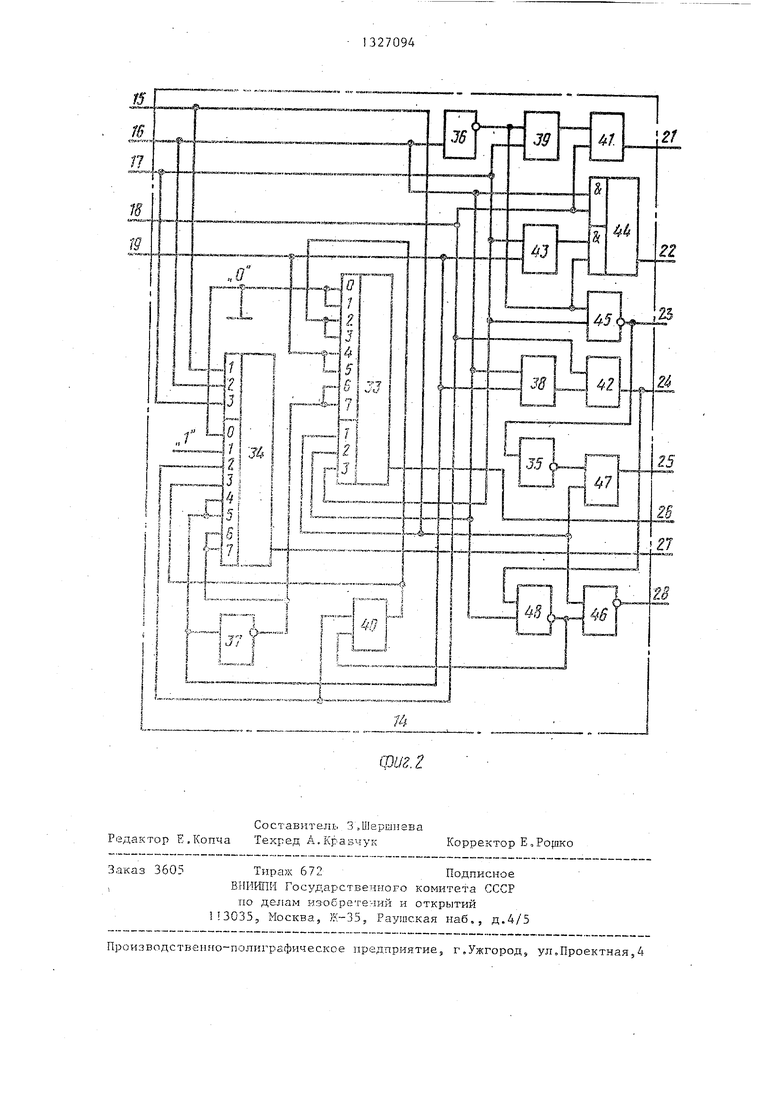

На фиг.1 изображена функциональ- ная схема цифрового преобразователя тригонометрических функций; а на .фиг.2 - функциональная схема блока управления.

Преобразователь (фиг.) содержит первый 1 и второй 2 элементы.-ИСКЛЮЧАЮЩЕЕ Щ1И, блок 3 элементов ИЛИ, блок 4 памяти, первый 5.и второй 6 блоки элементов ИСКЛЮЧАЮЩЕЕ ИЖ, первый 7, второй 8, третий.9 и четверты 10 элементы И, первый 11, второй 12 и третий 13 сумматоры, блок I4 управления, входы первого 1.5, второго 16 и третьего 17 разрядов кода операции вход 18 первого, вход 9 второго и входы 20 остальных разрядов кода арэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента И 7-10, три сумматора 11,12 13, блок 14 управления, элемент И- НЕ 295 элемент ИЛИ-НЕ 30, коммутатор 31 кодов , входы трехразрядного кода операции и вход выбора. Данный преобразователь может быть использован в специализированных многофункциональных быстродействующих вычислителях с числом значащих разрядов п 10, например, для построения цифрового преобразователя координат устройства отображения информации метеорадиолокатора. 1 з.п.ф-лы, 2 ил. 1 табл.

гумента, выходы с п-ервого 21 по восьмой .28 блока 14 управления, элемент 29 И-НЕ, элемент 30 ИЛИ-НЕ, коммутатор 31 кодов и вход 32 выбора преоб- разователя.

Блок 14 управления (фиг,2) содержит первый 33 и второй 34 коммутато-. ры сигналов, первьш 35, второй 36 и третий 37 инве1)торы, первый 38,второй 39 и третий 40 элементы И, первый 41, второй 42 и третий 43 элементы ИСКгаоЧАйЩЕЕ ИЛИ, элемент 44 2И- ИПИ, первый 45 и 46 элементы ИЛИ-НЕJ элемент 47 ИЛИ и элемент 48 И-НЕ.

Цредлагаемый преобразователь реализован для п 10 на интегральных схемах (ИС) серий 505 и 533 так, что блок 4 содержит четыре ИС 505 РЕЗ с прошивками 0068-0071, и инвертор, сумматор 11 - одну ИС 533 ИМ55 сумматор 12 или 13 - одну ИС 533 ИМ5 и две ИС 533 ИМб, коммутатор 31 - три ИС 533 КПП и инвертор , через который вход выбора коммутатора 31 связан с инверсными входами выбора его ИС 533 КПП (ИС 533 КПП имеет выходы с тремя состояниями и является коммутатором двух четырехразрядных кодов), а коммутаторы 33 и 34 выполнены на ИС 533 КП11, являющейся коммутатором одного из восьми сигналов на один выход, а остальные узлы преобразователя выполнены на логических элементах ИС серии 533.

В блоке 4 можно выделить два постоянных запоминаюпщх устройства, каждое из которых имеет m 16 выходов с тремя состояниями, инверсный вход выбора и п - 1 9 адресных входов, являющихся входами младших разрядов кода адреса блока 4, вход старшего разряда которого связан через инвертор с входом выбора первого ПЗУ (с Q входами выбора двух ИС 505 РЕЗ с про- шивками 0071 и 0070) и непосредственно подключен к входу выбора второго

В предлагаемом преобразователе операндами являются код а За , 3, ,, ...,а„ {где а, и а - разрядные цифры знакового и дополни тельного знакового разрядов модифиц рованного обратного или прямого, ил дополнительного кода а координаты а например прямоугольной координаты X а или у а маркера) операции л нейного преобразования, код о/ угла являющегося аргументом операции фун ционального преобразования, коды 51по1исо5о(. , а также промежуточномером, и выходной код Ф31.

ПЗУ (к входам выбора двух ИС 505 РЕЗ с прошивками 0069 и 0068), запрограм- д ные коды, каждьй из которых обозна мированного на воспроизведение кода чается буквой Ф с соответствующим синуса в угле от О до (Т/4) () радиан, а первое ПЗУ запрограммировано на воспроизведение кода синуса в угле от W4 до (f/2) (1-2) рад, при этом выходы п+1 старщих разрядов обоих ПЗУ поразрядно соединены между собой и являются выходами блока 4.

Связь между

кодом ot (этот является для преобразовавходным при ) и углом tf- характеризуется выражениями

20 код

теля

i(F/2)-ot (/2). 21 2- (fi/2) . 2-d 3.

n.л гЛ-,

пр Г2- ;

ЙСП

(1 - L.},

де o(j - разрядная цифра i -го (i

1,0д1,2,...,п) разряда кода d ;

код, образованньй п младшими разрядами кода ei. и определяющий прямой приве- денньш угол dnp ( «/2)nf код, определяющий дополнительный до 7Г/2 приведенный.

АОП

угол (f/2( ТГ/2;

дол

ci пр +

АОП

.Т.е.

1 - код пололштельной единицы, т.е. 1 01,0,,..,0.

П18 . аО v П15 -ci., ;

пТз аО V ;

Ф20 0 0, ,..., 0, ilTs . (,.,

Сигнал ИЗ2 является для преобразо-gg работа этих элементов разрешена, т.е.

вателя как сигналом синхронизацииП7 П12 П25, а ), так и сигна(при запрещена работа элемен-лом выбора, поскольку выходы коммутатов 7 и 29, т.е. вырабатываютсятора 31 находятся при в третьем

сигналы и , а при П32 1состоянии, а при разрешены так,.

В предлагаемом преобразователе операндами являются код а За , , 3, ,, ...,а„ {где а, и а - разрядные цифры знакового и дополни- тельного знакового разрядов модифицированного обратного или прямого, или дополнительного кода а координаты а, например прямоугольной координаты X а или у а маркера) операции линейного преобразования, код о/ угла о1 являющегося аргументом операции функционального преобразования, коды 51по1исо5о(. , а также промежуточные коды, каждьй из которых обозна чается буквой Ф с соответствующим

номером, и выходной код Ф31.

ные коды, каждьй из которых о чается буквой Ф с соответству

д ные коды, каждьй из которых обозна чается буквой Ф с соответствующим

Связь между

кодом ot (этот является для преобразовавходным при ) и углом tf- характеризуется выражениями

0 код

теля

(1J

(i

яда

лад. и риве- 2)nf олниенный.

.е.

ицы,

С учетом принятых обозначений и . связи (1) работу преобразователя мож35 но описать следующим образом.

На устройство поступают сигнал П32 его выбора, код У У1У2УЗ П15П16П17 операции, сигналы П18 и П19 старших разрядов кода аргумента

40 и код Ф20, образованный младиими разрядами кода аргумента. Причем в зависимости от значения сигнала сиг- налы П18 и П19 и код Ф20 определяют входной(2+п 1-разрядный код(дргумент)

45 а или i в соответствии с выражениями

.,aj V П15 - (otXi.-.-.o n)

(2)

51327094 6

что на них пропускается код при . блоков 3 и 5 и вырабатывается сигнал 0 с первого кодового входа, а при П12 переполнения сумматора 12. - с второго кодового входа ком- Такт преобразования начинается с мутатора 31.изменением сигнала П32 с О на 1,

Перед началом выполнения такта течение каждого такта остаются некаждой из восьми операций сигнала изменными как все сигналы на входах на вход преобразователя поданы преобразователя, так и коды ФЗ и Ф5, сигналы кода соответствующей опера- сигналы П8,П9,П12, сигналы, выраба- ции и соответствующего кода аргу- тываемые сумматором 11, и сигналы, мента (2), по которым устанавливают- JO вырабатываемые блоком 14 в соответ- ся сигналы кодов ФЗ и Ф5 на выходах ствии с выражениями:

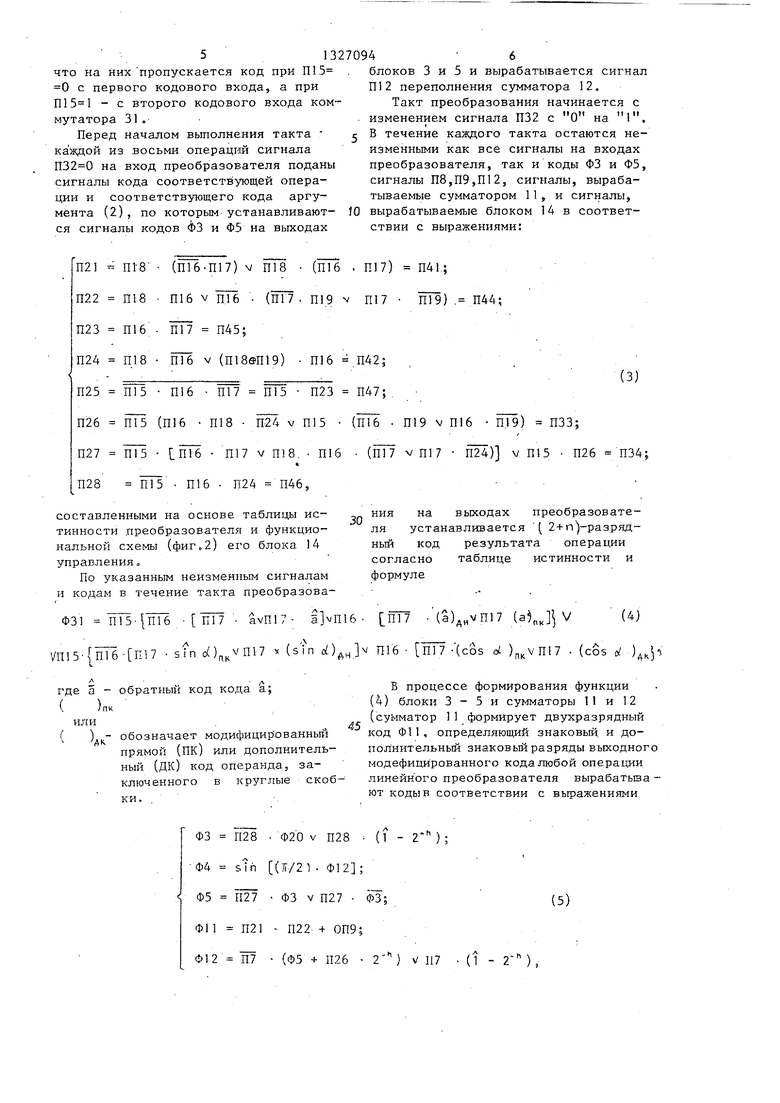

П2 - П1-8 (П16-П17) V П18 (П16 . П17) П41;

П22 П18 П16 V пТб . (пТ7 . v П17 IU9} . П44-,

П23 П16 . П17 П45;

П24 П18 пТб V (П18еП19) П16 .П42|

П25 П15 П16 П17 П15 П23 П47;

П26 П15 (П16 П18 П24 v П15 {П16 П19 v П16 ПГ9) ПЗЗ;

П27 П15 ГПб П17 V П18. П16 (П17 vni7 П24) v П15 - П26 П34; П28 1Ш . П16 - П24 П46,

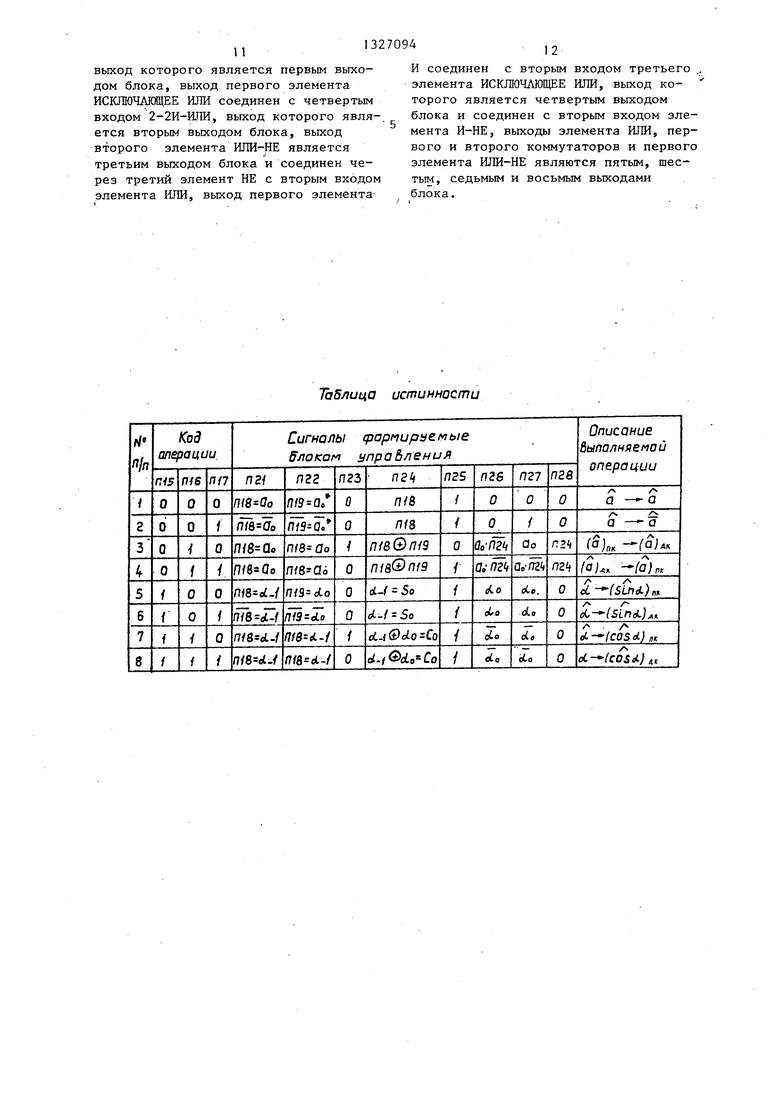

составленными на основе таблицы истинности .преобразователя и функциональной схемы (фиг.2) его блока 14 управления.

По указанным неизменным сигналам и кодам в течение такта преобразоваФ31 П17 - avni7- . П17 (а)д„УП17 ( V (4)

( sm с() х (sm d} ПГб ш7- (cos d ) - (cos i }/,

I

45

В процессе формирования функции (4) блоки 3 - 5 и сумматоры 11 и 12 (сумматор 11 формирует двухразрядный код Ф11, определяющий знаковый, и дополнительный знаковьй разряды выходного ный (ДК) код операнда, за- модефицированного кода любой операции ключенного в круглые скоб- линейного преобра.зователя вырабатьша- , коды в соответствии с вьфажениями

где а - обратный код кода а;

( ).к

или

( ) - обозначает модифицир ованный прямой (ПК) или дополнительФЗ П28 . Ф2 0 V П28 ( - 2 ) ; Ф4 sTn (Т/21 - Ф5 1127 ФЗ V П27 - ФЗ; Ф11 П21 - П22 + ОП9; П7 (Ф5 + 1126 - 2) V П7

(3)

30

ния на выходах преобразователя устанавливается 2+п)-разряд- ный код результата операции согласно таблице истинности и формуле

(5)

- 2- },

а элемент 1 (вырабатывает знаковый разряд) и сумматор. 13 (вырабатывает п значащих разрядов) с помощью сиг- налов П8 П17-П24, ШО П8-П13, П29 П13-П32 и .П29 и прямого при или обратного при кода Ф4 (этот код образован п+1 верным значащим разрядом кода синуса угла при угле О(ДРП ) вырабатывает

прямой или дополнительный код синуса (косинуса) с усечением и округлением до п значащих разрядов. Это позволяет выполнить операцию функционального преобразования с ошибкой , имеющей характеристики

о- П-1

(6)

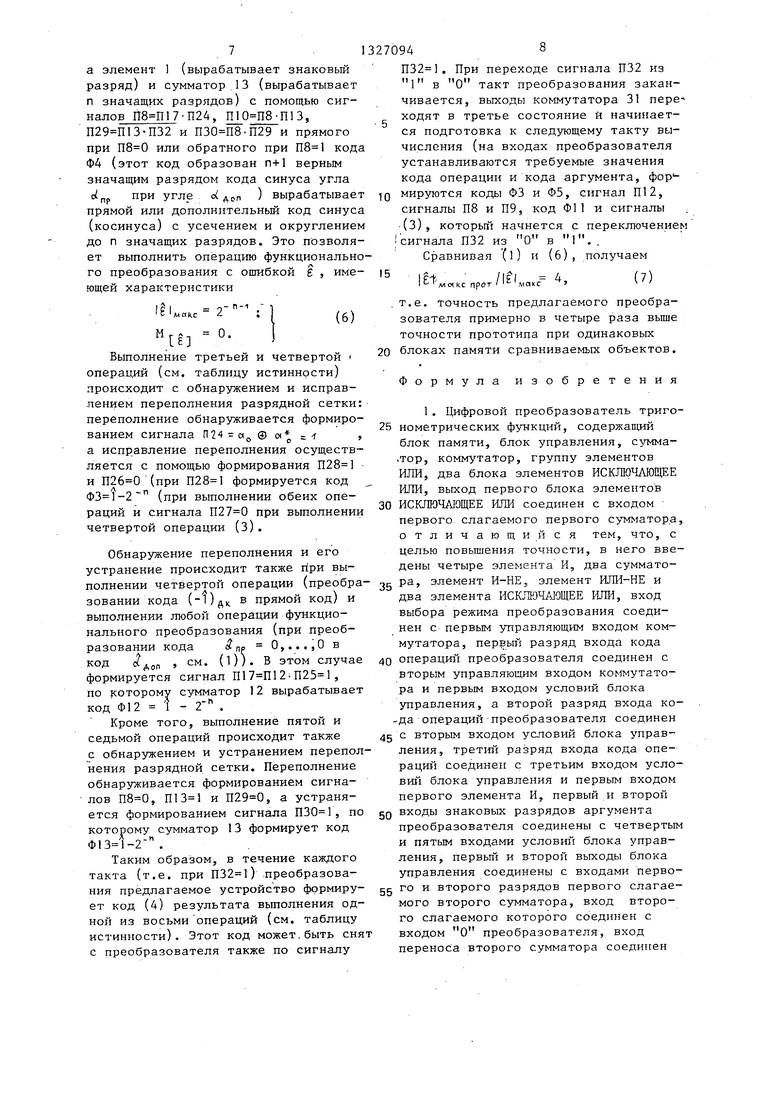

Выполнение третьей и четвертой i операций (см. таблицу истинности) происходит с обнаружением и исправлением переполнения разрядной сетки: переполнение обнаруживается формированием сигнала ® oi -г , а исправление переполнения осуществляется с помощью формирования и (при формируется код ФЗ 1-2 (при выполнении обеих операций и сигнала при выполнении четвертой операции (З).

Обнаружение переполнения и его устранение происходит также при вы20

Т.е. точность предлагаемого преобра зователя примерно в четыре раза выш точности прототипа при одинаковых блоках памяти сравниваемых объектов

Формула изобретени

1. Цифровой преобразователь триг 25 нометрических функций, содержащий блок памяти, блок управления, тop, коммутатор, группу элементов ИЛИ, два блока элементов ИСКЛЮЧАЮЩЕ ИЛИ, выход первого блока элементов 30 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом первого слагаемого первого сумматор отличающийся тем, что, целью повышения точности, в него вв дены четыре элемента И, два суммато

полнении четвертой операции (преобра- 35 элемент И-НЕ, элемент ИЛИ-НЕ и

зовании кода (-)дк в прямой код) и выполнении любой операции функционального преобразования (при преобразовании кода (пр - О,...,О в код (,р , см. (1)). В этом случае формируется сигнал П17 П12-П25 1, по которому сумматор 12 вырабатывает код Ф12 1 - 2 .

Кроме того, выполнение пятой и седьмой операций происходит также с обнаружением и устранением переполнения разрядной сетки. Переполнение обнаруживается формированием сигна- лов , и , а устраняется формированием сигнала , по которому сумматор 13 формирует код Ф1з4-2-.

Таким образом, в течение каждого такта (т.е. при ) .преобразования предлагаемое устройство формирует код (4) результата выполнения одной из восьми операций (см. таблицу истинности). Этот код может.быть снят с преобразователя также по сигналу

два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход выбора режима преобразования соединен с первым управляющим входом ком мутатора, первый разряд входа кода

40 операций преобразователя соединен с вторым управляющим входом коммутато ра и первым входом условий блока управления, а второй разряд входа к -да операций-преобразователя соедине

45 с вторым входом условий блока управ ления, третий разряд входа кода опе раций соединен с третьим входом усл вий блока управления и первым входо первого элемента И, первый и второй

50 входы знаковых разрядов аргумента

преобразователя соединены с четверт и пятым входами условий блока управ ления, первьш и второй выходы блока управления соединены с входами перв

55 го и второго разрядов первого слага мого второго сумматора, вход второ го слагаемого которого соединен с входом О преобразователя, вход переноса второго сумматора соеди ен

3270948

, При переходе сигнала IT32 из 1 в О такт преобразования заканчивается, выходы коммутатора 31 пере ходят в третье состояние и начинается подготовка к следующему такту вычисления (на входах преобразователя устанавливаются требуемые значения кода операции и кода аргумента, 1Q мируются коды ФЗ и Ф5, сигнал П12, сигналы П8 и П9, код Ф11 и сигналы (З), которьп начнется с переключением

iсигнала П32 из О в 1,.

Сравнивая (l) и (б), получаем

let,

5г 1 макс

(7)

MotKc прот

Т.е. точность предлагаемого преобразователя примерно в четыре раза выше точности прототипа при одинаковых блоках памяти сравниваемых объектов.

Формула изобретения

1. Цифровой преобразователь триго- 25 нометрических функций, содержащий блок памяти, блок управления, тop, коммутатор, группу элементов ИЛИ, два блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого блока элементов 30 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом первого слагаемого первого сумматора, отличающийся тем, что, с целью повышения точности, в него введены четыре элемента И, два суммато35 элемент И-НЕ, элемент ИЛИ-НЕ и

два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход выбора режима преобразования соединен с первым управляющим входом коммутатора, первый разряд входа кода

40 операций преобразователя соединен с вторым управляющим входом коммутатора и первым входом условий блока управления, а второй разряд входа ко -да операций-преобразователя соединен

45 с вторым входом условий блока управления, третий разряд входа кода операций соединен с третьим входом условий блока управления и первым входом первого элемента И, первый и второй

50 входы знаковых разрядов аргумента

преобразователя соединены с четверты и пятым входами условий блока управления, первьш и второй выходы блока управления соединены с входами перво55 го и второго разрядов первого слагаемого второго сумматора, вход второго слагаемого которого соединен с входом О преобразователя, вход переноса второго сумматора соеди ен

с выходом второго элемента И, первый вход которого соединен с третьим выходом блока управления, четвартый выход блока управления соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента Ид пятьй и шестой выходы блока управления соединены с первьп- входом третьего элемента И и входо переноса первого сумматора, седьмой и восьмой выходы блока управления соединены с первым входом первого блока элементов ИСКЛЮ ШОЩЕЕ ИЛИ и с первыми входами элементов liTOI группы соотзетст- венно, вторые входы которых образуют вход кода аргумента преобразователя, выходы элементов ЙШТ группы соединены с вторьм входом первого блока элементов ИСКЛЮ ЧАЮЩЕЕ ИЛИ; вход выбора режима преобразования преобразователя соединен с первым входом элемента и вторым входом третьего элемента И, выход которого соединен с входом второго слагаемого первого сз/мма-- тора 5-выход которого соединен с адресный входом блока naiv KTH и младшими разрядаг И первого информационного Бхода коммутатора, два старших разряда первого информационного входа которого соедикекы с въ ходок второго сумм;;;.гора5 иь ход -переполиенргя первого сумматора соединен с третьим входом третьего зламеита И и зторым входом л;торого эле.ента И вьтход первого элемента И соединен с: пер1;;ыми входами чатвсртого элемента Л., э.пс:мепта КЛК- НЕ. пторэго блока эл:::ментов ИСКЖгЧЛ- ЮЩЕЕ ПЛК к второго элемента ИСКЛЮЧАЮЩЕЕ ИШ1; вькод четвертого элемента И соединен с вторым зходом первого эле:-.1ента КСЮБОЧ,4гаЩЕЕ ИЛИ., выход кото- porcj соедине с двумя старшими раз- P)T,i ai iii ь торого ин4юрмацио1ьного входа ког-гму атора, вь ход элемента И-НЕ соединен с вторым входом элеме гга КЛй-НЕ 3 выход которо:: о соединен с в :эдом первого слагаемого третьего суммгггорар иы ход переполнения которо- ;го- соединен с вторыми входами четвпр- iToro элемента И и элемента И-НЕ , зк- ход cTapii. iix разрядов блока -памяти соединен с вторым входом второго- блока элементов ИСКЛОЧ ХВЗЦЕЕ ИПН, выход которого соединен с входом второго слагаемого третьего суьичатора, выход, младп1::го разряда блока памяти соеди- iiei с вторьм входом второго элемента ИС:КШ) -УШЦЕЕ ИЛ1-1, выход которого со.:.. третий вход н г первым .вхоединен с входом переноса третьгго сумматора, выход которого соединен с младшими разрядами информационного

входа коммутатора, выход которого является вьпсодом функции преобразователя.

2о Преобразователь по п,1, о т - л и ч а ю д и и с я reMj что блок управления содержит два коммутатора, три элемента НЕ, три элемента И, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 2-2И-ИЛИ, два элемента ИЛИ-НЕ, элемент ИЛИ, элемент И - НЕ, первый,

второй и третий входы условий блока соединены с первым, вторым и третьим управляющими входами первого и второго коммутаторов 5 первый, вход условий блока соединен с первьми входами

элемента ИЛИ и первого элемента ИЛИ- НЕ, второй вход условий блока соединен с первыми входами элемента 2И-- И-ПИ; первого элемента И, элемента И-НЕ и через первьгй элемент НЕ с

первыми входами второго элемента

И,, второго элемента ИЖ-НЕ и вторрлм

входом элемента 2--21 1--ИЛИ5

условий соединен

дом- первого элемента ИСКЯОЧ/ШДЕЕ ШШ

и вторыми входами .вторь х элементов И и ИЛИ-НЕ, четвертый вход условий блока соедипен с нервьми входами второго и третьего элементов ИСКЛ10Ч;Ш)ЩЕЕ ИЛИ, третьего элемента Ир третьим

информационным входом первого комму

татора,, третьим входом элемента 2-2И- Irilli-l, вход С блока соединен с первым информационны- входом первого коммутатора и первьгм и вторым информацион-кыми входами второго коммутатора, вход 1 блока соединен с вторым информационным входом первого коммутатора, выход элемента И-НЕ соединен с BToptjiM входом первого элемента ИИИПЕ и вторь;м входом третьего элемента Vi,j ззыход которого соединен с четвертым информационным входом первого л третьим и четвертым информацяонньп И входами вторО ГО коммутаторов, пять5Й

вход -условий блока соединен с вторьи;;;: входами первого элемента ИСКЛЮЧАЮ-- 1ДЕЕ ИЛИ, первого элемента PI, с пятым к шестым информационными входами первого и второго коммутаторов и через

второй элемент НЕ -- с седЫ &гм и восьмым и1 формагдионньБ-1и входами первого и второго коммутаторов, выход второго элемента И соединен с вторьш входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

выход которого является первым выходом блока, выход первого элемента ИСКЛЮЧЛЩЕЕ ИЛИ соединен с четвертым входом 2-2И-ШШ, выход которого явля-. ется вторым выходом блока, выход второго элемента ИЛИ-НЕ является третьим выходом блока и соединен через третий элемент НЕ с вторым входом элемента ИЛИ, выход первого элементаТаблица истинности

И соединен с вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход ко- торого является четвертым выходом блока и соединен с вторым входом элемента И-НЕ, выходы элемента ИЛИ, первого и второго коммутаторов и первого элемента ШЖ-НЕ являются пятым, шестым, седьмым и восьмым выходами блока.

Составител, З.Шершиава Редактор Е.Копча Техред А. Кравчук Корректор ЕоРощко

Заказ 3605 Тнраж 672Подписное

,ВНИИПИ Государственного комитета СССР

но делам из-обретений и открытий 1 13035,, Москва, Ж-ЗЗ, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

Фи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор напряжений | 1982 |

|

SU1129718A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Преобразователь полярных координат | 1990 |

|

SU1742817A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования кода аргумента в прямой или дополнительньй код синуса и косинуса, ретрансляции кода аргумента, преобразования его в обратный код, а (Л со ю со ij

| Синусно-косинусный преобразователь | 1981 |

|

SU1005040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-02-24—Подача