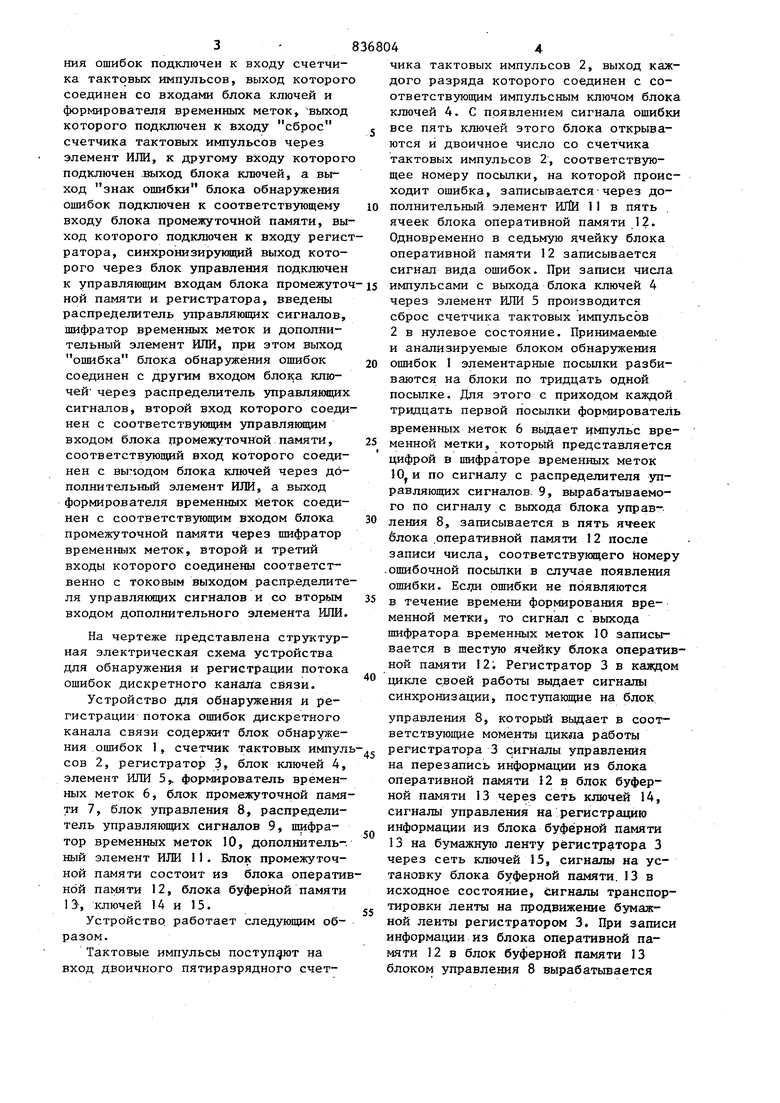

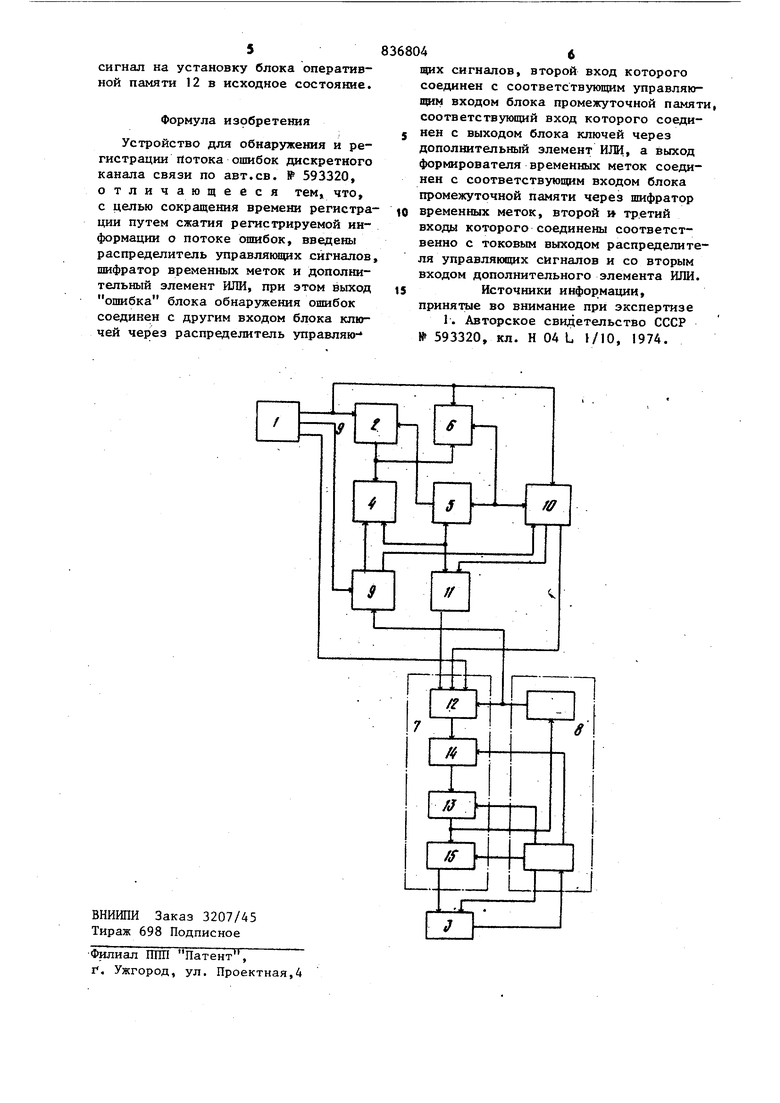

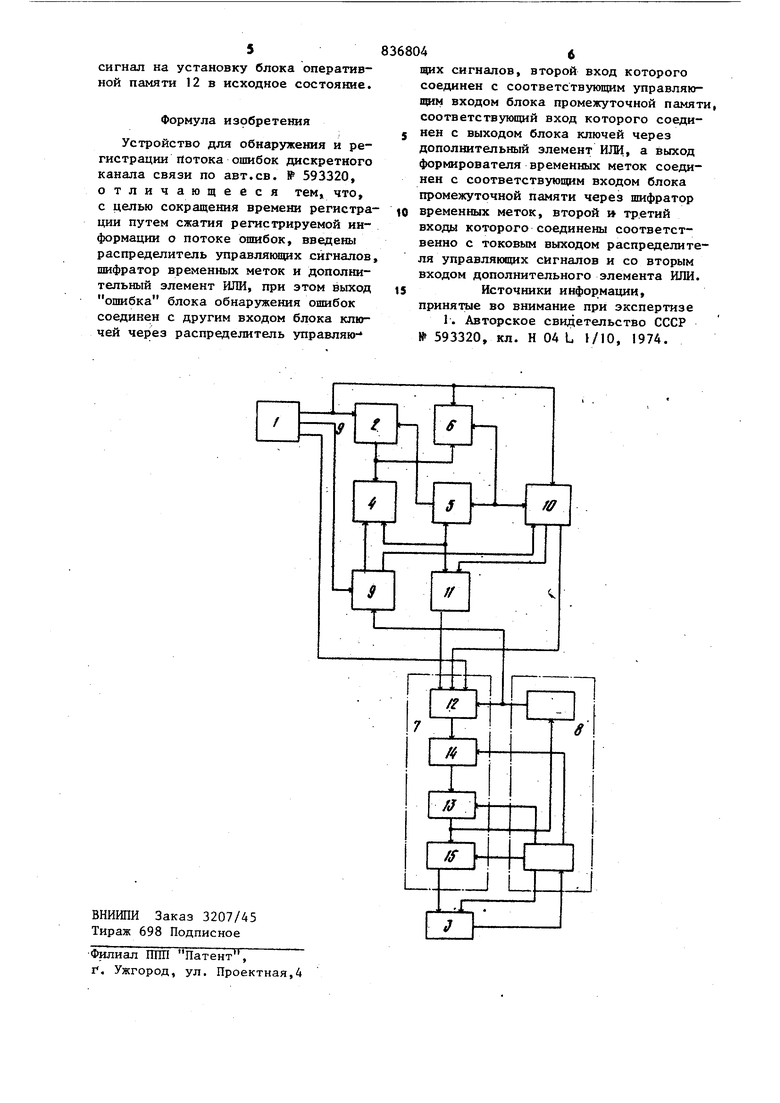

Изобретение относится к технике р диосвязи и может использоваться в аппаратуре для исследования дискретных каналов радиосвязи. По основному авт.св. № 593320 известно .устройство для обнаружения-и регистрации потока ошибок дискретного канала связи, содержащее на входе блок обнаружения ошибок, а также счетчик тактовых импульсов и регистратор, например перфоратор, бдок клю чей, элемент ИЛИ, формирователь временных меток, блок промежуточной памяти, блок управления, при этом тактовый выход блока обнаружения оши бок подключен к входу счетчика такто вых импульсов, выход которого соединен со входами блока ключей и формирователя временных меток, выход кото рого подключен к входу сброс счетчика тактовых импульсов через элемент ИЛИ, к другому входу которого подключен выход блока ключей, а выход знак ошибки блока обнаружения ошибок подключен к соответствующему входу блока промежуточной памяти, выход которого подключен к входу регистратора, синхронизирующий выход которого через блок управления подключен к управляницим входам блока промежуточной памяти и регистратора 1. Однако известное устройство не обеспечивает малого времени регистрации информации о потоке ошибок. Цель изобретения - сокращение времени регистрации путем сжатия регистрируемой информации о потоке ошибок. Для этого в устройство для обнаружения и регистрации потока ошибок дискретного канала связи, содержащее на входе блок обнаружения ошибок, а также сметчик тактовых импульсов и регистратор, например перфоратор, блок ключей, элемент ИЛИ, формирователь временных меток, блок промежуточной памяти, блок управления, при этом тактовый выход блока обнаружения ошибок подключен к входу счетчика тактовых импульсов, выход которог соединен со входами блока ключей и формирователя временных меток, выход которого подключен к входу сброс счетчика тактовых импульсов через элемент ИЛИ, к другому входу которог подключен выход блока ключей, а выход знак ошибки блока обнаружения ошибок подключен к соответствзпощему входу блока промежуточной памяти, вы ход которого подключен к входу регис ратора, синхронизирукнций выход которого через блок управления подключен к управляющим входам блока промежуто ной памяти и регистратора, введены распределитель управляющих сигналов, шифратор временных меток и дополнительный элемент ИЛИ, при этом выход ошибка блока обнаружения ошибок соединен с другим входом блока ключей- через распределитель управлянмцих сигналов, второй вход которого соеди нен с соответствуняцим управлянщим входом блока промежуточной памяти, соответствующий вход которого соединен с вьгюдом блока ключей через дополнительный элемент ИЛИ, а выход формирователя временных меток соединен с соответствуюащм входом блока промежуточной памяти через шифратор временных меток, второй и третий входы которого соединены соответственно с токовым выходом распределите ля управляквцих сигналов и со вторым входом дополнительного элемента ИЛИ. На чертеже представлена структурная электрическая схема устройства для обнаружения и регистрации потока ошибок дискретного канаЛа связи. Устройство для обнаружения и регистрации потока ошибок дискретного канала связи содержит блок обнаружения ошибок 1, счетчик тактовых импул сов 2, регистратор 3, блок ключей 4, элемент ИЛИ 5,, формирователь временных меток 6, блок промежуточной памя ти 7, блок управления 8, распределитель управляющих сигналов 9, шифратор временных меток 10, дополнительный элемент ИЛИ 11. Блок промежуточной памяти состоит из блока операти ной памяти 12, блока буферной памяти 1 Э-, ключей 14 и 15. Устройство, работает следующим образом. Тактовые импульсы поступают на вход двоичного пятиразрядного счетчика тактовых импульсов 2, выход каждого разряда которого соединен с соответствующим импульсным ключом блока ключей 4. С появлением сигнала ошибки все пять ключей этого блока открываются и двоичное число со счетчика тактовых импульсов 2, соответствующее номеру посылки, на которой происходит ошибка, записываетсячерез дополнительный элемент ШЙ 1 1 в пять ячеек блока оперативной памяти 12, Одновременно в седьмую ячейку блока оперативной памяти 12 записывается сигнал вида ошибок. При записи числа импульсами с выхода блока ключей 4 через элемент ИЛИ 5 производится сброс счетчика тактовых импульсов 2 в нулевое состояние. Принимаемые и анализируемые блоком обнаружения ошибок 1 элементарные посылки разбиваются на блоки по тридцать одной посьшке. Для этого с приходом каждой тридцать первой посылки форьшрователь временных меток 6 выдает 1|мпульс временной метки, которьй представляется цифрой в шифраторе временных меток по сигналу с распределителя управляющих сигналов. 9, вырабатываемого по сигналу с выхода блока управ-, ления 8, записывается в пять ячеек блока .оперативной памяти 12 после записи числа, соответствующего номеру ошибочной посьшки в случае появления ошибки, Есда ошибки не появляются в течение времени формирования временной метки, то сигнал с выхода шифратора временных меток 10 записывается в шестую ячейку блока оперативной памяти 12; Регистратор 3 в каядцом цикле рвоей работы выдает сигналы синхронизации, поступающие на блок управления 8, который вьщает в соответствующие моменты цикла работы регистратора 3 с.игналы управления на перезапись информации из блока оперативной памяти 52 в блок буферной памяти 13 через сеть ключей 14, сигналы управления на регистрацию информации из блока буферной памяти 13 на бумажную ленту регистратора 3 через сеть ключей 15, сигналы на установку блока буферной памяти. 13 в исходное состояние. Сигналы транспортировки ленты на продвижение бумажной ленты регистратором 3. При записи информации из блока оперативной памяти 12 в блок буферной памяти 13 блоком управления 8 вырабатьшается

сигнал на установку блока оперативной памяти 12 в исходное состояние.

Формула изобретения

Устройство для обнаружения и регистрации Потока ошибок дискретного канала связи по авт.св. № 593320, отличающееся тем что, с целью сокращения времени регистрации путем сжатия регистрируемой информации о потоке ошибок, введеш 1 распределитель управлякшц1х сигналов шифратор временных меток и дополнительный элемент ИЛИ, при этом выход ошибка блока обнаружения ошибок соединен с другим входом блока ключей через распределитель управляю-

368046

щих сигналов, второй вход которого соединен с соответствую1цим управляющим входом блока промежуточной памяти, соответствующий вход которого соедиJ нен с выходом блока ключей через дополнительный элемент ИЩ, а выход формирователя временных меток соединен с соответствующим входом блока промежуточной памяти через шифратор

fO временных меток, второй тр.етий входы которого соединены соответственно с токовым выходом распределителя управляющих сигналов и со вторым входом дополнительного элемента ИЛИ.

15 Источники информации,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР fr 593320, кл. Н 04 L J/10, I97A.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и регистрации потока ошибок дискретного канала связи | 1974 |

|

SU593320A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1980 |

|

SU974597A2 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА ПЕРЕДАЧИ И НАКОПЛЕНИЯ ИНФОРМАЦИИ | 1985 |

|

SU1378757A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1979 |

|

SU862375A1 |

| Устройство для передачи асинхронных сигналов | 1982 |

|

SU1075288A2 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Каротажная станция | 1988 |

|

SU1749867A1 |

| Регистрирующее устройство | 1988 |

|

SU1509595A1 |

| Устройство для регистрации параметров молоковыведения | 1982 |

|

SU1083981A1 |

Авторы

Даты

1981-06-07—Публикация

1979-06-19—Подача